抗电磁旁路攻击防护单元的性能分析

2010-12-27陈家文丁国良常小龙刘承智

陈家文,丁国良,常小龙,刘承智

抗电磁旁路攻击防护单元的性能分析

陈家文,丁国良,常小龙,刘承智

(军械工程学院计算机工程系,河北石家庄 050003)

基于半定制集成电路设计流程实现的抗电磁旁路攻击防护电路中,防护单元的性能决定了防护电路的性能。本文给出了评价防护单元所需的四个性能指标,同时结合集成电路设计工具给出了评估防护单元性能的实现流程。

集成电路;防护单元;性能指标

利用半定制集成电路设计流程实现具有抵抗旁路攻击能力的芯片已经成为防护电路设计的重要手段[1-2]。在半定制集成电路设计流程中,逻辑单元的性能和电路结构决定整个模块电路或芯片的性能。一旦完成了电路的结构设计以后,逻辑单元的性能是影响电路性能的主要因素。因此,需要在防护单元设计之初对其性能进行评估,以达到防护能力的要求。

评价集成电路逻辑单元性能指标通常包括:传播时延、版图面积和单元功耗等,评价防护单元的性能时,除了使用上述三种性能指标外还应包含逻辑单元的电磁信息泄漏程度的评估。

1 性能指标选择

(1)传播时延Tp

单元电路的传播时延反映了单元对输入信号变化的响应速度。它表示信号通过一个单元电路时所经历的时间,表示输入及对应的输出变换其峰值50%时的时间差。以缓冲器为例,由于对输入信号的上升和下降响应时间不同,可以引入两个子传播时延Tplh和Tphl。分别对应于输入信号由高到底和由低到高变化时门单元的传播时延,如图1所示,那么传播时延Tp就可以用这两个子时延的平均值来表示:

(2)版图面积S

单元的版图面积反映了模块电路或芯片的集成度,一般单元面积越小,电路集成度越高,得到的集成电路的面积越小。在密码芯片、智能卡等移动载体中,都希望芯片面积尽量小。因此,在设计防护单元时面积也是要考虑的一个十分重要的因素。

图1 时延的基本定义

(3)单元功耗P

功耗是电路设计的重要特性,决定了电路消耗多少能量以及电路消耗多少热量。这一因素将会影响到设计应该怎样选择电源容量、电池寿命、电源线尺寸、封装和冷却方法等。因此,设计防护电路时功耗性能参数是必须考虑的因素。

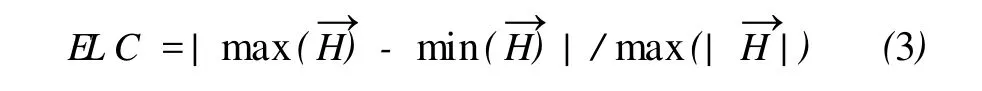

(4)电磁泄漏系数ELC

研究表明集成电路工艺达到0.18nm以后,基本单元电路的性能主要受输出负载电容的影响[3]。因此,可以利用输出负载线产生的电磁辐射分析防护单元的电磁泄漏程度。

首先,利用电偶极子模型可以计算得到输出负载线产生的近场磁场强度:

其中,→I是通过导线的电流,l输出导线长度, r是观测点距单元的距离,θ是观测点和输出导线的连线和单元电路所在平面的夹角。

双轨电路中输出导线有偶数条,其产生的磁场通过所有输出导线产生磁场叠加得到。以两条输出线为例,双轨电路的磁场强度为:

得到防护单元的磁场以后,利用电磁泄漏系数定义式分析防护单元的电磁信息泄漏情况,电磁泄漏系数ELC(Electromagnetic Leakage Coefficient):

电磁泄漏系数表示防护单元的输入信号不同时产生的电磁辐射差值的大小,反映了防护单元产生电磁信息泄漏程度,ELC值越大不同输入状态下电路产生电磁辐射的差值越大,电磁信息泄漏也越强。

2 电路性能仿真分析流程

图2给出了分析门电路性能参数仿真分析流程。主要步骤如下:

(1)版图面积测量,在完成版图设计以后通过游标即可测量出单元面积。

(2)传播时延是逻辑电路性能的一个重要的参数,Spectre仿真可得到所有输入输出信号的瞬态变化曲线,根据这些曲线可以测量得到每一个输出信号对各个输入信号变化的响应时间,即时延Tp。

(3)功耗仿真,功耗是一个十分值得测量的量。电源的瞬时功耗P(t)正比于电源电流idd(t)和电源电压V dd,即有下列关系式P(t)= idd(t)V dd。在一段时间t内消耗的功耗就是对瞬时功耗的积分:

首先测量电源电流随时间变化的曲线,对该曲线积分并乘以电源电压。比较不同逻辑电路之间的功耗大小时,需要在不同的逻辑电路上,在同样长的测量时间内,运行相同的运算。

(4)磁场仿真,磁场仿真与功耗仿真最大的区别是,前者需要得到门单元所有输出线上的电流,而不是电源电流。仿真得到输出线电流以后,通过公式转化为磁场并叠加,得到单元电路工作时产生的磁场辐射。

图2 门电路性能仿真分析流程

3 仿真实验建立

实验采用TSMC0.18μm 1.8/3.3V 196M混合信号BSIM 4.5 PDK实现了DDCVSL(Dynamic Differential Cascade Sw itch Logic)、SABL (Sense Amp lifier Based Logic)两种逻辑与非门,其中DDCVSL和SBAL是Tris提出的两种动态双轨防护逻辑[4-5]。如图3是SABL与非门的物理版图。

由于门电路的输出负载在实际电路中很难保证完全相等,因此测试电路中两个输出线上的负载电容分别取10f和12f,这样保证实验结果更加贴近实际情况,如图4所示。

图3 SABL与非门版图

图4 SABL与非门测试原理图

4 实验结果及分析

实验仿真得到SABL和DDCVSL逻辑与非门的性能参数,如表1所示。

注意在计算防护单元的ELC值时,为了计算方便,取输出端导线长度dl=1μm,距离观测点距离r=0.5cm,θ≈π/2,代入公式(2)可得,在观测点叠加后的磁场(A/m)。

表1 TSMC0.18工艺下两种与非门性能参数的比较

在电路时延方面,DDCVSL具有较小的时延效应,这主要是因为DDCVSL的下拉网络节点的导通回路上晶体管数量较少,从而导通回路上的电阻和寄生电容也较少,电容充放电时间短,电路时延较小。

在功耗方面,SABL与非门消耗的功耗明显高与DDCVSL与非门。SABL单元下拉网络在预充阶段会对所有的寄生电容充电,而求值阶段所有的寄生电容均会放电,因此消耗电源功耗较大。

从版图面积的角度看,DDCVSL与非门的面积小于 SABL与非门的面积。构建一个DDCVSL与非门至少需要11个MOS管,而构建一个SABL与非门则至少需要16个MOS管。

在电磁信息泄漏方面,SBAL与非门的电磁信息泄漏程度低于DDCVSL与非门,其防护性能较好。在求值阶段二者电磁泄漏系数相近,但在预充阶段SABL的电磁泄漏系数较小。由于与DDCVSL两个互补输出线相连的下拉网络具有不同的寄生电容和电阻,造成两个下拉网络结构不对称,因此,不同输入状态下两个互补输出线上形成的电流差别较大,进而导致了电路的电磁信息泄漏较强。

综上,与DDCVSL防护逻辑相比,SABL具有相对较小的电磁泄漏系数,防护性能较好。而SABL防护逻辑会导致更大的功耗、面积、时延。因此,在进行防护电路设计时必须综合考虑电路的防护能力和功耗、面积、时延等其它性能指标。

5 结论

文章给出了功耗、面积、时延和电磁泄漏系数(ELC)四个评价防护单元的性能指标,同时还给出了对防护单元性能进行评估的实现流程。实验结果表明,基于上述性能指标和评估流程,设计者能够较为准确地分析各种基本单元的性能,为设计防护逻辑和防护单元提供了有效的评估方法。

[1] HU IYUN L,MOORE S,MARKETTOS A T.A simulation methodology for electromagnetic analysis and testing on synchronous and asynchronous p rocessors[J].Croptology ePrint A rchive,2004,1-10.

[2] 童元满,王志英,戴葵,陆洪毅.不同设计层次下密码运算部件抗功耗攻击能力量化评估技术[J].计算机研究与发展. 2009,46(28):940-947.

[3] 石伟,戴葵,童元满,龚锐,王志英.防DPA攻击的两种不同逻辑比较研究[J].计算机工程与科学.2007.129(15):19 -22.

[4] TIRI K,A KMAL M,VERBAUWHEDE I.A dynamic and differential CMOS logic w ith signal independent power consump tion to withstand differential power analysis on smart cards[C].in Proc.Eur.Solid-State Circuits Conf.(ESSCIRC),Florence,Italy,2002,pp.403-406.

[5] TIRI K,VERBAUWHEDE I.A dynamic and differential CMOS logic style to resist power and timing attacks on security IC’s[C].IACR Cryptology ePrint A rchive,Santa Barbara,CA,Rep.2004/066,Feb.2004.

Performance analysis of defending logic cell against electromagnetic side channel attack

CHEN Jia-w en,DING Guo-liang,CHANG Xiao-long,LIU Cheng-zhi

(Department of Com puter Enginecring,Ordnance Engineering College,Shijiazhuang Hebei050003,China)

The performance of defending cell determined the perfo rmance of defending circuits imp lemented by the semi-customed design flow,w hich was used for fighting against electromagnetic side channel attack.Four perfo rmance indexes w ere given to evaluate defending cell,meanw hile,an evaluation flow was p roposed according to IC design tools.

Integrate Circuit(IC);Defending Cell(DC);Perfo rmance Index(PI)

TP273

:A

1001-9383(2010)04-0026-04

2010-08-15

陈家文(1961-),男,河北景县人,副教授,主要从事装备保障指挥自动化技术研究.