赛灵思静态随机存储器型FPGA单粒子翻转检测

2010-12-26吕达吴飞陆华

吕 达 吴 飞 陆 华

(航天恒星科技有限公司,北京 100086)

1 引言

太空环境下,赛灵思(XILINX)静态随机存储器(S RAM)型的现场可编程门阵列(FPGA)容易受到单粒子翻转(SEU)的影响。FPGA片内所有S RAM 都可能受到SEU 的影响,包括配置存储单元、用户逻辑单元、配置逻辑寄存器。配置存储单元的内容决定着FPGA的功能,配置存储单元发生翻转会导致FPGA功能持续改变,直至下次重新配置完成。用户逻辑单元包括块RAM(BRAM)以及可编程逻辑单元(CLB)、可编程IO 单元(IOB)中的触发器,这些存储单元的值在FPGA运行过程中实时刷新,所以SE U 影响不大。配置控制逻辑寄存器发生翻转属于单粒子功能中断(SEFI)的内容,会导致FPGA配置功能失效,但配置控制寄存器发生错误概率极低。据NASA测试数据显示,每70年才可能发生一次[1]。故配置存储单元SEU是FPGA抗SEU 设计中最重要的内容。

目前抗SEU 的措施包括通过一定厚度的材料进行辐射屏蔽、冗余设计、擦洗(Scrubbing)以及系统监控与重配置等。

冗余的方法包括采用多个完成相同功能的器件进行备份以及在同一器件中三模冗余容错技术(TM R)[2],冗余设计的假设前提是:任何两个存储单元的同一位不会在同一时间发生SEU 效应[3]。采用多个完成相同功能的器件备份可以提高可靠性,但会造成体积和功耗的增加;三模冗余设计可以带来可靠性的提高[4-5],但会使模块的速度降低、占用资源和功耗增加。

擦洗的方法是指周期性的刷新存储单元中的内容,可以减少受到SEU 而发生翻转的概率,这种方法的优点是无需额外的硬件逻辑资源,实现简单,其缺点是无法对擦洗数据进行校验,不能判断是否发生过SEU,而且只能恢复暂态故障[6]。同时,如果擦洗的时间间隔越大,可靠性就会降低[7]。

对配置存储器进行回读和重配置是一种有效的抵抗SEU 的方法,在FPGA实时运行过程中,回读配置存储器,并对读出的数据进行校验,如果发现错误则重新配置。目前NASA[8]、日本的智能卫星(SmartSat)[9]工作组都进行了基于这种结构的卫星信号处理平台的研究,国内国防科技大学[10]、航天恒星科技有限公司等单位也进行了这方面的研究,并取得了一定的进展。

本文以XILINX Virtex-II FPGAXC2V3000为例,分别通过内部访问接口(ICAP)和外部并行访问接口(SelectMap),回读配置数据并校验,实现了S EU 检测。另外,通过局部动态重构的方法,在地面环境实现了故障注入。

2 原理与方案

FPGA抗SEU 设计框图如图1所示,包括如下4个模块。

图1 FPGA抗SEU 设计方案Fig.1 Structure of SEU mitigation

1)目标模块:指被检测以及故障注入的实体。它们具备检测以及故障注入的接口。

2)监控模块:对被检测目标进行监控,对情况进行判断;在出现故障之后报告故障处理模块。

3)故障处理模块:检测出目标系统故障后,根据故障类型,进行相应的处理。可以是给出报错信息,也可能对错误予以纠正,也可能是既报错又给予纠正。

4)故障注入模块:在验证检测算法时使用,包括故障注入器和故障集。

故障注入器指对目标系统实施故障注入的实体。它根据故障注入模型条件,在故障注入时机到来的情况下,对目标系统进行故障注入。

故障集由实际发生在系统中的故障组成。故障集是通过对故障模型进行分析得到的集合。对于单粒子故障集来说,故障集包括了SEU、SEFI、单粒子锁定(SEL)等,其中SEU 故障集包括CLB 故障、IOB 故障、全局时钟(GCLK)故障以及BRAM Interconnect 故障等。

FPGA配置存储器SEU 检测可以通过ICAP和SelectMap 接口实现。通过ICAP 接口,FPGA可以在普通星载软件无线电平台实现对自身的SEU 检测。目标模块由两片XILINX FPGA实现,监控模块位于被监控FPGA内部,故障注入以及故障处理模块由被监控FPGA和DSP 模块完成,如图2所示。通过SelectMap 接口实现SEU 检测,需要在普通星载软件无线电平台基础上增加监控模块。目标模块是两片XILINX FPGA,监控模块由反镕丝FPGA,反镕丝FPGA通过SelectMap 接口回读SRAM 型FPGA的配置数据。故障注入以及故障处理模块由反镕丝FPGA和DSP 模块完成,如图3所示。

图2 通过ICAP 接口进行FPGASEU检测的硬件框架Fig.2 Detecting SEU for FPGAby ICAP

图3 通过SelectMap 接口进行检测的硬件框架Fig.3 Detecting SEU for FPGAby SelectMap

2.1 检测模块

对FPGA配置存储单元进行SEU 检测的办法是:目标FPGA在工作状态下,对其可配置单元中的内容进行回读(active readback),对配置数据进行校验。为了避免破坏BRAM 中的内容,只针对其他内容进行回读校验。

2.1.1 回读接口选择

Virtex II FPGA配置访问接口包括JTAG、SelectMap,以及ICAP 三种,其中ICAP是内部访问接口,监控模块在目标FPGA内部完成,通过ICAP接口访问配置存储器,可以实现对目标FPGA自身的检测,电路结构最为简单,不需要另加监控模块,但监控模块自身也有发生SEU 的可能,如图2所示。JTAG 和Selectmap 都是外部访问接口,外部设备通过这两个接口可以实现对目标FPGA进行回读,但Selectmap是并行接口,回读速度快,访问方便,如图3所示。本设计分别选择了ICAP 接口和SelectMap 接口进行回读检测。

2.1.2 检测周期确定

根据NASA和XILINX 一起对XILINX VirtexII 器件(XC2V1000)进行辐照测试获得的参数,见表1[11]。以XC2V1000配置存储器的3Mbit为例,根据该数据可知,平均每天就会发生1.3bit 的位翻转错误,发生 SEU 的最长时间为 18h,XC2V3000 的配置存储器大约为9M bit,估算得发生SE U 的最长时间约为6h。SEU 检测速率至少是故障概率的10倍,所以最长检测时间为0.6h。

如果回读检测模块工作时钟为10M Hz,通过SelectMap 接口,对XC2V3000 配置存储器进行回读检测,完成1次检测大约需要的时间是110ms,因此最短周期就是110ms。

根据以上考虑,文章选定1s 对配置存储器进行1次回读检测。

2.1.3 检测内容确定

S EU 检测的做法通常是对配置存储器的所有内容进行回读检测,但并不是所有回读数据都需要校验,如BRAM 中的内容。XILINX 提供了mask文件,表明了不需要校验的内容。但如果校验的时候使用mask 文件,需要占用存储空间,XC2V300器件mask 文件大约9.2M bit,对星载电子设备来说是一个很大的空间。文章将mask 文件嵌入到配置以及回读中去,回读数据可以直接和原始bit 文件进行校验或者进行C RC 校验,节省了存储空间。

2.2 故障注入模块

故障注入是模拟FPGA、SEU,以及单粒子功能中断等单粒子效应的一种有效方法。对FPGA进行S EU 模拟可以采用重离子辐射的方法,NASA的喷气推进实验室(JPL)和单粒子效应(SEE)协会对大规模集成电路的单粒子效应进行了很多模拟试验,利用各种模拟源(粒子加速器提供的各种重离子和质子、脉冲激光等)对FPGA进行辐照,使FPGA配置单元发生随机错误。在算法调试阶段,采用照射的方法会花费高额费用,另外也不利于实施。

利用Virtex II 系列FPGA可局部动态重构的特点。局部动态重构技术指对于特定的基于SRAM 结构的FPGA,在一定的控制逻辑的驱动下,对芯片的部分逻辑资源实现在系统的高速的功能变换。局部动态重构是指对重构器件或系统的一部分进行重新配置,而在此过程中,其余部分的工作状态不受影响。

XILINX Virtex II FPGA最小访问单元为1帧,因此对FPGA配置存储器每帧进行动态重构即可完成单粒子模拟。这种研究方法可以在很大程度上仿真地面单粒子模拟试验,缩短试验周期,提高试验的灵活性。基于FPGA配置文件的保密性要求,以及XILINX FPGA结构本身的保密性,XILINX对配置文件中每一帧具体的逻辑资源以及如何组织这部分信息是不公布的。每一帧配置数据不但包含对逻辑资源的配置,即某些位不允许故障注入,可以参考mask 文件对允许比较的位进行故障注入。

故障注入模块由三部分组成:故障模式寄存器、控制寄存器、故障发生器。故障模式寄存器和控制寄存器可以由处理器通过特权指令访问,可以很方便地设置故障模式,制造所期望的故障模式,并控制故障的注入。故障模式寄存器可以对FPGA的不同部位设置所期望的故障模式。如欲使CLB部分的第i 帧第j 位发生翻转,只要设置故障模式寄存器相应的数据位即可。控制寄存器可以控制故障的插入,再非调试模式下可以禁止故障的插入,保证被监控FPGA正常运行。在调试模式下,允许故障的插入,数据在经过故障注入器后,产生类似于SEU效应的错误数据,写入到配置存储器,达到故障注入的目的。

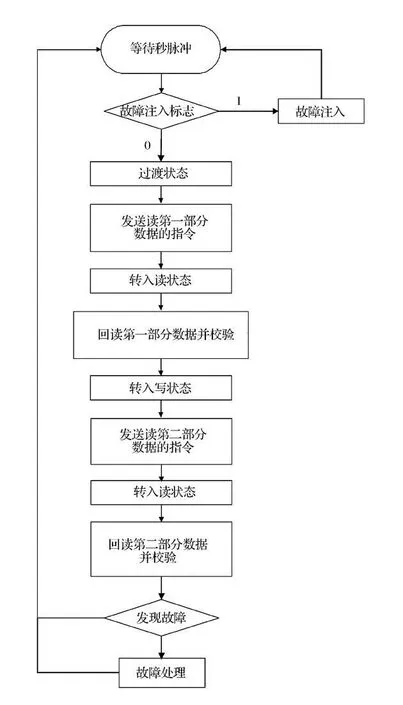

2.3 软件流程图

S EU 检测试验的软件流程如图4所示:秒脉冲下降沿到来时,检测故障注入标志,如果故障注入标志为1,则进行故障注入,即对配置存储器的一帧进行改写,否则对配置存储器进行检测。

图4 S EU 检测试验软件流程图Fig.4 SEU detection algorithm flow chart

3 试验结果及分析

3.1 SEU检测试验

3.1.1 通过ICAP 实现SEU 检测

FPGA对自身配置存储器进行检测结果如下:被监控FPGA实现点灯功能,未进行故障注入的时候,回读数据的CRC值保持恒定,如图5所示,CRC值始终是0xA2E2,检测结果compareout 信号也始终为低电平。

对配置存储器进行故障注入,配置存储器的Block Interconnect 列的第一帧的第一个字节进行改写,将最初的一个字节0×00 改为了0×07。故障注入后重新检测,回读数据的CRC值变为F00F,检测结果信号compareout 也变为高电平,表明检测到SEU 翻转,如图6所示。

图5 未故障注入时候CRC值始终不变Fig.5 CRC data are fixed w hen no SEU happens

图6 故障注入后CRC 发生变化Fig.6 CRC data are changed when SEU happens

3.1.2 通过SelectMap 接口实现SEU 检测

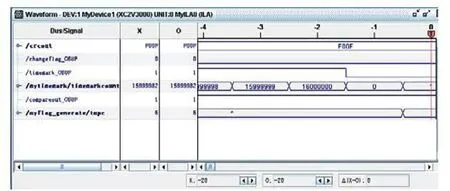

目标FPGA实现点灯功能。故障注入前始终未检测到SEU。故障注入是通过对GCLK 前两帧数据进行改写实现的。对配置存储器前两帧数据第一个字节分别写入0×0C,原来都是0×00;其余部分写入0×00。故障注入后小灯停止闪烁,开启回读检测模块,检测到SEU,如图7所示。

图7 故障注入后后检测到单粒子翻转Fig.7 S EU is detected after bug is inserted

图7中,从上至下第8个信号compare_o表示回读的配置数据与原始数据的比较结果,readnum表示回读比特计数。由图中看出当readnum=666时,compare_o为高电平,表示检测到了SEU。

3.2 资源使用情况

3.2.1 通过ICAP 实现SEU 检测

FPGA中实现的功能是通过ICAP 对自身配置存储器进行回读,并对读出的数据进行CRC 校验,所使用的资源如表2所示。

由表2可见,本文的FPGA抗SEU 设计占用资源少。本设计在星载GPS 接收机FPGA模块中进行了试验,FPGA设计在增加抗SEU 的功能的同时,不会造成资源的显著增加。

表2 FPGA通过ICAP 对自身配置存储器SEU 检测资源使用情况Table2 Resource using condition when detecting SEU in FPGAconfiguration memory through ICAP by itself

3.2.2 通过SelectMap 接口SE U 检测

本设计中选用Virtex II xc2v1500 代替反镕丝器件,对S RAM 型FPGA进行检测。监控FPGA内部实现监控模块、判决等功能,使用资源见表3。可见,通过SelectMap 接口实现SEU 检测占用资源很少。

表3 通过SelectMap 回读检测SEU 资源占用情况Table3 Resource using condition when detecting SEU in FPGAconfiguration memory through Seletcmap

4 结论及展望

文章分析了S RAM 型FPGASEU 的特点,以及FPGA抗SEU 方法,并通过对配置数据进行回读校验的方法实现了SEU 检测。

FPGA通过ICAP可以实现自身SE U 检测,但由于检测模块运行于FPGA内部,也可能发生SEU,可以通过对检测模块进行三模冗余设计提高可靠性,另外可以采用片外反镕丝器件通过Select-Map 接口对FPGA配置存储器进行回读,实施SEU 检测是更加可靠的办法。

References)

[1]Roosta R.AComparison of radiation-hard and radiation-tolerant FPGAs for space applications[R].NAS A,DEC,2004

[2]Carmichael C.Triple module redundancy design techniques for Virtex series FPGA[EB/OL].(2006-07-06).[2009-07-30]http://www.XILINX.com/hvdoes/apnotes/xapp197.pdf

[3]贺朝会,陈晓华,李国政.高能质子单粒子翻转效应的模拟计算[J].计算物理,2002,19(4):367-371

[4]Samudrala P K,Ramos J,Katkoori S.Selective triple modular redundancy (STMR)based single-event upset(S EU)tolerant synthesis for FPGAs[J].IEEE Transactions on Nuclear Science,2004,51(5)

[5]Fuller E,Caffrey M ,Salazar A,et al.Radiation testing update,SE U mitigation,and availability analysis of the Virtex FPGAfor space reconfigurable com puting[C]//4thAnnual Conference on Military and Aerospace Programmable Logic Devices(MAPLD).Washington DC:NASAOffice of Logic Design,September 2000

[6]Carmichael C,Fuller E,Blain E A.SEU mitigation techniques for Virtex FPGAs in space applications[C]// Proceeding of the Military and Aerospace Programmable Logic Devices and Technology Conference,1999

[7]Shubhendu S M,Emer J,Fossum T,et al.Cache scrubbing in microprocessors:mythor necessity [C]//PRDC' 04:10thIEEE Pacific Rim International Symposium on Dependable Computing.Tahiti,French Polynesia,2004

[8]Robert F,H odson1,Somervill K,et al.An architecture for reconfigurable computing in space[C]//Military and Aerospace Applications of Programmable Devices and Technologies Conference (MAPLD),Washington DC:NASAOffice of Logic Design,Sepetmber 2005

[9]Nishinaga N,Takeuchi M,Suzuki R.Reconfigurable communication equipment on smartSat-1[C].Military and Aerospace Applications of Programmable Devices and Technologies Conference (MAPLD),Washington DC:NASAOffice of Logic Design,September 2004

[10]邢克飞,杨俊,王跃科,等.XILINX SRAM 型FPGA抗辐射技术研究[J].宇航学报,2007,28(1)

[11]Yui C,Swif t G,Carmichael C.Single event upset susceptibility testing of the XILINX Virtex II FPGA[C]//Military and Aerospace Applications of Programmable Devices and Technologies Conference(MAPLD).Washington DC:NAS AOffice of Logic Design,September 2002