SAR目标模拟器硬件平台设计与实现

2010-09-27

(中国西南电子技术研究所,成都610036)

1 引 言

合成孔径雷达(SAR)已经广泛应用于矿产资源普查、地形测绘、森林覆盖统计和军事侦察中。通过SAR可以获得地面目标的高分辨率二维雷达图像,在军事上具有极高的使用价值[1]。SAR回波模拟器主要用于对SAR信号处理系统的功能验证与测试,而SAR目标回波信号往往是大时带宽积,因此,要求SAR目标模拟器产生信号必须是宽带、长持续时间信号,并且回波信号的出现时间要由外部主触发控制。因此,针对硬件平台就要求具有大数据存储容量和高模拟信号输出带宽能力。而普通雷达目标模拟设备因为输出信号带宽不够,或者因为没有大的数据存储容量导致目标回波信号时延不连续等原因,不适于产生SAR目标模拟信号[2]。

文献[1]与文献[2]都介绍了通过DDR存储数字回波数据,通过D/A转换生成模拟回波的方法。但两个文献中都使用DDR存储器,其数据读写速度不高;同时,从PC机向模拟器传输数字回波数据,通过USB接口进行,也存在着数据传输慢的问题。本文介绍的SAR目标模拟器,PC机通过CPCI总线将数字回波数据高速传输到目标模拟板DDRII存储器存储,可输出150 MHz带宽以上基带正交视频信号,与文献[1,2]介绍的硬件结构相比,该硬件结构具有更高数据吞吐速率特性。因此,该SAR目标模拟器硬件平台组成和关键技术对其它目标信号模拟器的设计也具有一定的借鉴价值。

2 硬件平台设计方案与关键元件介绍

2.1 SAR目标模拟器工作原理

该SAR目标模拟器由终端计算机和硬件平台两大部分组成。终端计算机产生目标回波数据,通过SAR目标模拟器硬件平台输出模拟SAR回波信号。首先在终端计算机显控界面下手动设置或导入雷达工作参数,通过仿真产生数字回波数据,并将数据以文件形式存储于计算机。当数据产生完成后,由显控将数字回波通过CPCI总线加载到硬件平台高速大容量DDRII存储器中。硬件平台根据显控指令,读取对应通道DDRII中存储的数据,将数据送到D/A,产生模拟回波信号。本系统支持单通道,或3个通道同时信号输出,因此可以提供条带、扫描、聚束SAR多种工作模式下回波模拟。该目标模拟器可以模拟带宽150 MHz以上、3 s时长的SAR目标回波信号。

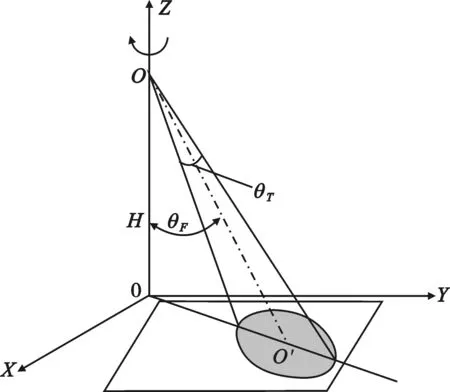

图2 辐射计天线波束与目标交会示意图Fig.2 Schematic diagram of the intersection of antenna beam and target

图1 SAR目标模拟器工作原理图Fig.1 Operating principle of SAR target simulator

2.2 SAR目标模拟器硬件平台组成

该平台主要由1片FPGA、六路D/A、3组大容量DDRII SDRAM、CPCI接口芯片PLX9656以及时钟和电源电路构成,硬件组成框图如图2所示。

由图2可以看出,FPGA为整个硬件平台核心,硬件平台工作控制全部由FPGA解析显控指令实现。

图2 SAR目标模拟器硬件平台框图Fig.2 Block diagram of hardware platform for SAR target simulator

2.3 关键器件选择

2.3.1PLX9656

PLX9656是PLX公司推出的高性能CPCI总线接口芯片,该芯片可提供64/32位CPCI总线接口[3]。

其主要特点如下:

(1)符合PCIV2.2协议,支持64位、66 MHz时钟PCI总线;

(2)采用PLX数据流水线架构(Data Pipe Architecture)技术,配有DMA引擎、可编程直接主控或者直接从属数据传输模式以及PCI信息传输功能;

(3)可以由2个局部总线中断信号LINTi和LINTo生成一个PCI中断信号INTA;

(4)允许Local端本地总线独立于PCI时钟工作;

(5)可直接生成所有控制、地址和数据信号以驱动CPCI总线,不需要额外驱动电路;

(6)可通过消息管理系统提供邮箱寄存器和门铃寄存器[4]。

2.3.2DDRII存储器

DDRII(Dual Data Rate SDRAM),其含义就是“第二代双倍速率SDRAM”[5]。DDR在时钟上升和下降沿各传输一次数据,使其数据传输速率为传统SDRAM的2倍。而DDRII相对于DDR的最大区别就是采用4 bit预取,因此其预读数据的能力是DDR的2倍。DDRII依靠控制器提供的差分时钟(CK和CK#)运行。双向数据选通信号(DQS)与数据一同发送,以便在接收端进行数据捕获[6]。

3 FPGA核心控制模块设计

FPGA为整个硬件平台核心,它通过CPCI总线与终端机进行指令和数据交换,通过控制DDRII数据读取,控制模拟回波信号输出。当显控向硬件平台写回波数据时,FPGA首先通过CPCI接口芯片9656本地总线接收终端发出指令,并根据指令启动对应通道DDRII存储控制器,将DDRII存储控制器转入写状态,随后将终端发出数字回波数据存储到对应通道DDRII存储器中。

数据传输完成后,根据终端发出相应通道信号输出指令,FPGA内DDRII存储控制器读取相应通道DDRII存储器数据,并将数据送给D/A,经数模变换后输出两路正交基带信号。整个硬件平台控制全部由FPGA完成,因此FPGA内部集成了3个DDRII控制模块和1个CPCI接口控制模块。

3.1 DDRII控制模块

DDRII控制模块非常复杂,包括时钟产生子模块、延迟控制子模块、读写控制子模块、物理层子模块和用户层子模块[6]。

图3 DDRII控制器控制流程图Fig.3 Control flow chart of DDRII controller

DDRII控制模块控制相应通道DDRII的数据存储与读取,为了提高读写效率,系统采用突发读写方式进行,突发读写长度设为8,DDRII控制模块的控制机制如图3所示。

系统上电时,DDRII控制模块首先完成对DDRII存储器初始化,初始化完成后控制器进入空闲等待状态。当终端机发出写指令时,控制模块转入写数据状态。由于向DDRII写数据速度比CPCI总线传输速度高一个数量级,因此要在PLX9656与DDRII控制模块之间放置一个双口RAM,进行数据传输缓冲。

当双口RAM接收终端计算机发出数据并达到缓存半满状态时,FPGA启动一次DDRII的突发写操作,将双口RAM数据写入DDRII存储器中。当双口RAM数据读取完毕时,DDRII控制模块转入等待双口RAM进入下一次缓存半满,双口RAM再次半满时又发起一次DDRII突发写。如此循环往复,直到终端发出本次写数据完毕,DDRII控制模块又转入空闲等待状态,等待终端发出新指令。

当终端发出输出正交基带信号命令时,DDRII控制模块首先记录主控机发出读取起始地址与读取长度,然后发起一次DDRII突发读数,将DDRII输出数据缓存到双口RAM中,当双口RAM写满,并且外部主触发信号到达时,启动一次双口RAM向D/A送数。当双口RAM数据读取完毕后,再启动一次DDRII突发读数,再次写满双口RAM,下一个主触发信号到来时,将双口RAM数据又送往D/A。如此循环往复,重复以上操作。当收到停止读指令时,控制模块转入空闲等待状态,停止D/A输出信号,等待终端计算机发出新指令。

DDRII控制有严格的时序要求,时序上配合稍微失误就会出现异常数据。DDRII读写控制与FPGA内双口RAM的配合也是一个难点。笔者在设计中就遇到过由于DDRII控制器写数据速度过快,超过了CPCI写双口RAM速度,导致每个主触发输出回波信号末尾有异常数据,通过调整双口RAM写半满信号输出时间,问题得到解决。建议设计初期多做仿真进行验证,调试过程中通过ISE自带工具Chipscope在线逻辑分析仪,采集数据来辅助进行时序和功能验证。

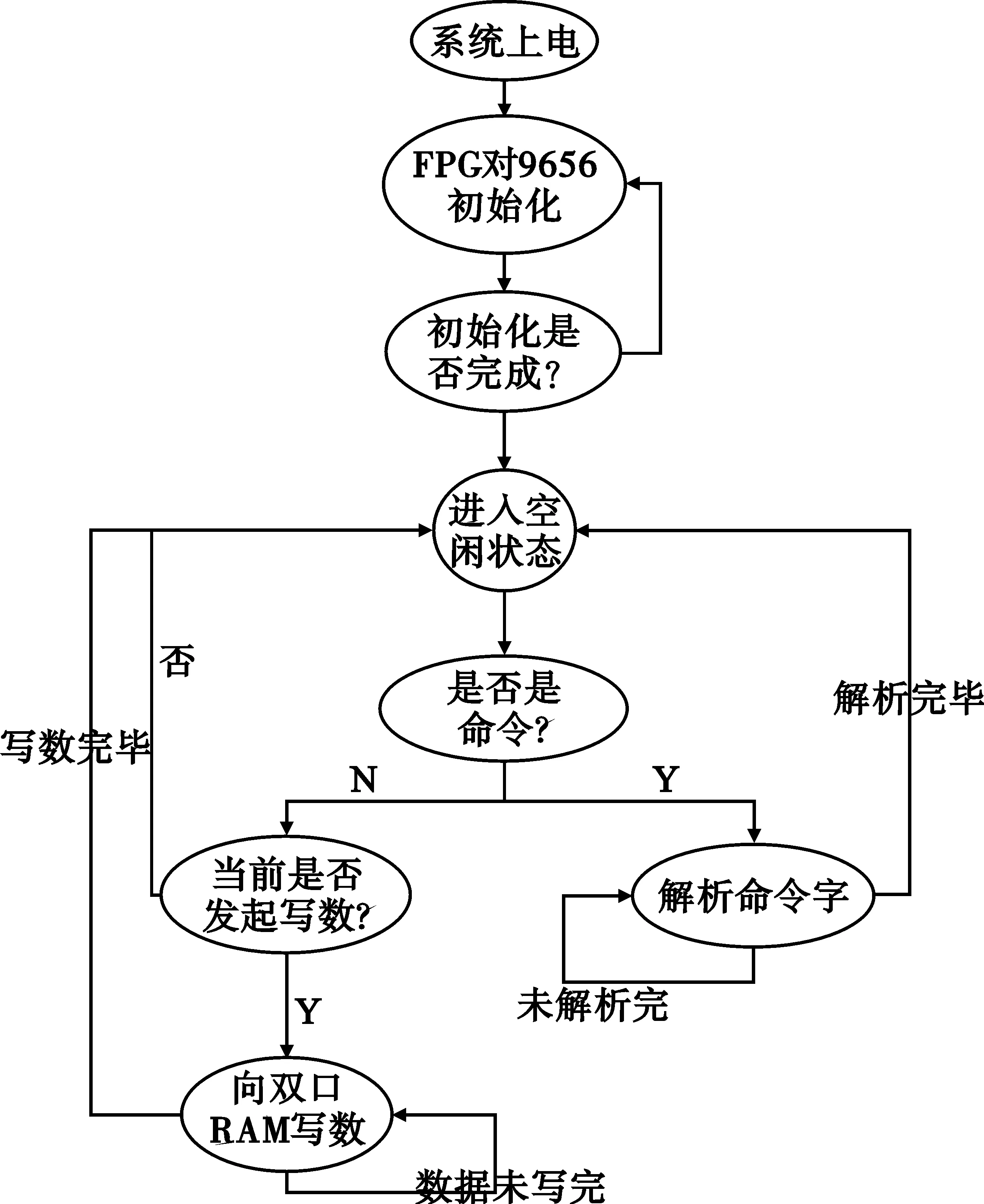

3.2 CPCI接口控制模块

该模块一端与PLX9656的本地总线相连,一端与DDRII控制模块相连,既要担负总线接口功能,还要担负解析终端计算机命令功能。该模块在设计过程中要特别注意隐晦的逻辑错误,此处的逻辑错误将导致整个SAR目标模拟器硬件平台的工作异常。该模块输出控制信号多,而FPGA中Chipscope在线逻辑分析仪采集深度有限,导致出现故障时无法通过工具判断定位,因此在设计过程中要特别注意隐晦逻辑错误。图4为CPCI接口流程图。

图4 CPCI接口模块工作流程图Fig.4 Operating flow chart of CPCI interface module

FPGA上电后首先完成PLX9656初始化,将PLX9656配置为从模式,设置一次CPCI传输最大长度为60 Mbyte,DMA为持续突发模式。通过与PLX9656本地总线接口,接收终端机发出指令与数据,并进行命令解析。

4 测试结果

由终端机产生数字目标回波信号,将生成的两路正交线性调频信号送入硬件平台,平台根据指令输出两路模拟线性调频信号,通过示波器采集模拟信号,并将采集数据导入计算机,在计算机上通过Matlab软件对采集信号进行脉冲压缩,波形如图5所示。从图中可以看出,其脉压后的主副旁瓣比达到40 dB以上,因此可以推知模拟正交基带信号质量非常好,同时判定达到系统设计指标要求。

图5 脉压后波形Fig.5 Waveform after pulse compression

5 结 论

本系统仅通过一块FPGA即实现了对DDRII控制和CPCI数据接收,以及控制六支路三通道D/A输出,该硬件平台具有极高性价比。该模拟器达到了技术指标,满足系统使用要求,可直接应用于各种SAR系统调试与功能验证。未来可以此硬件平台为基础,稍作改动并加载相应仿真数据,即可作为通信系统和电子战的模拟仿真平台,因此具有良好通用性和广阔的应用前景。

参考文献:

[1] 李志国,白雪,潘志明.注入式SAR目标回波模拟系统的设计与实现[J].信息化研究,2009,35(1):34-36.

LI Zhi-guo,BAI Xue,PAN Zhi-ming.Design and Implementation of an Infusing Type SAR Target Echo Simulation System[J].Informatization Research,2009,35(1):34-36.(in Chinese)

[2] 刘嘉元,干汉成,白雪.SAR目标回波基带信号产生模块设计[J].现代雷达,2008,30(1):90-92.

LIU Jia-yuan,BAI Han-cheng,BAI Xue.Design of SAR Echo Base-band Signal Produce Module[J]. Modern radar,2008,30(1):90-92. (in Chinese)

[3] PCI 9656BA data book[Z].[S.l.]:PCI Inc.,2009:30-40.

[4] 竺红伟,刑孟道,夏际金.实时信号处理系统CPCI接口设计[J].雷达科学与技术,2006,4(4):228-232.

ZHU Hong-wei,XING Meng-dao,XIA Ji-jin.Design of Real-time signal processing system CPCI interface[J].Radar Science and Technology,2006,4(4):228-232.(in Chinese)

[5] 陈大平,王勇.DDR SDRAM控制器的FPGA实现[J].仪器仪表用户,2009,16(1):108-110.

CHEN Da-ping,WANG Yong.Realization of DDR SDRAM Controller Base of FPGA[J].Electronic Instrumentation Customer,2009,16(1):108-110. (in Chinese)

[6] Lakshmi,Gopalakrishnan.使用 Virtex-4 器件实现的 DDR2 的控制器[Z].[S.l.]:Xilinx公司,2006.

Lakshmi,Gopalakrishnan.Design of DDR2 controller Base of Virtex-4[J].[S.l.]:Xilinx Inc., 2006. (in Chinese)