主从可配置I2C总线接口IP及其应用*

2010-09-26龚向东黄虹宾2刘春平

龚向东,黄虹宾2,刘春平

(1.深圳大学 电子科学与技术学院,广东 深圳 518060;2.深圳大学 机电与控制工程学院,广东 深圳 518060)

1 引 言

I2C总线作为一种简单、高效的二线制双向串行传输总线,在电子器件及系统中应用非常普遍[1],其严格的通信规范[2]保证了数据传输的可靠性。在基于FPGA的可编程片上嵌入式系统的研究开发中,往往需要设计定制I2C总线控制器,并以IP核的形式集成到系统中。目前,文献中介绍的关于I2C总线接口的设计或对第三方I2C总线接口IP核的应用研究[3~5],功能上局限于作为I2C主设备端口使用,或仅能用作I2C从设备端口。本文介绍一种I2C总线控制器IP,可以编程配置为主设备端口或从设备端口,因此,提供了更广泛的应用选择。这个IP核由美国SLS公司(System Level Solutions, Inc.)发布[6],具有完全兼容Philips I2C标准、支持多I2C主端口工作、宽输入时钟频率范围等特点。

本文首先简要介绍该主从可配置I2C总线控制器IP的硬件结构,然后着重论述在Altera 的Nios II可编程片上嵌入式系统中该IP核的系统集成和应用编程技术,最后给出了实际应用例子。

2 IP核的硬件结构

SLS的I2C总线控制器IP的内部硬件结构如图1所示,主要由波特率时钟发生器、寄存器模块、并行I/O编程接口、I2C编程接口以及I2C接口内核5个模块组成,其它模块用于连接Nios II系统的Avalon总线或用于临时数据存储。

图1 I2C IP核的硬件结构Fig.1 Hardware architecture of the I2C IP core

在5个主要模块中,波特率时钟发生器模块向I2C接口内核提供可编程设置的时钟信号,以便后者产生合适的I2C移位时钟SCL;寄存器模块包括数据移位寄存器、本地地址寄存器、控制寄存器、状态寄存器和时钟寄存器以及这些寄存器的控制电路;并行I/O编程接口模块用于访问寄存器时的接口命令处理;I2C编程接口模块则为上述寄存器以及波特率时钟寄存器建立相应的访问地址;而最核心的I2C接口内核模块实现符合I2C串行协议的数据传输。

除了产生SCL时钟信号外,为了确保数据传输符合严格的I2C规范,I2C接口内核模块具有处理5种级别I2C总线活动的功能:

(1)握手命令处理,检测来自并行接口的I2C传输开始命令和结束命令;

(2)工作模式处理,确定工作模式(包括从端口接收、从端口发送、主端口接收、主端口发送)和相应的传输方向;

(3)宏帧处理,检测帧类型(地址帧或数据帧)以及帧内的不同阶段;

(4)微帧处理,帧的移位过程处理;

(5)信号处理,确定I2C总线SDA上的start、stop信号以及SCL时钟的跃迁变化条件。

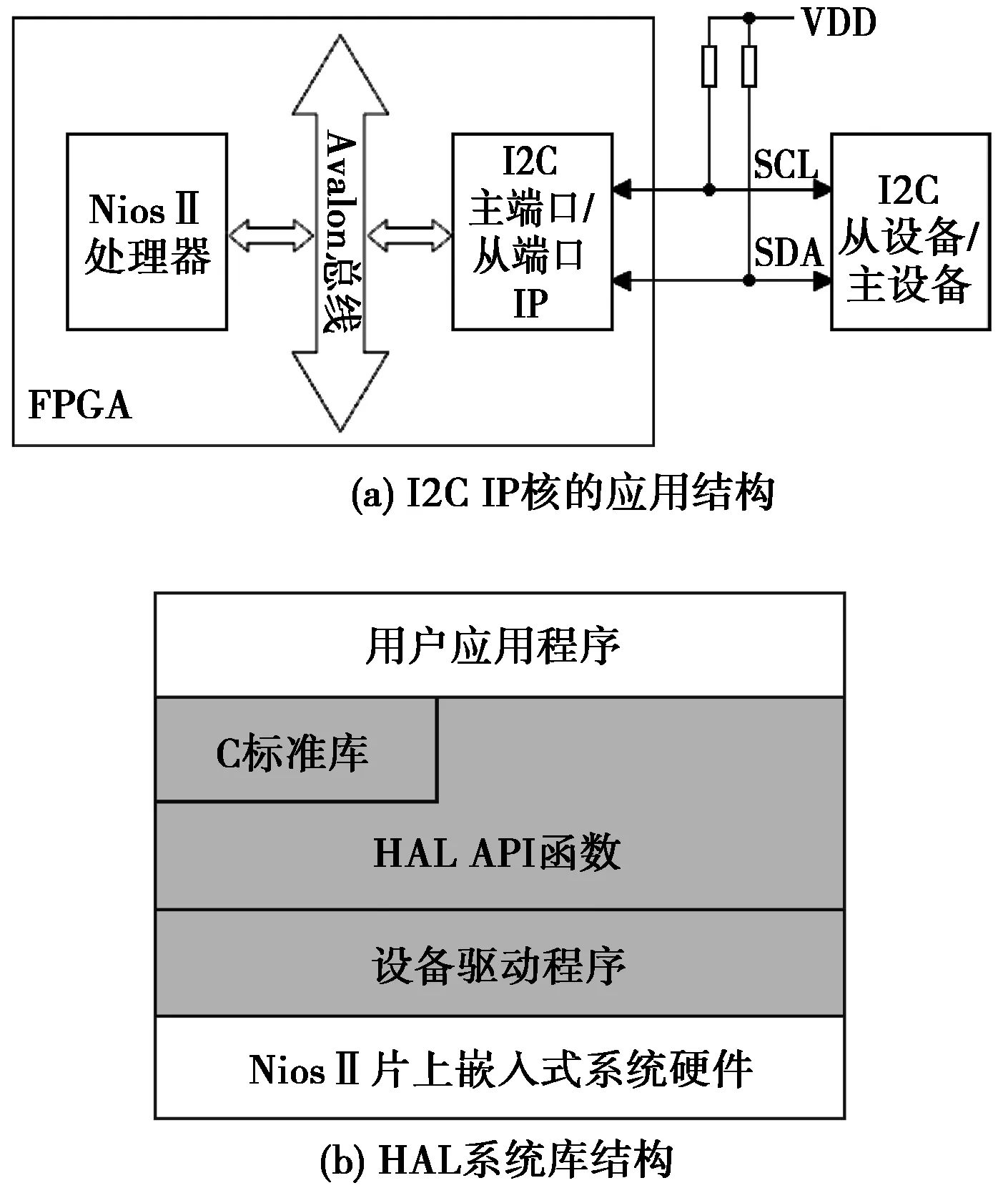

3 IP核的系统集成

目前,在采用32位软核处理器的可编程片上嵌入式系统中,Nios II[7]系统的应用最为广泛。Nios II片上嵌入式系统通过Altera设计软件Quartus II中的SOPC Builder工具构建,并在其FPGA器件上实现。Nios II 处理器、各种系统组件或外设接口IP通过系统内部Avalon总线互连,本I2C总线控制器IP核在系统中的应用结构如图2(a)所示。用户应用程序通过硬件抽象层(HAL)系统访问硬件,作为软件运行环境的HAL系统将C标准库、应用程序接口(API)和设备驱动程序集成在一起,其关系如图2(b)所示。

图2 I2C IP核应用的硬件/软件结构

Fig.2 Hardware/software schemes of the I2C IP core application

为了将I2C IP核封装到系统中,需要的文件包括:

(1)硬件文件:IP核的HDL语言硬件设计文件;

(2)软件文件:定义IP核内部寄存器映像的C语言头文件以及设备驱动程序文件;

(3)组件描述文件:用SOPC Builder的组件编辑器编辑IP核组件时自动生成的文件,这个文件提供了将IP核集成到系统的信息。

当采用SOPC Builder创建了Nios II应用硬件系统后,就可以在Altera的Nios II集成开发环境(IDE)中创建相应的HAL系统库,并进行IP核的应用编程。

4 IP核的应用编程

该I2C总线控制器的使用涉及到以下5个HAL API函数。

4.1 int open(const char* pathname,int flags)

该函数以指定的读写方式(O_RDONLY、O_WRONLY或O_RDWR)打开设备文件,并返回该设备文件号,如:

int fd;

fd=open(I2C_MASTER_0_NAME,O_RDWR);

即以可读可写方式打开设备宏名为I2C_MASTER_0_NAME的I2C总线控制器IP核,设备宏名已在构建Nios II应用系统时生成的系统描述文件(system.h)中定义。

4.2 ioctl(int fd,int req,void*arg)

该函数用于对fd指定的已打开设备进行I/O操作管理,其中参数req给出操作请求、参数arg给出与req请求相应的信息。本I2C总线控制器定义了以下操作请求:

(1)INITBUS:用于设置I2C主/从工作方式和SCL时钟频率的操作请求,相应的arg是类型为InitData的一个结构变量指针。该InitData结构在I2C IP核的设备驱动程序头文件中定义为:

struct InitData{

unsigned volatile char address;

unsigned volatile char clk;

unsigned volatile char Speed;

unsigned volatile char master_slave;

};

其中,address为此IP核的I2C设备地址,该地址以左移1位的形式写入IP核的本地地址寄存器中,clk为波特率时钟寄存器设置值,Speed为时钟寄存器设置值,master_slave为主/从方式选择:1选择此IP核为主端口方式,0选择为从端口方式。由clk和Speed确定的SCL频率按下式计算:

例如,给出如下设置,这个I2C IP核将工作于主端口方式,当Nios II系统频率为50 MHz时,其传输速率为100 kHz。

struct InitData InitI2C;

InitI2C.address=0x55;

InitI2C.clk=0x01;

InitI2C.master_slave=1;

InitI2C.Speed=0x7D;

ioctl(fd,INITBUS,&InitI2C);

(2)SETSLAVEADDR:I2C主端口采用该操作发送I2C从端口(或从设备)地址,此时的arg将以左移1位的形式写入从端口的数据寄存器,并将与从端口的本地地址寄存器内容比较。例如,当从端口实际I2C设备地址为0xD0时,应给出如下编程命令:

ioctl(fd,SETSLAVEADDR,0x68);

(3)CHECKASS:从端口采用该操作请求检查其状态寄存器中的地址匹配位,当主端口发送的从端口地址与从端口的本地地址一致时,该位有效并允许从端口进行后续的数据收发工作,相应CHECKASS请求的arg缺省为0;

(4)CHECKDONEFLAG:主、从端口都可以使用这个操作请求检查自己的数据读写操作是否完成,当数据传送完成时,该ioctl()函数调用返回1,相应CHECKDONEFLAG请求的arg缺省为0;

(5)DATARD:采用该请求的ioctl()函数调用返回I2C IP核的数据寄存器内容,相应DATARD请求的arg缺省为0;

(6)STOPTYPE:该请求用于I2C主端口选择产生停止条件或重复起始条件,前者相应的arg参数为0,后者相应的arg参数为1。

4.3 int read(int fd,void *ptr,int len)

该函数实现I2C IP核的数据接受操作,所读入的len个字节数据存于ptr指针指向的数据缓冲区中。

4.4 int write(int fd,void *ptr,int len)

该函数实现I2C IP核的数据发送操作,ptr为发送数据缓冲区指针,len为待发送数据字节数。

4.5 int close(int fd)

该函数关闭fd指定的I2C IP核。

5 应用实例

众多的电子器件及系统采用了I2C总线传输,如多种实时时钟/日历(RTC)芯片、音/视频编解码器件(CODEC)、LED/LCD驱动芯片以及MCU器件等。在EEPROM存储器、CMOS图像传感器等器件中,I2C的应用更为普遍。我们采用本文所述的I2C控制器IP核对RTC器件M41T00、音频CODEC器件WM8731、CMOS图像传感器MT9M011以及EEPROM器件24LC64分别进行了I2C传输测试,同时也对Nios II应用系统中集成多个I2C控制器IP核的情况进行了实验验证。为此构建的Nios II应用系统的Quartus II工程顶层模块如图3所示,其中包括一个I2C主端口(i2c_master_0)和一个I2C从端口(i2c_slave_0),硬件上只需将主端口的m_scl和m_sda线通过外部上拉电阻与I2C从设备(或从端口)的相应信号线相连,应用程序在外部SDRAM中运行。该Nios II系统中添加了一个1 MHz的信号源(tout),用作内嵌SignalTap II逻辑分析仪的采样时钟。

图3 验证I2C IP核的Quartus II工程顶层模块Fig.3 Top block of Quartus II project for verifying the I2C IP core

限于篇幅,在此仅给出对24LC64的测试结果。24LC64是Microchip公司的一款64K位I2C串行EEPROM器件[8],当该器件内部控制寄存器的3位芯片选择位(A2A1A0)置0时,该器件的I2C设备写地址为0xA0,其I2C设备读地址为0xA1。24LC64共有8K字节存储单元,故存储单元需要通过2个地址字节寻址。24LC64的写方式包括字节写和页写(连续32个存储字节为1页),其读取方式包括当前位置读、随机读和顺序读,图4给出了随机写/读一个数据字节的I2C总线时序要求。随机写过程如图4(a)所示,I2C主端口首先发出低电平start位,然后发出写控制字节(I2C从设备写地址),在收到从设备的应答信号(ACK)后,发送待写入单元的2个地址字节和待写入数据字节,从设备每接收到一个字节都需返回一个ACK位到主端口,最后主端口发出高电平stop信号结束写过程。在图4(b)所示的随机读过程中,至地址字节的写入部分与图4(a)类似。此后,主端口在重复起始条件下发出一个读控制字节(I2C从设备读地址),在从设备的ACK认可后,从设备将所寻址地址单元里的数据发送到SDA线上,主端口接收该数据字节后返回非应答信号(NO ACK)并以stop信号结束读过程。

图4 24LC64的随机写/读时序

Fig.4 Timing diagrams for random write/read of 24LC64

作为一个验证例子,将I2C时钟SCL速率设置为100 kHz,并以随机写/读方式向24LC64的第2 500(即0x09c4)个存储单元写入数据0x56后再从中读出,并通过Quartus II内嵌的SignalTap II逻辑分析工具捕获I2C时钟线m_scl和I2C数据线m_sda信号,所得到的这一写入、读出过程时序分别如图5所示,可见与图4要求的I2C总线时序一致。

图5 24LC64的0x09c4单元写入/读出数据0x56Fig.5 Timing diagrams showing write/read data 0x56 to/from Cell0x09c4 of 24LC64

6 结束语

本文介绍了一种新的I2C总线控制器IP核,该IP核既可以I2C主端口形式也可以I2C从端口形式集成到基于FPGA的可编程片上嵌入式系统中,且在一个系统中可以定制封装多个这样的IP,因此为各种I2C总线传输的应用提供了灵活性。采用这个IP核,通过本文设计Nios II应用系统,对多种电子器件的I2C总线传输进行了测试。实验结果表明,与其它I2C总线接口IP相比,该I2C总线控制器IP核在应用上更具有先进性。

参考文献:

[1] 何立民.I2C总线应用系统设计[M].北京:北京航空航天大学出版社,1995.

HE Li-min.Design of I2C bus application systems[M].Beijing:Beijing University of Aeronautics & Astronautics Press,1995.(in Chinese)

[2] Philips Semiconductors.The I2C-bus Specification,Version 2.1[EB/OL].2000.http://www.nxp.com/acrobat_download/literature/9398/39340011.pdf.

[3] 钱敏,黄秋萍,李富华,等.基于VHDL/ CPLD的I2C串行总线控制器设计及实现[J].电子技术应用,2006,32(8):109-112.

QIAN Min,HUANG Qiu-ping,LI Fu-hua,et al.Design and implementation of I2C serial bus controller based on VHDL/CPLD [J]. Application of Electronic Technique,2006,32(8):109-112.(in Chinese)

[4] 段沛沛,邓晔.基于VHDL的I2C总线从模式控制核设计[J].火控雷达技术,2008,37(4):86-89.

DUAN Pei-pei,DENG Ye.Design of I2C bus slave mode control core based on VHDL[J].Fire Control Radar Technology,2008,37(4):86-89.(in Chinese)

[5] 康文峥.基于NiosⅡ的I2C主设备接口的设计[J].舰船电子工程,2009,29(3):118-120.

KANG Wen-zheng.Design of I2C master device interface based on Nios II[J].Ship Electronic Engineering,2009,29(3):118-120.(in Chinese)

[6] System Level Solutions,Inc..IP Core I2C Controller [EB/OL].2009.http://www.slscorp.com/pages/ipi2ccontrollersls.php.

[7] Altera Corporation. Nios II Processor Reference Handbook[EB/OL].[2009]http://www.altera.com/literature/hb/nios2/n2cpu_nii5v1.pdf.

[8] Microchip Technology,Inc..24AA64/24LC64 64K I2C Serial EEPROM[EB/OL].[2002]http://ww1.microchip.com/downloads/en/devicedoc/21189f.pdf.