基于闭环控制的高精度三相电源的设计

2010-09-25张静,杨奕,徐勤

张 静,杨 奕,徐 勤

(重庆理工大学 电子信息与自动化学院,重庆400054)

某设备需要高精度的三相电源,工作频率为500 Hz ,单相电源之间的相位误差小于0.01°。经过多种技术对比后,在DDS 技术的基础之上,采用相位自动检测与自动修正的闭环结构。该技术有效地消除了温度、元器件参数等因素的影响,使电源能够长期稳定可靠地工作。

1 工作原理

高精度三相交流稳压电源工作原理图如图1 所示。采用直接数字频率合成技术来产生三路相位互差120°的正弦信号,正弦信号的频率由高频基准时钟分频得到,其稳定性由作为基准时钟的晶体振荡器决定,而现在晶体振荡器的频率稳定性极高(在10-9级别),因此采用这种设计方法首先就能保证电源频率长期稳定性。并且,这种方法能对电源频率进行精确控制。DDS 电路主要包括一块FPGA和其他辅助电路构成。三路正弦信号经功率放大后得到三相驱动电流A、B和C。三相驱动电流A、B 和C 之间的相位差分别为:

式中:φAB为 A、B 相之间的相位差;φBC为B、C 相之间的相位差;φA为A相电流的相位;φB为B 相电流的相位;φC为 C 相电流的相位。

图1 三相电源工作原理

在FPGA中分别计算120°减去φAB和φBC的值,得到的2 个差值ΔA和ΔC 的表达式如下:

ΔA和ΔC 作为反馈信号引入DDS 的信号处理中。由于ΔA和ΔC 是通过计算得到的数字结果,所以很容易实现数字补偿。ΔA对A 相驱动电流进行相位调制,ΔC对C 相驱动电流进行相位调制,通过这种方式很容易就构成了一个闭环系统,控制φAB和φBC保持几乎不变。

2 基于DDS 技术的正弦信号的合成

DDS 的工作原理就是通过累加比某一给定频率高的相位变化来产生给定频率的数字化波形[1]。如图2 所示,DDS 主要由相位累加器、相位调制器、正弦查找表和D/A转换器构成。相位累加器、相位调制器和正弦查找表是DDS 的数字部分,可以实现数字控制。相位累加器是整个DDS 的核心,实现相位累加功能。正弦查找表完成一种查表功能,实现相位到幅值的转换,它的输入是相位调制器的输出;输出送往D/A,转化成模拟信号。相位累加器的输入是一个系统时钟周期内的相位增量Δφ,输出信号频率fOUT和Δφ之间存在一个简单线性关系:

式中,N为相位累加器的数据位数;fCLK为系统时钟频率。

图2 基于DDS 的正弦信号合成原理框图

为了输出某一特定频率的信号,需要从频率控制寄存器输入相应的相位增量值,因此相位累加器的输入又可称为频率字输入。相位累加器的值在每个时钟周期与寄存在频率控制寄存器中的相位增量值累加一次。因此,输出的正弦信号SOUT可以表示为:

式中,Am为输出信号幅值;φK为当前的相位值;φK-1为上一个时钟周期的相位值。

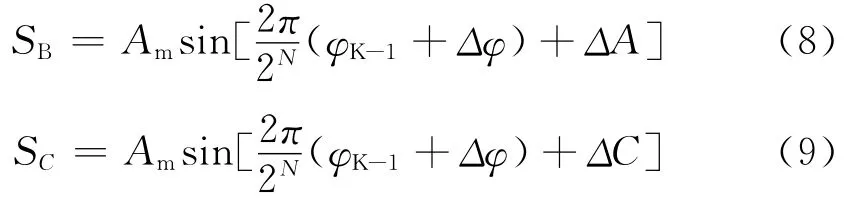

相位偏差输入可对相位累加器输出进行相位调制。ΔA和ΔC 作为相位偏差输入分别从2 个相位偏差控制寄存器输入到DDS 中(见图1 和图2)。假设B相驱动电流信号的表达式为:

则A相和C 相电流的表达式为:

再结合式(1)~(4),式(8)、(9)可以写为:

图3 FPGA 电路结构

从式(10)和式(11)明显看出,采用前述方法可以实现对三相驱动电流频率大小的精确控制,相位差ψAB和ψBC可以保持在120°基本不变。采用图1 所示的数字闭环控制技术实现了对相位差的自动补偿。

3 硬件电路设计

由于该电路为三相交流电源,每相电源互差120°,三相电源的电路结构与参数相同,下面的电路设计部分只给出其中一路。

3 .1 FPGA

电路的核心部分主要采用FPGA芯片EP2C5T144,芯片资源丰富,芯片内核采用1.2 V电压,I/O部分采用3.3 V电压[1]。该芯片主要包括完成DDS与频率误差修正两个模块,引脚D1~D36作为三路信号的D/A转换的数据接口,端口SA_PHASE、SB_PHASE 和SC_PHASE 分别是三相输出信号经过处理之后信号,主要是为了进行数字比相。具体电路设计如图3 所示。

3 .2 D/A

该部分的功能主要是将FPGA输出数字信号转换成模拟信号,采用12 位的高速D/A转换芯片AD7541,电压基准芯片ADR440BRZ 产生+4 V的高精度基准电压作为AD7541 的参考信号。利用高精度运算放大器OP4277 进行放大处理,输出双极性正弦波信号DA_OUT,具体电路结构如图4 所示。

图4 D/A 电路结构

3 .3 滤波电路

由于设计电源的频率为500 Hz ,采用1 个二阶低通滤波器和1 个二阶高通滤波器串联组合成1 个带通滤波器[2],低通滤波器的截止频率fH=450 Hz ,高通滤波器的截止频率fL=550 Hz ,形成通频带为100 Hz 的带通滤波器,滤除掉上一级D/A 转换电路的输出信号中的高频干扰信号以及其它低频干扰信号,电路结构如图5 所示。

图5 带通滤波电路

3 .4 功率放大

图6 功率放大电路

功率放大采用高效率的音频功率放大器芯片STK4040 ,额定输出功率达70 W,谐波失真为位修正,0.003 %,3d B 频响为20 Hz ~20 k Hz ,能够充分满足系统的功率放大要求,具体电路如图6 所示。

3 .5 信号整形

图7 信号整形电路

为了对经过功率放大之后的三相输出信号进行相以获得高度对称的三相驱动信号,首先将输出的三相信号分别通过变压器耦合的形式转换为相应的小信号,再经过过零比较,输出相应的方波信号SA_PHASE、SB_PHASE 和SC_PHASE,结构如图7 所示。

4 软件设计

软件设计部分主要是利用V HDL 语言开发完成,具体框图如图8 所示,主要有2 个功能模块,一是数字比相模块,一是带相位修正的DDS 模块[3~4]。数字比相模块根据式(3)和式(4 )比较3 个输入信号 A、B 和C 两两之间的相位差,然后将差值反馈到带相位修正的 DDS 模块中。DDS 模块根据式(7 )、式(8 )和式(9 )产生高精度的三相正弦信。

图8 软件结构框图

5 结束语

利用DDS 技术构成的带相位自修正的高精度三相交流电源,具有输出频率稳定度高、分辨率高、易编程控制等优点。采用闭环控制技术来消除温度、电子元器件老化等因素对电源精度的影响,具有较高的实际应用价值。

[1] 潘 松,黄继业.EDA技术实用教程(第三版)[M].北京:科学出版社 ,2007 .

[2] 张国雄.测控电路及装置[M].北京:机械工业出版社,2007 .

[3] 邓耀华,吴黎明,张力锴.基于FPGA的双DDS 任意波发生器设计与杂散噪声抑制方法[J ].仪器仪表学报,2009 ,30(11):2255-2261 .

[4] 孙 群,宋 卿.基于DDS 技术的便携式波形信号发生器[J ].仪表技术与传感器,2009 ,(4):67-70 .