基于FPGA的DVB-S调制器系统设计*

2010-09-17刘庆丰陈金鹰王舟兵李俊葶

刘庆丰 ,陈金鹰,王舟兵,李俊葶

(1. 成都理工大学,四川 成都 610059;2.成都首创电子有限公司,四川 成都 610092)

1 引言

数字电视前端设备调制器是数字广播包括不可缺少的中心端设备,它的性能、升级能力和兼容性直接影响整个系统的运营状态。目前各国的数字传输标准主要有日本的ISDB标准、美国的ATSC标准、欧洲的DVB标准。目前中国在制定属于自己的数字卫星电视标准,已完成广播电视卫星传输的数字化改造,形成了以DVB-S技术架构的数字电视卫星广播网。各地广电部门也广泛采用DVB-S作为卫星传输标准,此标准作为过渡标准基本得到认同,本文的前端调制器设计也采用此标准[1]。

2 调制器总体设计

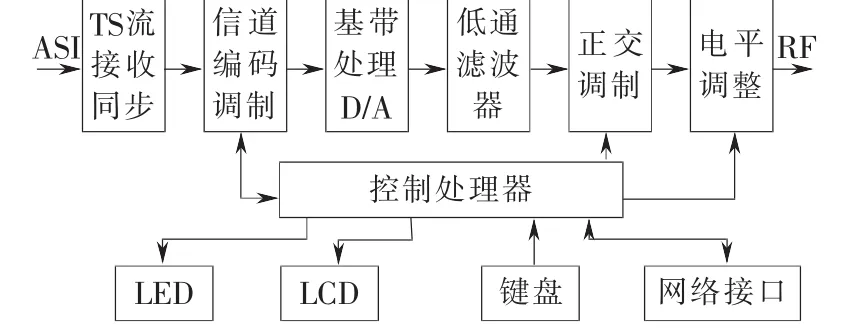

通过对基于FPGA的DVB-S调制器系统进行研究,将ARM与FPGA联系起来,从而建立系统的运行平台,ARM做控制器,FPGA做处理器,此系统关键技术有信道编码和基带信号处理。前端调制器组成框图如图1所示。

图1 DVB-S调制器组成框图

本设计主要由TS传输流接收、信道编码、基带信号处理及D/A、低通滤波器、正交调制及射频输出电平调整电路、微控制器处理部分等组成。系统能实现信道编码、QPSK调制、输出频率和电平可调等功能[2]。

3 调制器模块实现

据图1可知,可将DVB-S调制器的工作分解为:TS传输流接收与同步锁定、信道编码、基带信号处理及D/A、低通滤波器、正交调制及射频输出电平调整、微控制器处理等。下面介绍各个模块的接口定义与实现。

1) TS传输流接收与同步锁定[3]

DVB-S信道编码调制器的输入为TS流信号,TS流信号在工程上一般有两种方式,同步并行接口SPI信号和异步串行接口ASI信号。目前市场采用的大都是串行的ASI信号,对于ASI信号,DVB标准也对其做了规定,电平为800 mV,信号速率为270 Mbit/s,数据编码为8 bit/10 bit编码,空闲状态插入K28.5的同步字符,以利于时钟恢复。

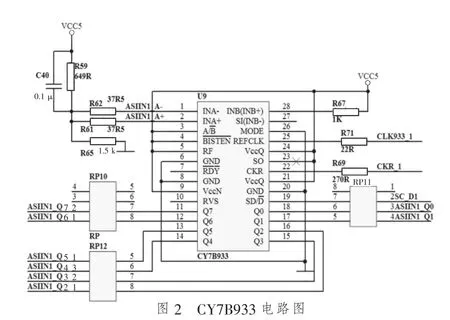

为便于信道编码处理,需对ASI信号处理恢复成并行的TS流信号。一般有两种方法,一种是用专用芯片,另一种利用FPGA软核完成。此设计采用Cypress公司的专用芯片CY7B933,其电路图如图2所示。

TS流同步搜索与锁定根据TS流同步字为47 hex,在数据流中搜索同步,标记包的起始位置和包有效标志,并锁定同步。该模块的接口定义为:

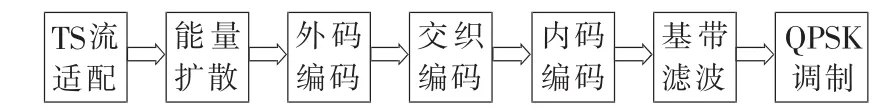

2) 信道编码调制[4]

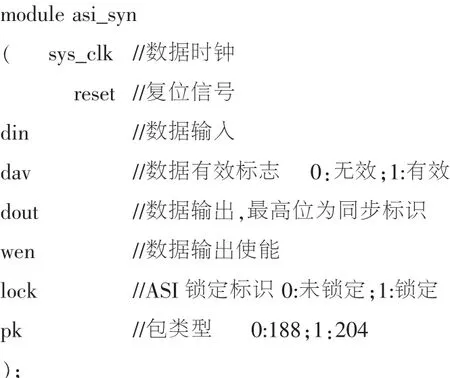

DVB-S标准提供了一套完整的适用于卫星传输的数字电视系统规范,用此标准完成码流调制编码框图如图3所示。

图3 信道编码框图

TS流适配单元是由于输入的TS流时钟是可变的,因此必须进行时钟匹配,包括去除输入TS流信号的空包、进行PCR校正、自动插入空包等过程。能量扩散单元是为了较好地进行时钟同步信号的恢复。要确定传输的TS流中的01跳变足够多,需要对输入的传输流进行随机化处理,伪随机序列生成多项式为

前向纠错(FEC)由3层组成,外层采用RS编码,它是在188 byte的传输包后按一定的规律加上16个校验字节, 形成 RS(204,188,T=8)误码保护数据包。 码生成多项式为

其中,b=02 hex。

有限域生成多项式为

中间层采用卷积交织,卷积交织把输出数据的顺序按照一定规律打乱,接收端按相反的规律恢复原来的数据顺序。内层采用卷积编码,生成1/2码率的卷积码。再按不同的删除格式按需要收缩成码率为2/3,3/4,5/6,7/8的收缩卷积码。前向纠错编码的根本目的是提高传输的可靠性。前向纠错编码输出一连串的窄脉冲,它占用的频带太宽,无法在卫星信道中传输。基带成形电路则对这种窄脉冲“加工”,使其适合在卫星信道中传输。对这种加工采用快速傅里叶变换对窄脉冲进行平方根余弦滚降滤波,滚降系数为a=0.35。

3) 基带处理及D/A变换

信道编码完成后,数据流经过IQ对排列依次输出,即对每个节拍到来的IQ进行符号映射。对于D/A设计接口,选择AD公司的AD9775,其最高采样时钟为400 MHz。

4) 模拟基带低通滤波器[5]

D/A输出信号为基带信号,由于内插滤波器的缘故,在基带符号率和4倍符号频率之间的信号被滤波器抑制。根据大多数MMDS信道需要采用的符号率为30 MS/s(兆符号/秒),因此对设计的模拟低通滤波器的要求就是能取出30 MHz信号即可。使用仿真软件RFsim计算9级48 MHz低通滤波器参数。由于AD9775输出的IQ信号为差分信号,仿真出来的滤波器为单端的,因此需要把单端低通滤波器转化成双端差分低通滤波器。

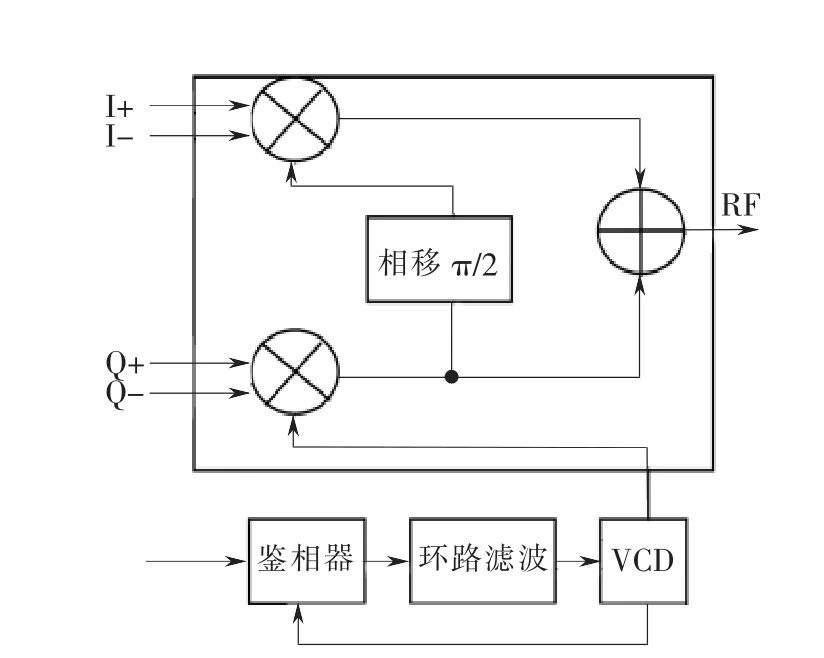

5) 正交调制

正交原理如图4所示,由PLL环路产生射频调制的载波信号,I路信号乘以载波加上Q信号乘以相移π/2的载波信号,然后相加得到调制的QPSK射频信号。选用的正交调制器为AD公司的AD8346。IQ信号由AD9775输出,经过低通滤波器,输入到AD8346,本振信号由PLL+VCO电路产生,锁相环器件采用ADF4113,VCO793-750。鉴相器输出频率为

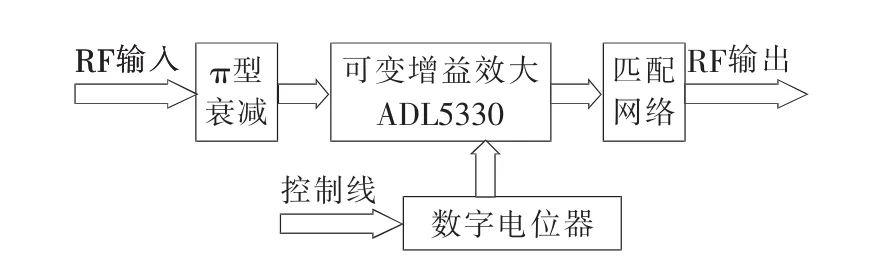

6) 输出电平调整和阻抗匹配

设计要求射频输出电平为-35~0 dBm,输出阻抗为75 Ω,正交调制器AD8346的最大输出电平达不到要求,而且它的输出阻抗为50 Ω,因此要在后面做可变增益调制和阻抗匹配,原理图如图5所示。

可变增益放大采用ADI公司的ADL5330,数字电位器采用AD5247,采用I2C控制接口。

图4 正交调制原理图

图5 输出电平调整与阻抗匹配

7) 微处理器控制接口

主要完成对调制器的参数设置、状态显示、锁相环控制、射频电平控制、网络控制等。

4 测试原理与结果

测试原理:DVB-S调制器输入信号为ASI格式的MPEG-2传输流,该传输流信号可由编码器、码流播放器等设备产生,通过码流播放器输出ASI信号进入DVB-S调制器,用示波器测试时域波形,用频谱仪进行频谱分析。调制器输出信号经过机顶盒解调输出音视频信号,输出TS流。用码流分析仪对输出码流进行分析,分析输出码流是否符合MPEG-2协议,对比输入输出码流是否正确。

通过对系统功能的测试,观察DVB-S调制器前后码流声音与图像的变化、码流节目参考时钟PCR的变化,结果表明信道编码及调制过程无错误。通过对系统技术指标的测试,如SNR(带外)≥48 dB,结果表明DVB-S调制器符合DVB-S调制协议设计要求。

5 小结

本文的调制器已广泛用于数字电视卫星业务和相关数字电视业务。调试运行表明,该系统能实现设计的所有功能要求,运行良好,现已推向了市场,样机外观见图6。

图6 DVB-S调制器样机图

:

[1]谭智斌.一种数字有线电视前端调制器的设计[J].中国有线电视,2008(2):121-124.

[2]刘庆丰.基于RFID小区车库智能化管理系统[J].通信技术,2009(7):189-191.

[3]葛锦环.基于FPGA的DVB-S QPSK调制器的设计[D].成都:电子科技大学,2006.

[4]葛锦环.基于FPGA的DVB-S中信道编码与实现[J].中国有线电视,2006(6):541-544.

[5]张义林.基于FPGA实现DVB-S信道编码及调制[D].成都:电子科技大学,2006.