高性能线性CCD开发平台的研制

2010-09-03易茂祥颜天信

梁 冰, 易茂祥, 颜天信

(合肥工业大学电子科学与应用物理学院,安徽合肥 230009)

线阵电荷耦合器件已经广泛地应用于航天、军事及民用工业领域。民用方面主要应用于印刷特征标志、印刷套色、物体外观缺陷、零件外形尺寸等非接触检测和图像扫描输入场合[1-3]。

研制高性能的CCD开发平台是线阵CCD发展的新方向。本文系统利用CCD信号处理器进行图像采集,采用ALTERA的低成本PFGA为核心,使用硬件描述语言在ALTERA的QuartusⅡ开发环境中对CCD进行驱动时序控制,对模数转换器进行采样控制。利用软核处理器与SDRAM协调完成图像数据存储以及与外围设备通讯控制等。此平台并行处理程度高,可实现高速处理,集成度高,硬件电路简单,避免了传统设计中使用大量分立元件的繁琐方式。

本设计将系统分为6大模块:CCD光电转换模块、CCD图像数据采集模块、驱动电路模块、FPGA图像处理与数据缓存模块、I/O通讯模块及电源模块。本文主要介绍硬件结构及原理。

1 系统硬件组成及原理

FPGA作为整个系统的核心部分,需要提供CCD工作时钟和CCD信号处理器的时钟[4,5]以完成视频信号的预处理,采样量化后的数字信号通过FPGA的控制完成SDRAM与接口的通讯。为了使用灵活,配以多种外围接口,包括Camera Link、USB、以太网口以及串口。系统框图如图1所示。首先利用FPGA产生CCD工作时钟,通过调幅后的时钟送入CCD中,CCD输出的模拟信号通过CCD信号处理器经过信号处理后,转化为12位的数字信号输入到FPGA中。整个平台还配有SDRAM作为数据存储,各种丰富的接口用来传输数据。

图1 系统硬件平台功能框图

FPGA实现功能的核心框图如图2所示。

图2 FPGA功能结构框图

将FPGA资源分为4大部分来实现相关功能。Nios处理器是用来实现USB、以太网的通讯及协同SDRAM完成图像数据的缓存。而另外3部分则直接通过硬件描述语言对FPGA编程完成。本设计的FPGA选用ALTERA公司的第3代低成本FPGA EP3C16Q240C8,它是65 nm工艺的FQFP封装240引脚的产品,且内带NiosⅡ软核处理器。它包括 15408个逻辑单元,504 KBit存储量、56个乘法器、4个PLL和20个时钟网络,它还有160个I/O接口。经过估算,此FPGA完全可以实现该系统的要求。以上结构显示此系统方案充分体现了软硬结合的特性,展现了利用FPGA进行系统开发的优势。

2 系统的具体实现

根据以上方案思路,本文选择了具体芯片来完成系统的搭建。

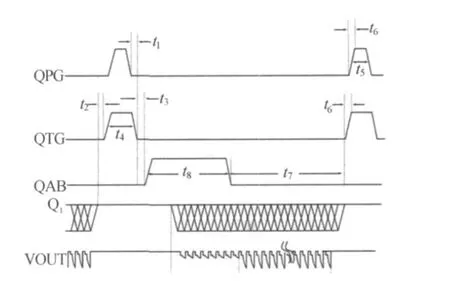

2.1 CCD光电转换与时序驱动

本设计线阵CCD采用PerkinElmer的RL2048P是两相阵列2048象元摄像器。选用该型号的原因是,它的感光面积大,信噪比高,灵敏度高,成像效果好,在单端输出无拖曳动态成像。像素数据率达到40 MHz。输出的图像信号经过信号处理器进行高速A/D转换,将模拟信号实时地转换成数字信号。RL2048P共需要6路驱动时钟,即复位信号(QRG)、电荷转移信号(QTG)、两相时钟信号(QH1,QH2)、电子曝光控制信号(QAB)、电荷转移控制信号(QPG)。各驱动时钟的时序关系如图3所示。

图3 CCD工作时序

FPGA输出的CCD驱动时钟通过设计合适的时序驱动电路实现信号调幅。CCD需要的时钟电平很多,达到7种之多。这是本设计的一个难点,本文采用CDC329A实现由QH1到QH2的反相,且摆幅也调整到高电平的+5 V,低电平的0 V。利用 TC4427EDA调整 QAB、QPG、QTG的幅值。而QRG的电平通过 TT L电路实现。

2.2 图像数据采集与驱动控制

CCD输出的模拟信号经过三极管放大后的模拟前端电路,需要进行相关双采样电路去除复位噪声及低频噪声等,然后还需进行增益调整放大,主要是为了在不同光照下使CCD信号较好地处在模数转换的量程范围内,从而使图像不至于太暗或饱和[6-8]。本设计选用AD公司生产的专用的高性能CCD信号处理器AD9945,它除了具备上述功能外,还包括黑电平箝位电路和预匿影功能、对信号偏移进行调整、对哑象元屏蔽等功能。最后通过精度12 Bit的ADC输出数字信号。

AD9945所需的控制时钟均由FPGA硬件实现,输出的数字信号将送入FPGA中。在模拟前端的相关双采样阶段,利用SHP、SHD作为相关双采样时钟,DATACLK作为数据输出锁存时钟。CLPOB为黑像素箝位时钟,PBLK则为预匿影时钟。通过相关双采样电路及黑像素箝位后,CCD输出的模拟信号有效抑制复位噪声和低频噪声,下一级将进行模数转换。在本设计中将CCD输出的模拟信号转化为12位的数字信号。时钟相位关系具体如图4所示。

图4 AD9945工作时序

2.3 I/O接口模块

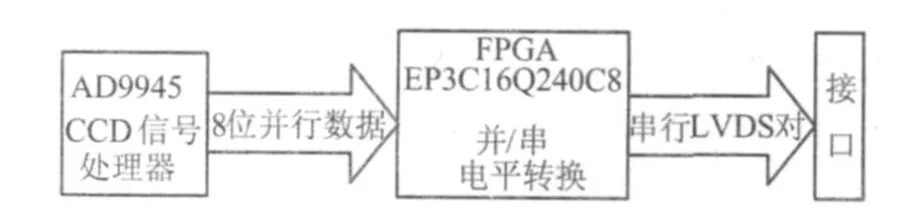

(1)Camera Link接口。Camera Link是一种基于LVDS(低电压差分信号)协议标准的用于数字相机的标准接口。实现Camera Link接口协议至少需要11对LVDS构成。根据上述思想,FPGA需要完成CMOS电平到LVDS电平的转换及8位并行数据到LVDS对的转换。

ALTERA的低成本FPGA cyclone 3系列,提供了丰富的高速差分信号接口。其中内置了LVDS转换模块,可将COMS信号转换为低电压差分信号,用来实现数据的高速传输。其中FPGA的左右模块发送速度能达到840 Mb/s,接收速度达到875 Mb/s。

使用FPGA块5、6的低电压差分信号I/O实现LVDS接口通讯。ALT ERA EP3C16Q240C8可实现 T TL/CMOS电平到LVDS电平的转换,因此,本设计只需用FPGA硬件实现一个串化器,将串行化后的数据送到专用的低压差分信号接口输出即可。用FPGA硬件实现Camera Link协议的原理如图5所示。

图5 Camera Link协议实现原理

(2)串口。本设计利用FPGA的NiosⅡ处理器完成对输入串口数据的控制。利用MAX3221完成CMOS电平到串口电平的转换。在此设计中采用DMA方式即直接存储器方式完成串口数据的传输。使用DMA传输方式的优点在于存储器不经过微处理器直接将数据传送至外部设备,一次DMA传输只需执行1个DMA周期,因而能显著提高数据传输速度。在ALT ERA的QUART USⅡ的SOPC Builder内部集成了一个DMA控制器部件,可以用它来协调外设接口和存储器的数据传输。运用NiosⅡHAL中DMA的API函数可方便地使用C语言编程,实现SDRAM存储器与外设串口的数据传输。

(3)网口和 USB口。本设计采用的网口芯片是CRYSTAL公司生产的CS8900A以太网控制器,它是一款 Nios2可编程配置的芯片。CS8900A是用于嵌入式设备的低成本以太局域网控制器。它的高度集成设计使其不再需要其它以太网控制器所必需的昂贵外部器件。CS8900A包括片上RAM、10Base-T传输和接收滤波器,以及带24 mA驱动的直接ISA-总线接口。除此之外,CS8900A还提供其它性能和配置选择。它独特的Packet Page结构可自动适应网络通信量模式的改变和现有系统资源,从而提高系统效率。

USB控制芯片选用的是Philips公司的单片串行总线ON-THE-GO控制器ISP1362,支持全速(12 Mb/s)和低速(1.5 Mb/s)的数据传输。

2.4 电源模块

系统输入电源采用+15 V输入,根据计算电路系统的功耗和电流驱动能力选择TPS54331作为开关电源,最大可提供3 A电流。由于该系统共需9种电压源,所以为了保证系统的统一性,尽可能采用简单的方式来实现,均采用 TLV1117实现电平的转换。通过改变外接电阻的值来得到所需的电压。

3 结 论

(1)从功能上看,本系统最大的特点是CCD工作在40 MHz时钟下,数据传输速率大、接口丰富。此系统既能满足用户对图像采集后数据的分析研究,也可以通过FPGA算法实现图像采集后的预处理,通过高速差分信号接口传输给下一级进一步分析处理,从而实现开发平台的多用途和多功能化。

(2)从硬件系统设计看,采用PCB四层板。模拟部分和数字部分分开布局。高速电路与低速电路尽量远离,且高速避免信号之间的干扰。

(3)经过系统调试,电源模块工作稳定,各芯片工作正常,各接口均可实现数据传输,通过JTAG口和AS口能正常下载硬件程序和Nios程序。

[1]ShefferD.Random addressable 2048×2048 active pixel im

age sensor[J].IEEE T rans Electron Devices,1997,44(10):1716-1720.

[2]李明伟,黄 鸽,刘静茹.一种高速线阵CCD图像数据采集系统[J].仪器仪表学报,2005,26(8):716-718.

[3]王庆有.CCD应用技术[M].北京:电子工业出版社,2003:15-98.

[4]佟首峰,阮 锦,刘金国,等,智能型高速CCD相机的时序电路的研制[J].光学技术,2000,26(6):552-555.

[5]李翰山,王泽民,雷志勇,等.基于 CPLD的高速线TDI CCD驱动电路设计[J].计算机测量与控制,2007,15(1):122-124.

[6]薛寒光,朱衡君.一种基于FPGA的线阵CCD驱动器的设计[J].中国仪器仪表,2005,12:97-99.

[7]曾 锋,易茂祥.图像采集系统的线性CCD驱动电路设计[J].合肥工业大学学报:自然科学版,2009,32(1):120-124.

[8]蔡荣太,王延杰.视频监控用线阵CCD摄像机的设计[J].测试技术学报,2007,21(5):435-438.