基于FPGA原型的GPS基带验证系统设计与实现*

2010-08-12冯华星何文涛李晓江

冯华星,何文涛,李晓江

(1.中国科学院微电子研究所,北京100029;2.杭州中科微电子有限公司,杭州310053)

随着SoC设计复杂度的提高,验证所需时间已经占到整个设计周期的70%以上,如何减少验证时间成为一个十分重要的问题。GPS基带芯片是一个典型的SoC,其主要功能模块是相关器,用以实现GPS信号的解调和解扩。相关器占据了基带芯片中的大部分硬件资源,其仿真过程十分复杂且耗费大量时间,因此仅仅依靠软件仿真是不现实的。随着FPGA的性能和容量不断提高,基于FPGA的原型验证能够减小开发风险,避免软件仿真的缺点,加快产品上市时间,并且能够真实地反映硬件的特性。这些优点使得基于FPGA的原型验证越来越多地被用于SoC系统的设计过程。

1 从ASIC到FPGA原型的移植

理论上,FPGA原型验证要与SoC的结构保持高度一致,但是,由于ASIC和FPGA结构上的差异,导致从ASIC到FPGA的移植需要做出适当的调整。

首先,当设计规模很大时,单片的FPGA容量不足以容纳整个设计规模,需要2个或多个FPGA芯片来实现整个验证系统。这时,FPGA之间的布线延时给整个系统的时序要求带来困难,尤其对于高性能的设计。其次,结构上的差异导致的ASIC和FPGA IP模块在时序上不兼容,需要额外的工作进行时序转换。再次,某些硬IP核无法移植到FPGA上,需要构造适当的电路或者增加外围辅助电路。

2 GPS基带系统架构

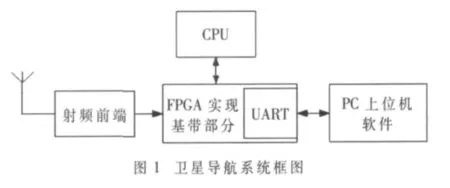

整个GPS卫星导航系统包括前端射频部分和基带部分。前端射频部分完成信号接收、滤波、AD转换等;基带部分完成GPS信号的解调、解扩、实现信号的跟踪和捕获。其系统框图如图1所示。

该卫星导航基带芯片基于ARM7TDMI构建,拥有为捕获跟踪功能所设置的特殊硬件器件以及大量的常用外设。例如DMA、UART接口、SPI接口、GPIO、实时时钟(RTC)等。256 KB的ROM和96 KB的SRAM用于存储代码和运行程序以及中间数据,并可外接FLASH进行程序调试及下载。其基带框图如图2所示。

3 FPGA验证平台设计和实现

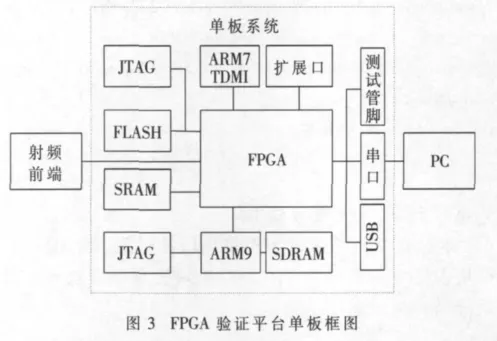

FPGA验证平台的结构如图3所示。

FPGA芯片采用Altera公司Stratix III系列的EP3SL-150F1152C3,ARM7CPU采用ARM7TDMI的验证测试芯片,ARM9芯片采用Samsung的S3C2410芯片。

由于ARM7内核无法移植,所以采用外接的ARM7TDMI测试芯片作为CPU,同时电路板上集成了一块ARM9芯片。因此该平台也可用于基于ARM9内核的SOC验证平台,并且板上预留的扩展接口可以再接一块ARM9芯片,可用于双核的开发。

基带芯片其他部分都位于FPGA芯片中。编译后的电路通过FPGA旁边的JTAG接口下载到FPGA芯片中,通过ARM旁边的JTAG接口进行软件下载和调试。软件调试工具使用ADS1.2。信号可以通过RS232串口或者USB接口与上位机进行通讯。

4 验证中的问题分析和解决

从ASIC到FPGA的移植需要根据实际情况做一些调整。在该系统中,采用ARM7TDMI测试芯片的CPU时钟由FPGA内部产生,经由电路板送到ARM7芯片,由于板级布线延时,FPGA内部时钟和ARM7时钟在相位上不再保持同步,由此造成时序混乱。因此,在FPGA输出时钟到ARM7之前要做相位调整,以补偿在板级线路的延时。

FPGA验证也有不足之处。

首先,调试困难,由于EDA工具不够完善,所以缺乏有效的调试手段。示波器和逻辑分析仪作为主要的调试工具,在问题的定位上给验证人员提出了更高的要求;虽然目前的EDA软件集成了内部的在线逻辑分析仪,但是在使用上仍然有缺陷。协助调试方法主要有2种:(1)软件仿真和硬件模拟结合,当硬件调试很难对问题定位时,可以将代码编译成二进制文件保存到ROM中,在软件平台上运行程序,提高信号的可观察性。(2)在基带结构中增加测试电路,对关键信号进行监视,当出现问题时可利用测试电路所保存的数据进行分析。

其次,ASIC和FPGA结构上的差异给验证工作带来了额外的负担。验证人员需要时刻保持ASIC和FPGA在版本上的一致性。原则上,ASIC上的任何的改动都要精准地反映在FPGA中,二者的一致性是相对的,验证人员需要做到心中有数。要做好二者的一致性,要对模块进行正确划分。把从ASIC到FPGA需要调整的部分单独划分出来(不影响系统系能的前提下)。这样,当ASIC部分进行代码更新时,只要不涉及到需要调整的部分,全部替换即可。这样即节省了时间,又保证了二者的一致性。

再次,FPGA平台运行性能较差。在本系统中,CPU和AHB总线的时钟可以稳定运行在100 MHz左右,但是,ARM7和FPGA之间布线延时造成ARM7最高运行在32 MHz左右,否则就不能保证功能以及时序上的正确性。因此,FPGA原型验证在性能上要低于ASIC平台。采取的方式是:在ARM7平台上测试功能,在ARM9平台上测试性能。采用ARM9芯片时,系统可以运行在100 MHz左右,完全满足系统整体性能的要求。板级系统的可扩展性有助于解决在验证过程中的某些问题。

经过充分的验证,本系统实现了基于FPGA原型验证平台的GPS基带芯片的导航定位功能。

[1]ANTTI I.FPGA prototyping:untapping potential within the multimillion-gate system-on-chip design space,2005,133-136.

[2]LIN Yi Li,YOUNG Chung Ping,Alvin W.Y.Su,Versatile PC/FPGA-based verification/fast prototyping platform with multimedia Applications.IEEE Transactions on Instrumentation and Measurement,2007,56(6).

[3]HU Tsung Yu,CHEN Liang Bi,HUANG Ing-Jer.An efficient HW/SW integrated verification methodology for 3D Graphics SoC development.The 13thIEEE International Symposium on Consumer Electronics,2009.

[4]LINDA E.M,LUIS A.P,JEFFREY P.System-on-Chip design and implementation.IEEE Transactions on Education,2009.

[5]张开明,王新安,张国新,等.WLAN SoC芯片BX501的FPGA验证平台设计与实现.微电子学与计算机,2006,23(1):97-102.

[6]窦建华,孙强,陆俊峰.基于JTAG和FPGA的嵌入式SoC验证系统设计与实现.合肥工业大学学报,2009,32(3):336~339.