基于挠性覆铜箔的平面无源集成LC单元设计

2010-08-12于宝青杨玉岗

于宝青,杨玉岗

(辽宁工程技术大学电气工程学院,辽宁葫芦岛125105)

随着信息产业及其带来的消费类电子产品的迅速发展,为电力电子行业带来巨大的市场,在通信、计算机以及各种移动设备中,都需要大量的电力电子变流器。大多数电力电子变换器中无源器件占据了变换器很大的体积,提高开关频率可以减小储能元件的体积。分立型的电感电容通常体积大,元件较多,空间利用率不高,阻碍了功率密度的提高。通过电磁作用将电感、电容、变压器集成为一个模块可以克服这些缺点。

电感器与电容器集成技术是利用电感绕组之间的寄生电容作为部分电路参数实现部分电路功能。为了增大电感绕组之间的寄生电容,可以通过特殊结构(如平面绕组结构)或者增大介质材料的介电常数(选用具有较大介电常数的介质材料)。电感与电容集成后为一个器件,即为LC单元。

VANWYK J D教授在磁元件与电容元件集成方面开展了大量的工作,提出电感器-电感器-电容器-变压器(L-L-C-T)集成结构,电感电容集成结构作为原边绕组,铜箔作为副边绕组。为了增大变压器漏感作为谐振电感,在原边绕组和副边绕组之间加入一层低磁导率的磁性材料作为“漏感层”来调节漏感,整体采用平面结构,可以减小无源元件的总体积和高度,提高变流器功率密度。这种结构采用的是EI型磁芯。

[1]中提出了基于柔性多层带材绕组的集成EMI滤波器结构,采用介电常数较低、温度和频率稳定性好的薄膜电介质材料来实现电容,克服了增大电容的困难。但所占据空间的体积仍然比较大,不符合现代开关电源的“短、小、轻、薄”的发展趋势。参考文献[2]中的平面PCB绕组电感电容集成结构,虽然可以减小磁芯的高度和尺寸,绕在EI型磁芯上可以实现很大的电感,但磁芯中柱也占据了很大面积。综合参考文献[1]和参考文献[2]的思路,在现有实验条件下,本文提出了一种基于多层挠性覆铜箔交错并联的平面集成LC结构,采用CI型磁芯,实现了串联谐振、并联谐振集成,最后测试了样机的谐振点并与pspice软件的仿真结果进行了比较,得出集成的平面LC单元有效性和可行性的结论。

1 集成结构的设计

1.1 多层交错并联集成单元的设计

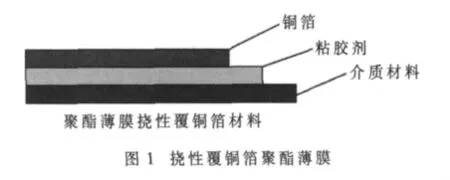

集成LC单元材料选用挠性覆铜箔聚酯薄膜。挠性覆铜箔薄膜[3]是一种由金属导体材料和介电基片,通过胶粘剂经热压粘结的复合材料。这种产品可以随意卷绕,挠性覆铜箔材质比较薄,适合多层交错并联结构。本文采用的是聚酯薄膜挠性覆铜箔材料。如图1所示的挠性覆铜箔材质,其上层为50 μm的铜箔,中间为25 μm的粘胶剂,下层为50 μm电介质材料,该电介质材料是聚酯薄膜,介电常数为3。

图2为单层集成结构及其串/并联等效电路图,将聚酯薄膜裁剪成如图2(a)形状,两片紧压叠放。上下两面铜箔形成电感,位于中间的介质材料与上下两面的铜箔形成电容,因此形成了电感和电容的集成结构,如图2(b)。这样的结构可以同时得到确定的电感、电容,即通电后既有磁场储能,也有电场储能,并通过适当的连接方式与外电路相连,可以等效为串联谐振或并联谐振电路。当把端点A、D与外电路连接时,B、C两端悬空,形成电感、电容的串联谐振形式;当端点A、D与外电路连接,B、C两端直接相连接时,即形成了电感、电容的并联谐振形式,其等效电路如图2(c)所示。

本文提出了一种基于多层挠性覆铜箔交错并联的平面集成LC结构,实现了串/并联谐振的集成。如同图2制作方式一样,共裁剪8片这样的形状,把它们层叠、紧压,能够实现交错并联集成的LC单元结构,这种结构能灵活增大电容,如图3(a)所示,其等效电路如图3(b)所示。同样也是4个端子的LC单元结构,可以制作多个这样的集成LC单元,按照参考文献[2]提到的多个单元连接结构还可以根据不同电感值和电容值的需要,对多个单元进行大电感大电容、大电感小电容、小电感大电容、小电感小电容的串/并联连接来实现。进一步增加了集成电感值和电容值的灵活性。

本文先制作2个四层交错并联集成的LC单元。采用CI型磁芯,节省了EI型磁芯的磁芯中柱,增大了电容面积。将与CI型磁芯相应的电路板挖空,然后把每个集成LC单元的4个引脚焊接到电路板上,2个单元之间的引线可以从电路板上走线,磁芯扣在LC单元上,既可以节省整体无源器件所占空间体积,还可以增大磁芯的散热面积。若想增大电感值,当给集成LC单元通电时,所有集成LC单元电流的方向应该是一个方向,比如每个集成LC单元都从A、D端输入,从B、C端输出,连接方式可以在电路板上实现;而若想减小电感值,可以使若干集成LC单元电流流向相反,即从B、C端输入,从A、D端输出。结构示意图如图4所示。

1.2 电容的计算

式中,ε0为真空中的介电常数(8.854×10-12F/m),εr为介质相对介电常数,w为铜箔的面积(m2),d为介质的厚度(m)。

由式(1)可以看出,如果需要增加更大的电容C,有3种途径:(1)增大电介质材料的相对介电常数εr;(2)增大平面绕组的铜箔面积w;(3)减少电介质材料的厚度d。

若增加更大的电容,采用交错并联方式[1]优势即可显现出来,如图2(b)所示,假如每个单元由n片这样的结构叠加成图3(a)的结构,可以推导出电容C的计算公式:

计算电容时,先计算一个集成LC单元的电容量,根据参考文献[2],多个单元根据需要可通过不同的连接方式得到不同的电容值。

1.3 电感的计算

式中,μ0为真空中的磁导率(4π×10-7N/A2),μeff为磁芯的有效相对磁导率,Ae为磁芯的有效截面积(mm2),Le为磁芯的有效磁路长度(m),Lg为磁芯的空气隙(m)。

同样在计算电感时,先计算一个集成LC单元的电感量,根据参考文献[2],多个单元根据需要可通过不同的连接方式得到不同的电感值。

2 仿真和实验

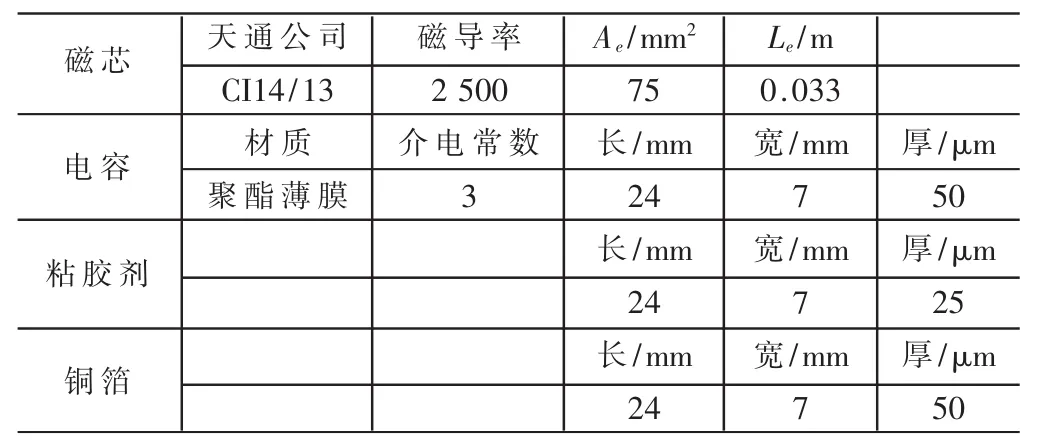

本文制作了一台基于交错并联挠性覆铜箔材料的集成谐振LC单元样机,如图5所示。该样机选用天通公司的CI14/13磁芯;集成LC单元的材料选用咸阳众鑫电子材料有限公司的挠性覆铜箔聚酯薄膜。具体参数如表1所示。

表1 样机的材料和参数

集成LC单元的制作方式如图3所示,制作的2个四层集成LC单元,测得每个集成LC单元的电感值为3.6 μH,电容值为0.37 nF,按照参考文献[2]中大电感大电容的串联方式连接计算得到电感为14.3 μH、电容为0.83 nF。按照大电感大电容的并联方式连接得到电感值为57.1 μH、电容为0.21 nF,样机计算的参数如表2所示。

表2 样机的计算测量及实验结果

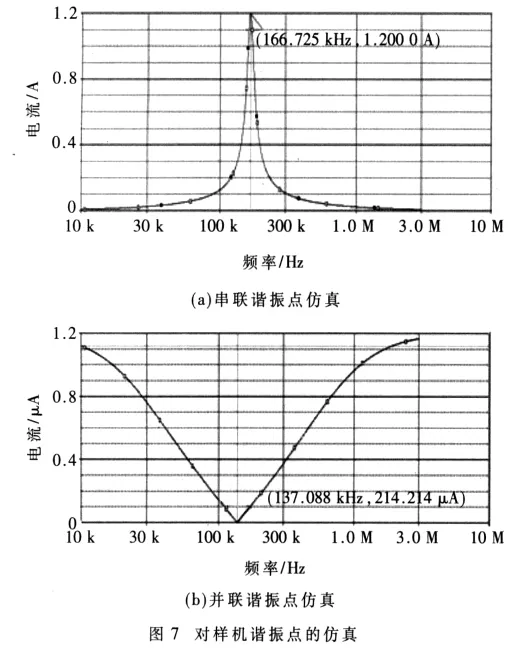

由于介电常数较小、集成的电容值小,但所集成的器件计算出来的谐振频率比较大,频率达到几MHz以上。实验用的仪器为洤华仪器有限公司的3 255自动电子零件分析仪,可以测得的最高谐振频率为200 kHz。所以在实际测量时需要额外增加辅助电感和电容使它们的谐振频率在200 kHz以下。附加的电感和电容如图6(a)所示,串联结构的集成LC中2个单元电感值为15 μH,电容值为0.75 nF,计算集成器件的谐振频率是1.52 MHz。在集成LC单元串联结构中附加串联了80 μH电感和10 nF的电容后,集成器件的谐振频率实际测量为160 kHz。

同样实验测量并联结构的集成LC中2个单元的电感值为60 μH,电容值为0.2 nF,计算集成器件的谐振频率是1.45 MHz,如图6(b)在集成LC单元并联结构中附加并联了22 nF的电容后,实际测量集成器件的谐振频率为140 kHz。实际仪器所测量的加了辅助电感、电容的串联谐振和并联谐振的谐振点的值如表2所示。

对附加后的串联集成结构和并联集成结构进行了PSPICE仿真,仿真曲线如图7所示,串联谐振频率为166.725 kHz,并联谐振频率为137.088 kHz。所得的结果与实际测量的结果接近,证明样机设计比较符合预期效果。如果选用比较高的介电常数,如Y5V、X7R等材料,能够得到几百nF甚至μF级别以上的电容值,可以不用再附加电感和电容。

本文提出的一种新型的集成LC结构,是基于挠性覆铜箔多层交错的多个单元的集成结构,并且可以放到CI型磁芯里。制作了样机并对其参数进行了实验验证,实验结果表明此实现方法的有效性。这种结构可以放到各种谐振变换器的电路中作为谐振部分。如果选用高磁导率的CI型磁芯或选用大的CI型磁芯,可进一步提高电感值,选用比较高的介电常数,可进一步提高电容值,这两方面的提高对于无源集成更有现实意义。通过对层数和单元数的调整,以及不同单元的连接方式,可以得到不同的电感值和电容值,对于无源元件的选值更具有灵活性。

参考文献

[1]伍晓峰,温志伟,徐德鸿.一种基于柔性多层带材绕组的集成EMI滤波器结构[C].第三届中国高校电力电子与电力传动学术年会,2009.

[2]ZHAO L.Generalized frequency plane model of integrated electromagnetic power passives[M].Doctor of Philosophy in Electrical Engineering,2004.

[3]辜信实.印刷电路用覆铜箔层压[M].北京:化学工业出版社,2002.