DVI数字视频图像数据的实时截取方法

2010-08-10龙在云

龙在云,武 斌

(河北建筑工程学院,河北 张家口 075024)

1 引言

液晶、等离子、LED全彩屏等数字平板显示系统已得到广泛应用,数字视频接口(Digital Visual Interface,DVI)可以把计算机、数码摄像机的显示数据直接输出到平板显示系统,相比于模拟传输,节省了模数转换环节,不会造成信号损失,从而保证了图像的清晰度、色彩保真度。但是未经处理的数字视频数据流量很大,如1 024×768 24 bit@60 Hz的动态图像,传输总带宽超过1.6 GHz。对这样的图像数据进行实时截取和传输,需要专门的高速硬件电路,本设计采用FPGA进行缓冲降频实现图像实时截取。

2 图像数据的截取缓冲方案

DVI可提供2组TMDS (Transition Minimized Differential Signaling)连接,每组3个通道,每通道带宽可达165 MHz。当采用1组TMDS连接时,最大可提供60 Hz,1 600×1 200 的 UXGA 信号或 85 Hz,1 280×1 024 的SXGA信号所需带宽。DVI接口支持即插即用,且在无外接设备时是关闭的。若需打开接口取得图像数据,则DVI接口电路需提供必要的即插即用信息。DVI接口适用EDID与DDC2B协议,DDC2B协议包含了显示器的重要信息,包括厂家、型号、屏幕分辨力、最大刷新率、连接模式等。这些信息存于I2C接口的E2PROM中,电路接入后,上位机开始读取E2PROM中得数据,经两次确认后,输出显示数据。

DVI数字视频数据流量大,频率高,需要高速硬件处理来实现任意截屏,同时对通信传输速率要求很高,通常采用光纤通道传输。

DVI数据有5%的行场开销(模拟视频达20%),利用这个时间可以充分地对行列记数,达到动态实时截取的要求。充分利用场同步、行同步和输入时钟可以使系统统计像素位置属性。并把它与指令要求对比,属于截取区域的则立即存储,否则将抛弃。

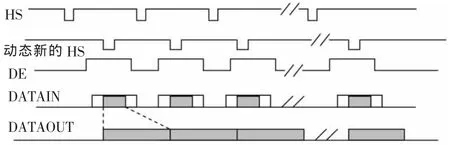

如果实际图像截取时总是等于或小于总行数和总列数,那么就可以利用空闲时间进行缓冲,并以相同或较低频率读出、驱动到传输设备,而不会发生数据丢失或拥堵。如图1所示,1 024×768@60 Hz的DVI点时钟pclk为65 MHz,若每行只输出每行640点,则最低可降频至35 MHz读出,例如在1 024×768的图像中,截取640×480的图像,在帧频和位宽不变的情况下,截取输出的数据量只有原来的2/5,这大大降低了对通信设备的要求。

对于某些设计,也可采用利用外部双体SRAM组成帧缓冲器,读写交替工作,帧缓冲引入1帧的时间延迟,适用于实时性要求不高的情况,充分利用无用行空闲时间进一步降低通信要求。

图1 按行组成数据包

3 硬件系统组成

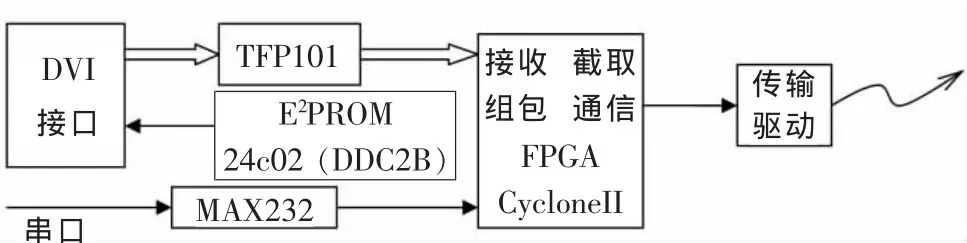

DVI数字视频图像数据实时截取硬件系统电路图如图2所示。

图2 电路组成框图

TI公司的TFP101只有1组TMDS连接,兼容DVI1.0规范。EP2C5-208是CycloneII系列FPGA芯片,内部资源丰富,适合数字视频数据的读写控制器逻辑设计。在FPGA中集成了51单片机内核,用于与上位机通信,接收控制指令如截屏数据、图像处理要求、上位机DVI接口数据格式等。E2PROM存储显示设备系统信息,用于完成即插即用功能。通信采用了1.2 Gbit安捷伦光驱动模块,传输驱动接口逻辑与其对应。

4 逻辑设计

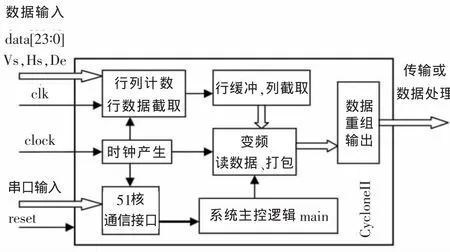

逻辑模块按功能分为主控模块、读写控制模块、行缓冲存储模块、通信数据接收模块、数据输出模块等。FPGA逻辑设计框图见图3。

图3 逻辑功能模块框图

主控模块负责其他模块的协调和调用,接收51内核传送的指令,并存储于内部指令寄存器,指令包括DVI各种数据模式设置、截屏起始点数据、组包方式、图像处理要求等,每次通信结束后的第一个帧同步到来时更新数据。其中通信模块负责与51内核接口,接收上位机的数据指令。

数据写模块用于接收TFP101送来的数据,在每一帧内记录行列点数,并动态地随截取数据生成的新的列同步(见图1),行同步随着截取列位置的变化而变化,当符合截取要求的行数据到来时,将该行写入行缓存。

读模块在新的列同步、新的读出时钟触发下,动态控制其读起点、终点,并按照上位机指令要求添加包头,读出所需的数据组成数据包,并驱动输出到传输模块,在读写模块控制下工作。数据高速写入,微小延时后变频读出,逻辑设计应确保不发生读写冲突,读出的数据要在下一行新数据写入前处理完成。

行缓冲模块调用片内EAB构成双口RAM,执行FIFO操作,在VerilogHDL文本程序编辑时,需要把EAB资源转化成具体的实例加以引用。

逻辑采用VerilogHDL进行核心模块设计,主控模块main.v、数据写模块write.v、读模块read.v、通信模块com.v、传输驱动drive.v、内嵌EAB模块均包含在顶层模块top.v之中。

5 小结

笔者介绍的数字视频图像的高速实时截取方法,节省了外部RAM,提高了系统可靠性,降低了硬件开销,是一种实用、低成本、有效的解决方案,已在LED显示屏和视频监控系统中应用,效果良好,达到预期目的。

[1]武斌,夏宇闻.数字视频信号的长线传输[J].电子技术应用,2003,29(1):62-65.

[2]武斌,龙在云,魏建新.基于页结构的视频数据交织读写控制器设计[J].电视技术,2008,32(5):17-18.

[3]倪琳琳,武斌,黄夔夔,等.低帧频,无闪烁LED全彩屏逻辑设计[J].电子产品世界,2003(4):29-31.

[4]夏宇闻.VerilogHDL数字系统设计教程[M].北京:高教出版社,2003.

[5]武斌,龙在云.LED全彩屏的系统设计[J].河北建工学院学报,2003(1):21-24.