基于FPGA的实时数据采集与处理系统

2010-07-17王旭柱

闫 君 王旭柱

(1、中国海洋大学信息科学与工程学院信号与信息处理,山东 青岛 266100 2、中国海洋大学信息科学与工程学院电子系,山东 青岛 266100)

1 引言

伴随着科技的发展和数据采集系统的应用,对数据采集与信号采集系统的各项指标提出了越来越多的要求,它广泛应用于雷达、通信、遥测遥感等领域。传统方法通常采用单片机或者DSP作为核心芯片,由于单片机的时钟频率相对较低,运行软件的时间占采用时间很大的比例,很难适应高速采集系统的要求。DSP运行速度虽然快,但是不能够完成外围的硬件逻辑控制。FPGA时钟频率相对比较高,延时小,FPGA采用IP内核技术,可以集成外围控制和接口电路。该系统主要应用于基于激发荧光和激光多普勒技术的浮游植物粒径分布现场在线监测系统中的数据采集部分,具有较强信号处理能力和较大数据吞吐量 ,在信号捕获,测量,分析系统中具有广泛实用性。

2 系统硬件结构

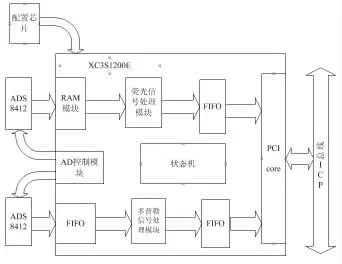

FPGA芯片采用Xilinx公司的Spartan3E系列中的XC3S1200EFG320,为实现高速双通道采用采用了TI公司的具有 Ref引脚和伪双极全差动输入的 16位 2MSPS并行ADS8412。该系统大体分为数据采集单元,数据处理单元,逻辑时序控制单元,主机通信单元,以及电源模块。系统总体结构框图如下:

该系统可完成两路中频信号的采样处理,单路信号加入到到模数转换器中,ADS1605将模拟信号转换为16bit的数字信号。通过FPGA的地址译码分时选通AD1和AD2实现双通道的由AD到FPGA内部RAM和FIFO模块的。相应的信号处理算法在FPGA内部模块中实现。系统总体结构框图如下:

3 模拟ADC设计

ADS8412是德州仪器公司推出的一款2Msps采样速率的16位逐次逼近(SAR)模数转换器(ADC)。采用P8/P16并行输出,带有内部时钟和基准电压源,无丢失码,2MHz采样频率时的功耗为 175mW,SNR为 90dB。ADS8412是单极单端输入范围,有16位和8位可选择接口,零等待时间,高速并行接口,8位/16位总线传输,48引脚TQFP封装,转换时钟由芯片内部产生,360ms的转换时间可保护2MHz的数据吞吐,模拟输入信号由+IN和-I两个引脚提供,本设计采用16位的总线输出

4 FPGA以及外围芯片电路设计

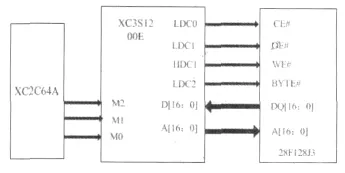

Spartan-3E型FPGA,是Xilinx在SP3基础上,针对用户针对用户对更低成本的需要推出的低成本优化FPGA,主要满足要求有效逻辑和大量资源的逻辑集成、DSP协处理器和嵌入式控制等应用。该系统大约需要500K空间的存储,因此选择XC3S1200E这一款的芯片,芯片的各个内核时钟信号均是利用DCM来实现的配置方式采用主并行配置方式,FPGA驱动PROM CLK,这种配置方式需要分别设置FPGA 中 M0、M1、M2 管脚为“0”、“1”、“0”,采用128Mbit的NOR型的并行Flash,配置方式通过CPLD XC2C64控制来实现的。

5 PCI接口电路部分

PCI接口接口电路可以采用PCI专用的接口芯片,也可利用PCI软核,该系统利用Xilinx提供的PCI core来完成PCI总线控制器的设计。这样不需要考虑PCI控制器的内部时序,缩短设计周期。

6 数据流程

由于本系统应用中要求对两个通道中的数据采取不同处理方式。AD1采集荧光信号,AD2采集多普勒信号。当系统启动后两个通道都开始采样进行2K的数据循环采样,于此同时对一通道中的数据进行50个数据累加检测,当发现50个数据的和大于事先计算好的触发门限时,两个通道都开始进行6K的采样,由于保存了触发前的两个通道的2K数据,所以最后两个通道中的数据都为8K,最后对一通道的8K采样信号求最大值和最小值,计算出中间值,通过对一通道中的数据进行搜索,与中间值进行比较得到其下标地址,从而得出脉冲的两个中值之间的宽度。 在第二个通道中对采集的8K数据进行快速傅里叶变换得到第二通道的频谱,最后将以上计算后得到的数据上传到主机进行显示。

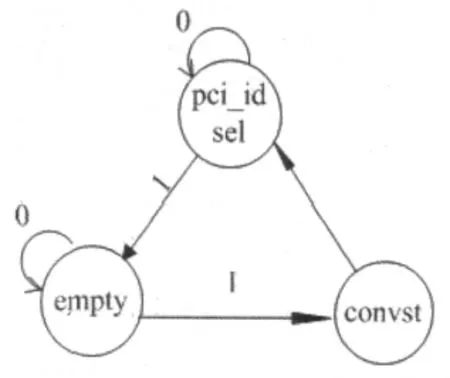

7 状态机结构图

8 结束语

本文主要介绍了基于芯片FPGA XC3S1 200E的数据采集PCI卡,通过了以上工作开发了适用于中频速度的具有广泛适应性的数据采集卡。本文的创新点在于利用FPGA内部模块来实现数据处理的设计,采用Verilog生成的状态机分别控制各个模块有序的连接,在实际应用中根据执行任务不同可以随时更换软核模块,增强了系统的灵活性。

[1]朱冰莲,刘学刚.FPGA实现流水线结构的FFT 处理器,重庆大学学报。2004(9):33-36

[2]Fast Fourier Transform Data Sheet.Xilinx.Inc.2003.

[3]吴德鸣,陆达.高速通信中基于FPGA的PCI总线接口研究与设计,计算机应用。2005.7.

[4]周俊容.高速数据采集系统,电子工程师2005.5.

[5]连冰,宫丰奎,张力等.基于FPGA的快速傅里叶变换,国外电子元器件,2003(12):26-28.

[6]薛小刚,葛毅敏.Xilinx ISE 9.X FPGA/CPLD设计指南。人民邮电出版社。2007年8月.