基于阈值电压差原理的CMOS电压基准源

2010-07-02刘诗斌

叶 侃,刘诗斌

(西北工业大学 电子信息学院,陕西 西安710129)

基准电压源是集成电路中的重要模块,广泛应用于各种模拟、数字、数模混合电路中,特别是在A/D、D/A转换等系统中,其稳定性与准确性直接影响整个系统的精度。传统电压基准源通常采用“带隙”技术。由于双极性晶体管的Vbe具有负温度特性,而工作在不同电流密度下的Vbe之差则具有正温度特性,两者相互补偿可得到与温度无关的输出电压[1]。

加工成本低、周期短等特点使CMOS工艺逐渐成为电路设计中的主流。由于寄生纵向晶体管无法在CMOS工艺中实现,有些学者提出了纯MOS管的电压基准源设计方案:利用MOS管的亚阈值区工作原理设计基准[2];利用载流子与阈值电压在不同温度下的特性设计基准[3];利用 NMOS、PMOS管不同阈值电压设计基准[4]等,但它们存在温度性能较差或电源电压调整率较大的缺陷。本文在分析文献[4]基本原理的基础上,发现电路中的电流源是影响电压基准源的重要因素,针对温度系数和输出电压变化率性能矛盾,设计了一种和式电流并将它作为基于阈值电压差电路中的电流源,在得到良好的输出电压变化率的同时,提高了电压基准源的温度性能。

1 基本原理

实现一个电压基准,首先需要找到一个稳定的电压单元。例如,二极管电压基准电路中的齐纳击穿和带隙电压。在CMOS工艺中,阈值电压就是一个稳定的电压单元。阈值电压的特性依赖加工过程,且对环境温度的变化敏感,因此,需要找一个相对的量值来抵消这些变化。而PMOS与NMOS的阈值电压变化趋势相同,可以通过两者相减的方式得到一个稳定的电压。

图1为基于阈值电压差的电压基准电路原理图,输出电压基准Vref为P管与N管栅源电压VGS之差:

图1 CMOS电压基准电路基本原理

对于CMOS器件,阈值电压VTH与载流子迁移率μ是受温度影响的主要参量。阈值电压与环境温度有近似线性的关系[5]:

其中,VTH(T0)为温度T0时的阈值电压;αvt是阈值电压的温度系数,其值介于 1 mV/℃到 4 mV/℃之间,且 P管大于N管。载流子迁移率与温度的关系:

式中,μ(T0)为温度 T0时的载流子迁移率,且m的值介于 1~2.5 之间[5]。 将(2)、(3)式代入(1)式,(W/L)N和(W/L)P取适当值,令(1)式对温度的导数为零,便能得到与温度无关的输出电压。同时,由于(1)式中各参数均与电源电压无关,输出电压不随电源电压变化而变化,因此,理论上这种电路结构可以实现电压基准源。然而,图(1)中的Ia、Ib为理想电流源,既与环境温度无关,又不随电源电压变化而变化,而在实际应用中电流源的实现通常既是电源电压的函数,又与温度相关。本文通过不同性质电流相加的形式,设计了一种与电源电压无关,与环境温度成反比的和式电流,得到了一种同时具有低温度系数和低输出电压变化率电压基准源。

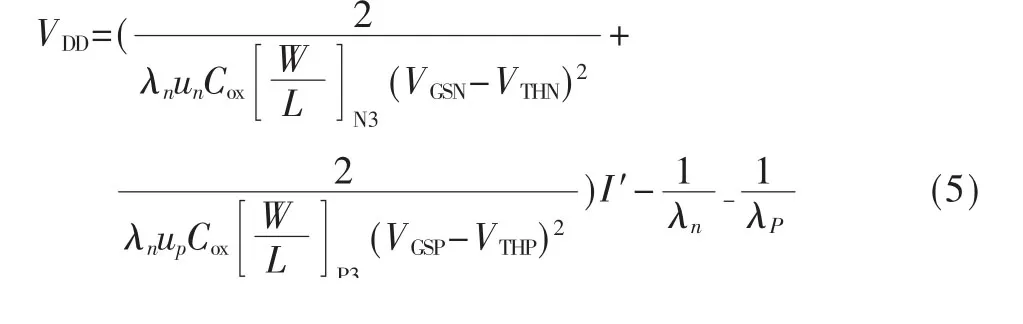

2 新型CMOS电压基准电路

该电路由和式电流模块与核心模块组成。为防止电路在零稳定点而不能正常工作,还应加入启动电路。许多论文中都有关于启动电路的详尽描述,这里不再进行讨论。

2.1 设计思路

由于无法同时调和温度性能和电压输出变化率这对矛盾,所以必须以其中一个作为改进方向。(1)式中除电流外均与电源电压无关,而对温度而言,除电流外,阈值电压VTH和载流子迁移率μ都是温度的函数。显然,选择减少电源电压对输出的影响作为和式电流的改进目标,即能满足对输出电压变化率的设计需要,同时还能兼顾电路对温度性能的要求。反之,若将温度性能做为改进对象,电路可以得到较好的温度性能,但是电源电压对输出电压的影响却不可控。实验证明,在相同的电源电压工作范围内后者的输出电压变化率为前者的十几倍,而且温度系数提高并不明显。根据以上分析可得,一个与电源电压无关的恒流源,虽然其与环境温度的关系待定,但都可利用此关系在一定程度上优化文献[4]的设计(文献[4]中忽略了温度变化对电流的影响)。

由于简单偏置电路的电流与电源电压成正比,且根据MOS管栅源电压几乎不随电源电压变化的特性可以得到一个不随电源电压变化的电流,则通过此两者相减容易得到一个与电源电压成反比的电流,再将其与偏置电路电流按一定比例相加,即可实现一种与电源电压无关的电流设计。在此基础上,可具体解析得到该和式电流与环境温度的函数关系式,然后对(1)式中的参数进行合理设置,从而改善电路的温度性能。

2.2 电源电压对输出的影响

图2为本文所设计的新型CMOS电压基准整体电路图。如图所示,和式电流模块中,自举偏置电路(由MOS管 P3、P4、N3、N4和电阻 R2构成)产生偏置电流。 当电源电压变化时,沟道调制效应是影响输出电流的主要因素[6]。忽略体效应,只考虑沟道调制效应,流经P3的电流:

式中,λ为沟道长度调制系数。且电源电压可表示为N3和 P3管的VDS之和:

栅源电压几乎不随电源电压变化而变化,忽略电源电压对栅源电压的影响,且(5)式中其他参数均与电源电压无关,偏置电流与电源电压可以表述为线性关系。I1与I3是偏置电路的镜像电流,设:

式中,IA0为电源电压V0时流过P2的电流,a为漏电流的电压系数。同时,栅源电压不变使流经电阻R1的电流IR1不变,因此流经P7的电流可表示为:

图2 新型CMOS电压基准电路

式中,IB0=IR1-IA0,又 I3、I4分别与 I1、I2对应成比例,得到和式电流 I5:

式中 K1、K2分别为 P5、P8对 P2、P7宽长比比值。 取 K1、K2的值相等,即可得与电源电压无关的和式电流。同理,P5、P8与P6、P9的宽长比对应相等, 流经 N5的电流与 I5成正比,因而(1)式中电流与电源电压无关,得到了与电源电压无关的输出电压。

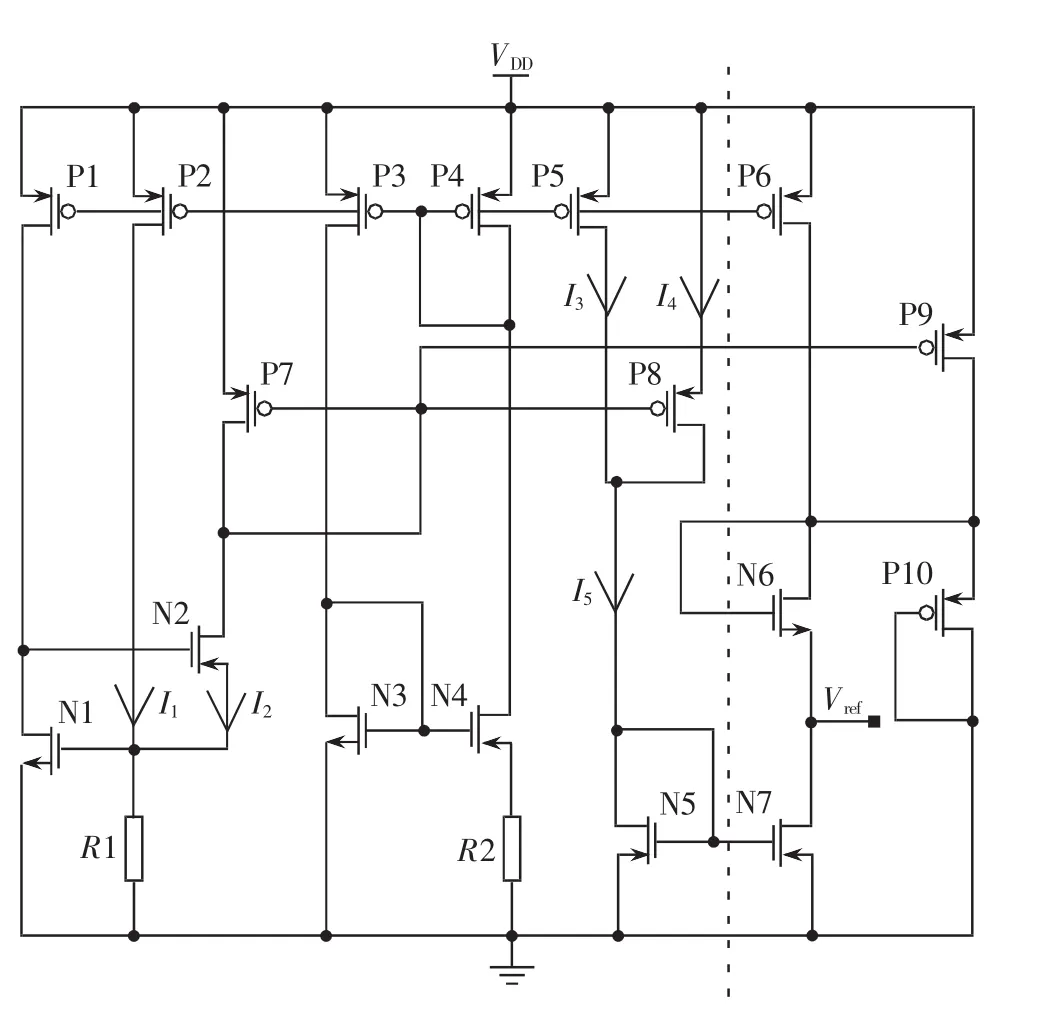

2.3 环境温度对输出的影响

自举偏置电路产生PTAT电流[7],流经P2的电流可表示为:

式中,IT0表示温度T0时的电流值,a为漏电流的温度系数。考虑环境温度对N1管的栅源电压影响:

式(10)中 IP1、μn、VTH都是温度的函数,且

式中,K3为 P1管对 P2管的宽长比。 将(11)、(2)、(3)式代入(10)式,令其对温度求导可得:

可在某极点温度TS得到栅源电压的最大值。当温度高于TS时,栅源电压随温度升高而下降,其特性可近似为线性变化。栅源电压可表示为:

式中,VGSTS表示环境温度TS时的栅源电压,β为栅源电压的温度系数。比较温度变化对栅源电压和电阻的影响,后者随温度的变化可忽略。和式电流I5可表示为:

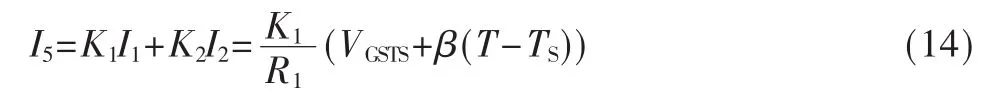

同理,(1)式中的电流 Ia、Ib与 I5成正比,即与环境温度成反比。将(14)、(2)、(3)式代入(1)式中,得到输出电压对温度T的导数:

式中A、B分别表示为 Ia、Ib应对 I5的比例系数。因而,同时考虑MOS管长宽比和电流Ia、Ib的设置,才能得到较好的温度性能。

3 仿真与分析

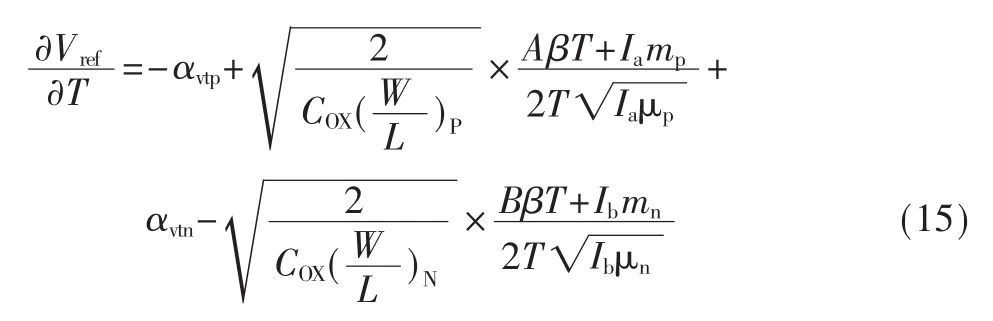

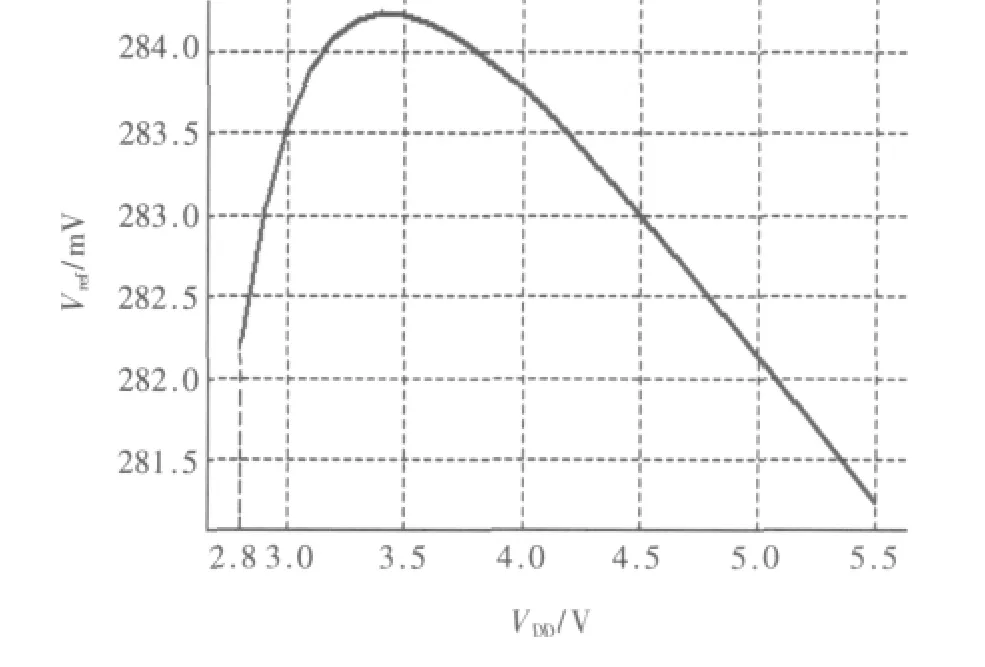

在 0.6 μm CMOS工艺下,采用Hspice软件进行仿真,得出:在25℃下对电源电压在 2.8 V~5.5 V的范围内进行直流扫描,基准电压曲线如图3所示。在3 V电源电压下对温度在-30℃~80℃的范围内进行直流扫描,基准电压曲线如图4所示。环境温度25℃、电源电压为3 V时,输出基准电压为283.5 mV。基准电压不到300 mV,可使用比例放大器进行适当放大,以满足不同需要。

图3 基准电压Vref电源电压特性曲线

图4 基准电压Vref温度特性曲线

由于和式电流模块中得到与电源电压成反比的部分拉高了工作电源电压值,但电源电压能在宽范围(2.8 V~5.5 V)内工作,且输出电压波动小于 3 mV,得到输出电压变化率1.11 mV/V,满足实际应用需求。

温度系数是电压基准源最主要的参数指标。由图4可以看出,环境温度20℃~30℃时的温度系数约为零,而且有较好的对称性。且在温度-30℃~80℃的范围内,温度系数为41.5 ppm/℃,较文献[4]有了很大改进。

与文献中提到的电压基准电路的主要指标进行比较,结果如表1所示。

表1 温度性能参数比较

比较结果表明,本文的电路实现结构能够在较宽的范围内工作,且同时满足对低温度系数和低输出电压变化率的要求。

[1]YTTERDAL T.CMOS bandgap voltage reference circuit for supply voltages down to 0.6 V[J].Electronics Letters,2003,39(20):1427-1428.

[2]HUANG Po Hsuan,LIN Hong Chin,LIN Yen Tai.A simple subthreshold CMOS voltage reference circuit with channellength modulation compensation[J].IEEE Transaction on Circuits and System-II:Express Briefs,2006,53(9):882-885.

[3]WANG Jian Ping,LAI Xin Quan,LI Yu Shan.A novel low-voltage low-power CMOS voltage reference based on subthreshold MOSFETs[C].The 6thinternational conference on ASIC(ASICON′05),2005:369-373.

[4]KONG Ming,GUO Jian Min,ZHANG Ke,et al.A novel CMOS voltage reference based on threshold voltage difference between p-type and n-type MOSFETs[J].Chinese Jouranl of Semiconductors,2007,28(10):1546-1550.

[5]TOLEDO L,LANCIONI W,PETRASHIN P.A new CMOS voltage reference scheme based on Vth-difference principle[C].IEEE International Symposium on Circuits and Systems(ISCAS′07),2007:3840-3843.

[6]RAZAVI B.模拟 CMOS集成电路设计[M].陈贵灿译.西安:西安交通大学出版社,2003.

[7]彭伟,谢海情,邓欢.一种新型高精度 CMOS电压基准源[J].电子器件,2007,30(3):863-865.