基于Altera IP核的RS译码器的设计与实现

2010-06-28刘学苏建峰孙婷

刘学,苏建峰,孙婷

基于Altera IP核的RS译码器的设计与实现

刘学1,2,苏建峰1,孙婷3

(1. 中国科学院国家授时中心,西安 710600;2. 中国科学院研究生院,北京 100039;3. 西安电子科技大学,西安 710071)

介绍了一种基于Altera公司提供的Reed-Solomon IP(intellectual property)核来实现RS译码功能的设计方法,该方法具有开发周期短、系统成本低以及稳定可靠特点。主要分析了Altera公司提供的IP核工作原理、参数配置以及接口设计,最后通过时序仿真验证了该设计的正确性。该设计方法已经成功应用于BPL长波接收机数据解调模块中。

RS码;IP核;现场可编程门阵列(FPGA)

RS(Reed-Solomon)码是一类具有很强纠错能力的多进制BCH码。RS码编解码结构相对简单,具有同时对突发错误和随机错误进行纠错的能力,因而广泛应用于数据通信和数据存储系统的差错控制中。在工程实现中,可用专门的硬件芯片或DSP(数字信号处理)芯片实现RS译码功能。

在中国科学院国家授时中心主持的“BPL长波授时系统现代化改造”项目中,对原有BPL系统进行加发时间信息编码设计,在发播端需对时码数据信息进行RS编码以保证信息的正确传输,因此需要在接收机数据解调中进行RS译码设计。由于接收机设计主要由Altera公司提供的FPGA芯片实现,因此在设计中考虑利用IP核实现RS译码功能。

基于以上背景,本文分析了Altera公司的RS IP核的原理,配置了译码参数,设计了译码器接口,给出了适合接收机的配置和使用方式,并应用该设计在FPGA中进行验证,实现了RS译码器。利用IP核实现译码功能,使接收机数据解调系统集成在一个FPGA芯片内,不仅降低了接口设计的复杂度,而且工程上实现成本低,运行稳定可靠,便于后期调试和修改。

1 RS译码原理

RS译码算法主要分为时域译码和频域译码。频域译码对于某些码长的RS码会获得更快的译码速度,但由于增加了时域与频域的变换和反变换以及相应的存储延时模块,需要消耗更多的资源,因此本文中采用时域译码方案。时域译码的关键步骤为错误位置及错误值多项式的求解,工程上常用的算法为修正的欧几里德算法 MEA(modified euclidean algorithm),其算法描述如下[3]:

1)根据接收到的码多项式计算伴随式;

2)采用MasseyFSR算法,确定错误位置多项式;

3)采用Chien搜索法,寻找错误位置;

4)计算错误值。

2 FPGA中RS译码方案设计

2.1 IP核介绍

Altera公司的Reed-Solomon v8.0 IP核能提供RS编译码算法,并且算法配置采用全参数化。Reed-Solomon v8.0 IP核支持包括Cyclone、Stratix在内的所有Altera的主流FPGA产品。Reed-Solomon v8.0会自动把缓冲计算中间变量的存储器块综合到M4K单元上,提高了RS编译码器的数据吞吐量和执行速度[3]。

2.2 译码器设计

译码器设计的关键环节是译码参数配置和译码器接口设计。根据RS译码原理、RS译码IP核参数约束以及项目设计要求,译码器中需要配置的参数及方法如下(以RS(15,9)码为例):

每个码组的监督码码元数根据实际工作需要可灵活设置。

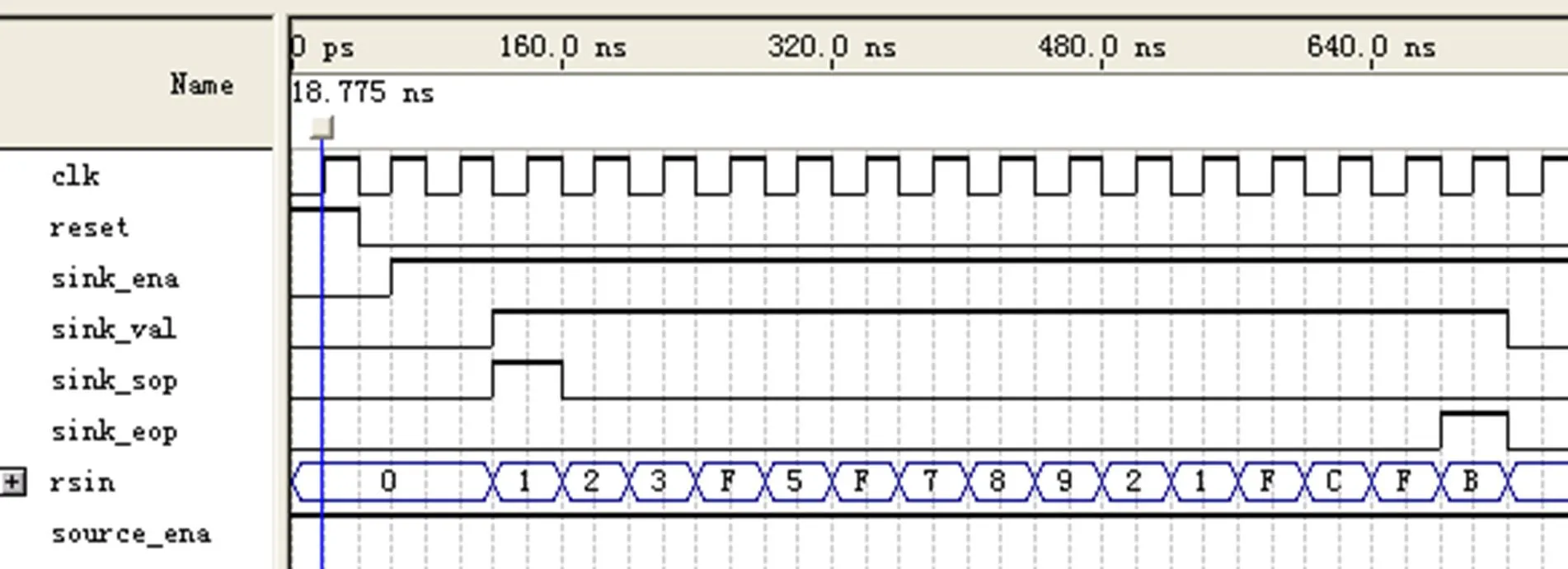

在译码参数设置成功后,需要进行译码器接口设计。译码器输入输出端口如图1所示:clk为时钟信号,上升沿有效;reset为复位信号,异步复位;rsin[4..1]为四位总线输入数据;sink_val表示数据有效;sink_sop和sink_eop分别表示一组数据的开始和结尾;source_ena系统运行使能信号,为“1”时表示当前模块可以运行且可以输出数据,为“0”时系统保存当前编码值,不输出数据;rout[4..1]为四位总线输出数据;sink_ena是输入使能信号,当它为“1”时表示当前模块可以接收数据,为“0”时表示不能接收数据;source_val表示数据有效;source_sop和source_eop分别表示一组数据的开始和结尾。

译码器的工作流程为:当source_ena为高时,编码器开始工作。sink_ena为高,可以接收输入数据;当sink_val为高时,数据有效,同时开始接收数据;当sink_eop为高时,一组数据发送结束,此次接收数据结束,等待下一次接收信号开始。

图1 RS译码器模块

3 仿真验证

项目中采用的是Altera公司的EP1C12Q芯片,该芯片属于Cyclone系列[4]。该设计已经在QuartusII环境下全编译,占用EP1C6Q中的5个引脚(4%),共使用了1 398个逻辑单元(23%),4 096 bit的存储单元(4%)。从使用情况来看,占用的逻辑单元和存储单元很少,适合大部分的FPGA器件。利用QuartusII进行时序仿真,波形如图2所示。编码模式下,当输入信息码元(1,2,3,4,5,6,7,8,9)时,输出编码码组为(1,2,3,4,5,6,7,8,9,2,1,3,C,F,B)。译码模式下,当接收码组中含错误码元时,如图2所示,其中信息码元出错2个,监督码元出错1个,通过译码后得到码组仍然为(1,2,3,4,5,6,7,8,9,2,1,3,C,F,B),表明译码器成功纠错,译码正确。

4 结语

本文探讨了利用Altera公司提供的IP核实现RS译码功能的设计方法,该设计方法已经应用在BPL接收机数据解调模块中。文中讨论的RS译码方法不仅缩短了开发周期,降低了实现的复杂度和系统成本,而且稳定可靠,集成度高,便于调试和修改。这种方法同时适用于数字定位技术中RS检错纠错系统[5]。需要说明的是,在今后工作中如果参考此方案,需要根据不同的RS码参数以及生成多项式进行参数配置以及对接口进行取舍。

[1] BERLEKAMP E R. Algebraic Coding Theory[M]. New York: McGraw Hill Book Corporation, 1968: 134-168.

[2] Altera. Reed-Solomon Compiler User Guide[Z]. California: Altera, 2006.

[3] 王新梅, 肖国镇. 纠错码: 原理与方法[M]. 西安: 西安电子科技大学出版社, 2002.

[4] 孙航. Xilinx可编程逻辑器件的高级应用与设计技巧[M]. 北京: 电子工业出版社, 2004.

[5] 向渝, 华宇, 吴海涛. 基于数字锁相环的GPS可驯钟系统研究[J]. 时间频率学报, 2008, 31(1): 50-55.

Design and Implementation of a RS Decoder Based on Altera’s IP Core

LIU Xue1,2, SU Jian-feng1, SUN Ting3

(1. National Time Service Center, Chinese Academy of Sciences, Xi’an 710600, China;2. Graduate University of Chinese Academy of Sciences, Beijing 100039, China;3. Xidian University, Xi’an 710071, China)

This paper introduces an Altera’s Reed-Solomon IP core to achieve the RS decoding function, and the method is characterized by short development cycle, low cost and reliability. This paper analyzes the principle of Altera company’s IP core, parameter configuration and interface designing, and verifies the correctness of the design through the timing simulation. This design method has been successfully applied to the data demodulation of BPL long wave receiver module.

RS code; IP core; FPGA(field programmable gate array)

2009-08-01

刘学,男,硕士,主要从事卫星导航技术的研究。

TN76

A

1674-0637(2010)01-0028-04