高速电路信号完整性探讨

2010-06-28黄震

黄 震

(船舶重工集团公司723 所,扬州225001)

0 引 言

随着高速数字系统的不断发展,电子系统中信号的频率已经从几十兆赫兹增加到几百兆赫兹,甚至达到几吉赫兹。本文针对由高速信号带来的反射、回流、串扰、电磁感应(EMI )等信号完整性问题进行一些探讨。

1 高速信号的定义

对于低速信号来说,一般考虑比较多的是静态电阻,设计系统时很少考虑走线的分布电感和分布电容。对于低速信号来说,传输线路就是一个点;对于高速信号,线路上各个点的电位是不同的,系统对输入的信号脉冲的响应是沿走线分布的,设计系统时更多的是考虑分布电感和分布电容,于是引入传输线概念及与传输线相关的一个概念——特征阻抗Z0。传输线等效模型如图1 所示。

点P是传输线上任意点,作为虚拟分界面将传输线分开,从右往左看过去,R1、L1、C1分别是线路的等效电阻、电感、电容。R2是因为漏电流的存在所体现的电阻,其阻值接近无限大;而传输线静态电阻R1很小,也可忽略不计。这种情况下传输线特征阻抗可以简化为:

这是无损情况下的特征阻抗公式。

图1 传输线等效模型

高速信号指的是上升沿和下降沿速度变化很快的信号。高频信号一定是高速信号,但是低频信号也可能是高速信号。只要是上升沿和下降沿的速度很快,即使频率很低,也是高速信号(某些芯片的参考时钟对沿的要求达到纳秒级;由高频信号分出的低频信号,其沿与高频信号是一致的)。业界有一个通用的定义:对于某信号,10%~90%的上升和下降时间为Tr,该信号在印制电路板(PCB)上走线的延迟为D,该信号的电气特性有效长度为L:

当信号在导线上传输的端到端时延大于L/6时,必须使用传输线理论。也就是说当传输距离到达一定程度才考虑使用传输线理论,否则认为该段线路只是一个点,信号作为普通信号处理。

2 信号完整性分析及解决办法

信号完整性是系统可靠性的保证。由于高速信号中包含了极高频率的成分,系统的电气参数发生了很大的变化,产生了许多高速电路特有的问题,包括反射、信号回流、串扰等。

2.1 反射

由于阻抗不匹配,在系统中会发生信号的反射,其反射系数为:

式中:Z0为特征阻抗;Z为负载阻抗。

由于反射信号和正常信号的叠加,使得接收端的信号劣化,影响对电平的判决,严重的话甚至会损坏接收器件。反射现象通常可以划分为源端反射、末端反射和传输线内部反射3 种。

在传输线上,只要特征阻抗没有变化,就不会有反射。PCB 板上的某一根线,从宏观上看是均匀的;但是从微观上看,肯定是凹凸不平的。从这个意义上来看,反射总是存在的,在设计过程中就要注意信号的电气特性有效长度和布线的技巧,保证阻抗变化引起的反射对信号完整性的影响降到最低。

比如,对于低速信号并不特别在意信号线是否在同一层,是否在某一段粗细不一致,也不会在意PCB 上的走线是否均匀,是否打过孔,但是对于高速信号来说,就必须关注这些问题。10GHz 信号不建议放在PCB 的内层,因为PCB 的内层走线比起外层来说更加凹凸不平。为了使频率特性更好,甚至采用10GHz 信号线镀金的方法来使走线更加均匀。在高速信号传输的背板上可以考虑采用背钻工艺,减小“树桩效应”等等。

根据集成电路输出阻抗为0,输入阻抗无穷大的原理,传输线的两端如果不加处理,必然会有反射发生。在接收端,以晶体管-晶体管逻辑(TTL)电路为例,接收端是晶体管的基极,而基极电流是极其微弱的,因此传输线的末端等效为一个无穷大的电阻RL,负载电阻与传输线特征阻抗不匹配,信号在这个点将会发生全反射,反射波一直传回源端。

如果源端内阻与传输线阻抗不匹配,在源端会发生二次反射,如此反复n 次反射。如果这个n 次反射信号叠加到原信号上,将导致信号劣化。解决方案是在发射端串接电阻来吸收二次反射,原则就是让源端的串阻加上源端内阻的阻值正好和传输线特征阻抗相等。

2.2 回流

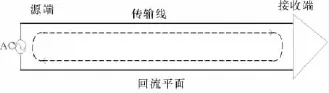

任何一个信号,最终都要形成一个闭环回路,如图2 所示。

图2 信号的回流

通常情况下是地平面作为回流平面,因此在PCB 设计的时候,信号层要与地平面相邻。当然对于板内的信号来说,也可以采用电源平面作为回流平面,但是必须特别注意电源平面的完整性。

对于一个交流信号来说,信号的回流总是选择阻抗最小的回路做为回流,如果信号与回流信号所形成的面积越小,那么干扰和抗干扰能力就越好。因为当回路面积越小,回路所能接收到的干扰就越少,同时向外的辐射就会越小。

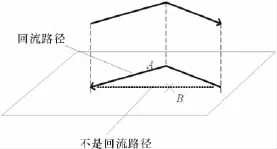

在现实的PCB 设计中,一个信号线不可能很直,必然拐弯抹角,见图3 。

图3 信号的回流

从路径的角度来说,当然是B 路径最短,直流电阻也最小;但是从阻抗的角度来说,对于该信号,A路径是阻抗最小的路径,也就是回流路径。

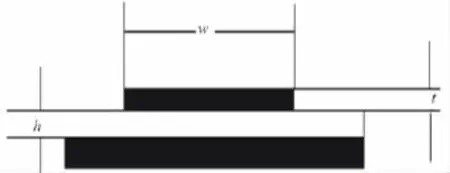

在图4 中,h 其实就是信号线与回流平面(或者说是回流路径)之间的距离,可见,如果以B路径为回流路径的话,那么信号线与回流路径之间的距离将会增大,那么Z0将会增大。而回流路径A是与信号最近的,即Z0最小。

在PCB 设计的过程中经常要关注信号完整性,其中重要的一点就是回流平面要完整,如果回流平面出现如图5 的分割,将会导致信号的回流面积变大,那么该信号受到干扰的可能性就很大。

图4 微带线剖面图

图5 不恰当的回流平面

2.3 串扰

随着电子技术的不断发展,在高速电路中信号频率变高、边沿变陡、电路板尺寸变小、布线密度变大,串扰已经成为信号完整性中的一个重要问题。串扰是指有害信号从一个网络转移到另一个网络,在数字设计中普遍存在,有可能出现在芯片、PCB板、连接器、芯片封装和连接器电缆等器件上。如果串扰超过一定的限度就会引起电路的误触发,导致系统无法正常工作。

影响串扰大小的因素有很多,限于篇幅,在这里只介绍一些解决方案,这些方案是通过理论计算、仿真和系统调试时的经验得出的。

串扰的解决方案:

(1)在情况允许的情况下,尽量增大走线之间的距离,减小平行走线的长度,必要时采用jog 方式走线。

(2)在确保信号时序的情况下,尽可能选择上升沿和下降沿速度更慢的器件,使电场和磁场变化的速度变慢,从而降低串扰。

(3)设计PCB 叠层时,在满足阻抗要求的前提下,应该尽量使导体靠近地平面或电源平面。这样可以使信号路径与地平面紧密耦合,减小信号线与回流线构成的面积,减少对相邻信号线的干扰。

(4)在布线空间允许的条件下,在串扰较严重的2 条信号线之间插入1 条地线,可以减小2 条信号线间的耦合,进而减小串扰,这里需要注意的是在该地线上多打一些孔,保证该地线与地平面的耦合,否则就失去了隔离作用,严重时甚至变成了一根天线。

EMI 是任何电子设备都不能避免的问题,由于高速电路中含有大量极高频的成分,EMI 现象尤其要引起重视。遵循上面论述的3 点正确处理电路设计,对EMI 有很好的抑制作用,适当的匹配减少了信号的反射,减少了EMI 的发射源;优化信号与回流构成的面积,有效地控制了EMI 的发射与接收;串扰本身就是EMI 的一种形式。

此外,适当的接地,有效的屏蔽(带有托盘的电路板的EMI 性能就要优于没有托盘的电路板),良好的PCB 叠层设计和器件布局,EMI 滤波器和磁性元件的正确选用,都是解决EMI 问题是必须考虑的因素。

3 结束语

高速电路设计是一个复杂的过程,较低速电路而言,往往有许多难以预料的因素影响整个系统的性能。因此,在开发高速系统时必须针对系统的特点广泛考虑各种因素,最终目的是使系统性能达到最优。

[1]Howard Johnson,Martin Graham.高速数字设计[M].沈立,朱来文,陈宏伟,等译.北京:电子工业出版社,2004.

[2]田广锟.高速电路PCB 设计与EMC 技术分析[M].北京:电子工业出版社,2008.

[3]Eric Bogatin.信号完整性分析[M].李玉山,李丽平译.北京:电子工业出版社,2005.