基于DSP Tools的数字中频发射机的设计

2010-06-25冯林浩于鸿洋

冯林浩,于鸿洋,张 萍

(电子科技大学 电子工程学院,四川 成都 610054)

1 引言

在传统的数字信号处理系统的设计中,需要先用Matlab等仿真软件进行建模仿真,得到理想的仿真结果后,再根据仿真过程,使用VHDL等硬件描述语言创建硬件工程,最后完成硬件仿真。这个过程非常复杂,需要花费大量的时间,而且由于软件仿真和硬件仿真不能直接联系,使得调试比较困难。Xilinx公司设计了一种全新的FPGA开发工具DSP Tools,将The MathWorks Matlab的系统级设计工具Simulink和Xilinx公司的FPGA开发工具ISE整合在一起,使得软件仿真和硬件仿真可以同时进行。DSP Tools在算法友好的开发环境中可以帮助设计人员快速生成DSP设计硬件表征,从而缩短了DSP设计周期。已有的Matlab函数和Simulink模块可以和Xilinx DSP Tools模块相结合,将系统级设计和DSP算法开发相链接。DSP Tools通过在Simulink中调用Xilinx的模块和IP核来搭建完整的系统,并使用workspace中的数据进行软件仿真,得到满意的结果后再直接生成硬件代码,下载到硬件中进行测试[1]。在不具备测试条件和环境的情况下,可以进行软硬件协同仿真。

2 基于DSP Tools的DSP系统开发流程

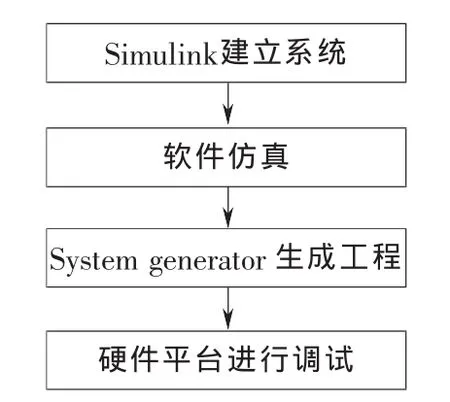

在Simulink中调用各种模块和IP核来搭建特定功能的系统,并创建各种测试向量来完成软件仿真。软件仿真完成后使用System gernerator编译DSP Tools模块生成HDL工程[2]。System generator可以直接生成NGC等网表文件,下载到硬件中进行调试,提高开发的效率;也可以生成HDL代码,以便在需要的时候进行修改,并结合Xilinx ISE等其他开发工具进行仿真、综合、布局、布线。在不存在硬件测试环境的情况下,还可以将硬件平台链接入DSP Tools进行软硬件协同仿真。DSP Tools开发流程如图1所示。

图1 基于DSP Tools的DSP系统开发流程

3 数字中频发射机的设计

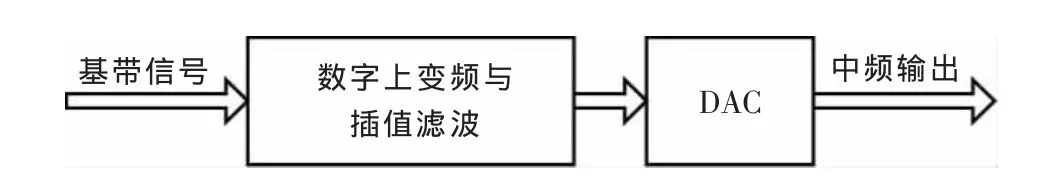

数字中频发射机(Digital-IF transmitter)的框图如图2所示。中频发射系统由高速DAC模块、数字上变频(DUC)模块及插值滤波模块组成。输入的数字基带信号首先经过插值滤波,转换到更高的采样率,然后通过数字上边频,调制到需要的频率上去,最后通过高速DAC模块把数字中频信号转化为模拟中频信号[3]。

图2 数字中频发射系统

数字中频发射系统是对信号在中频进行数字化,在进行频谱的搬移时,要考虑到采样率的变化。一般来说,D/A之前的信号采样率很高,要从基带信号得到这些有用的高速信号,需要有效地对其进行数字上变频、插值、滤波等处理,这些功能可以使用现场可编程门阵列(FPGA)来实现。FPGA具有较高的处理速度和较强的稳定性,同时又具有设计灵活、易于修改和维护的优点,可以适用于不同的系统要求。

在本文设计的数字中频发射系统中,输入正交基带信号,采样率为30 MHz,带宽20 MHz,抽取上边频和滤波模块实现6倍抽取,把采样率变为180 MHz,然后把频谱向上搬移25 MHz。

3.1 基于DSP Tools的数字上边频和插值滤波模块的设计

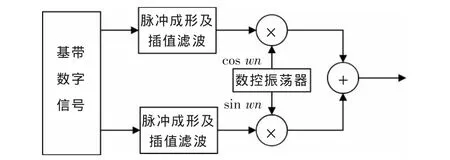

数字上变频克服了模拟上变频中存在的混频器的非线性和模拟本振的频率稳定度、边带、相位噪声、温度漂移、转换速度等问题,其频率步进、频率间隔也具有理想的特性,因而得到了广泛应用,数字上变频原理如图3所示。

图3 数字上变频框图

数字上变频由插值滤波、数控振荡器(NCO)和数字混频器组成,数字基带信号经脉冲成形及插值滤波后得到高采样率的信号,然后输入到数字混频器中与NGC产生的正交本振信号进行混频,最后进行求和运算,得到数字中频信号。

3.2 数控振荡器

数控振荡器是决定数字中频性能的主要因素之一。NCO的目标是产生频率可变的正交正、余弦样本,在FPGA中,NCO一般采用直接数字频率合成(DDS)的方法来实现。DSP Tools的IP库中有高性能的DDS可以直接调用。本设计调用的是DDS v5.0,其自身时钟设为180 MHz,动态范围36 dB,输出正交正余弦信号的频率为25 MHz。

3.3 脉冲成形及插值滤波器的设计

在DUC实现了从复基带(Baseband)信号到实带通(Passband)信号的转换。输入的复基带信号采样率相对较低,通常是数字调制的符号率。基带信号经过滤波,然后被转换成一个更高的采样率,从而调制到NCO的中频载波频率。

基带信号需要首先进行脉冲整形,滤掉带外的杂波,通常由FIR滤波器实现。插值部分(Interpolation)完成信号采样率变化和滤波功能,可以采用CIC和FIR实现。对于一个窄带信号,如果需要进行高倍的采样率变换,那么CIC将是非常合适的,无论是在实现性能或是资源节省方面,CIC都将优于FIR[4]。

在本设计中,基带信号的采样率是30 MHz,中频信号的采样率是180 MHz,只需要6倍的采样率变化,而且信号的带宽是20 MHz,不是窄带信号,因此使用FIR进行插值滤波是更好的选择。

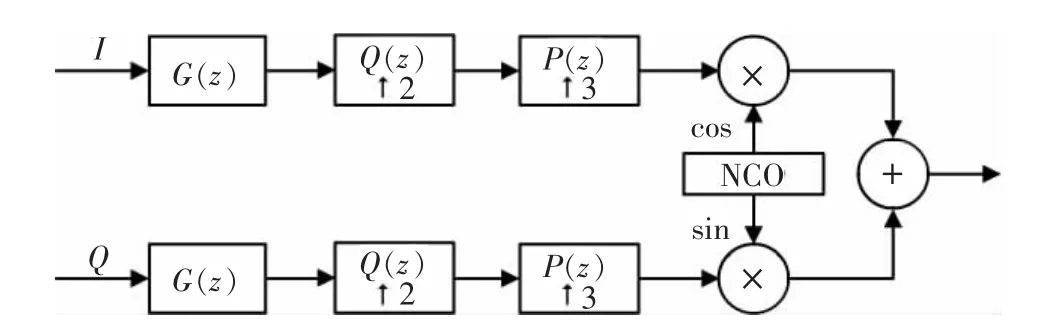

如图4所示,考虑到资源和效率,将整形滤波和抽取插值滤波分为3个FIR来设计:G(z)负责频谱整形,工作频率最低,设计成120阶的根升余弦(RRC)滤波器;Q(z)负责2倍插值滤波,工作频率次之,设计成80阶的低通FIR;P(z)负责3倍插值滤波,工作频率最高,设计成80阶的低通FIR。具体实现上,由于I,Q两路的滤波特性完全一样,为了节省期间资源,将I,Q两路的3级滤波器作复用。

图4 DUC滤波器功能划分

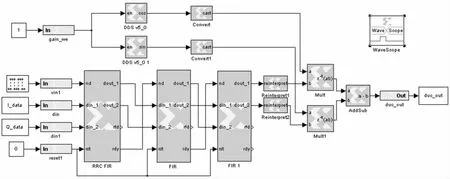

设计滤波器时,首先根据各级滤波器的滤波特性,使用Matlab的滤波器设计工具FDAtool(FilterDesign&Analysis tool)计算出抽取系数并进行量化,然后调用Xilinx的IP核FIR compiler v3.2,对各项参数进行设置并导入量化后的系数,就可以得到理想的FIR滤波器。图5是完整的数字中频发射机原理图。

图5 利用DSP Tools的数字中频发射机原理图

3.4 仿真结果及分析

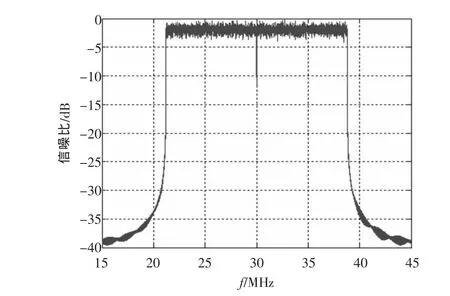

本仿真的输入段是两路基带I/Q信号,采样率30 MHz,带宽20 MHz,通过三级滤波器进行频谱整形及插值滤波后,采样率上升到180 MHz,然后与DDS产生的25 MHz正余弦信号混频,使频谱上移25 MHz。

由图6和图7可以看出,输入的基带信号频谱分布从20~40 MHz,中心频率是30 MHz,输出的中频信号采样率升到180 MHz,频谱分布在195~215 MHz之间,中心频率是205 MHz,相比采样率180 MHz,频谱上移了25 MHz。

4 结论

笔者通过对基于DSP Tools的数字中频发射机的设计实现,详细说明了如何利用DSP Tools在Matlab上设计数字信号处理系统。可实现“可见即可得”的设计方法,各种常用的DSP处理模块,如FIR,DDS,FFT可以直接调用,既方便省事,又能兼顾性能。

图6 输入基带I/Q信号的频谱

图7 输出中频信号的频谱

本文方法可以快速构建DSP系统,并在不具备外部硬件测试平台的情况下,使用JTAG口进行软硬件联合仿真。相对于传统开发方式来说,具有很大的优势。

[1]Xilinx.DSP Tools User Guide[EB/OL].(2009-04-07)[2009-08-09].http∶//www.Xilinx.com.

[2]Xilinx.DSP Tools Reference Manual[EB/OL].(2009-04-07)[2009-08-09].http∶//www.Xilinx.com.

[3]陈宝龙.基于FPGA的数字中频接收机的研究[D].南京:南京理工大学,2008.

[4]王水,吴继华.用 FPGA 实现数字中频[EB/OL].(2009-04-13)[2009-08-09].http∶//www.jdzj.com.