基于FPGA开发的VME总线电机控制系统

2010-06-21王飞葛琼璇王晓新刘洪池

王飞,葛琼璇,王晓新,刘洪池

(中国科学院 电工研究所,北京 100190)

1 引言

随着大功率交流调速系统在钢铁和高速铁路中得到越来越广泛的应用,高可靠性的控制系统成为研究者日益关注的问题。近年来,随着计算机技术和实时操作系统的快速发展,嵌入式系统为工业控制的实时性和可靠性提供了有力的支持。在诸多的嵌入式体系中,基于VME总线的控制系统因其开放性、可靠性和对多种操作系统的支持,占据了广泛的市场,并且被成功地应用于交流调速控制系统中。本文以美国GE公司生产的VME总线单板计算机7750作为核心控制器,利用自行开发的基于FPGA的电机控制板卡实现了一个高性能、低成本的电机控制系统。

开发基于VME总线的电机控制系统主要包括两个部分:总线接口逻辑和变频器脉冲发生器,本文所使用的总线接口为A24D16(即AM=39)的VME slave接口,脉冲发生器则为两电平电压空间矢量调制算法,整个系统基于 FPGA来完成。本文通过将接口逻辑功能和脉冲产生结合在单个FPGA上构成片上系统(system on chip)节省了空间和成本。实验结果表明,本系统具有良好的电机控制效果。

2 VME接口

VME总线规范是由Motorola公司制定的Versabus(逻辑、电气特性)和欧洲的Eurocard标准(机械特性)构成的,是一种开放式系统结构[1]。该系统结构支持多种实时操作系统,如 UNIX、VxWorks等,在控制系统领域具有广泛的市场,并且被成功地应用于交流调速控制系统中。

VME总线包括地址线、数据线和控制线3类,有多种数据传输模式,并且支持块传输和七级中断,数据传输采用主从模式。本文所使用的总线数据格式为24位地址和16位数据宽度。进行数据传输时,首先通过专用的总线控制器来分配机箱中主控制板(Master)对总线的控制权,当Master获得总线控制后,将按照数据格式驱动所要读写的地址、数据以及相应的控制信号线,待电平稳定后通过拉低AS和 DS信号开始对从卡(Slave)进行读/写操作,操作完成后Slave通过DTACK信号示意Master释放对总线的控制。

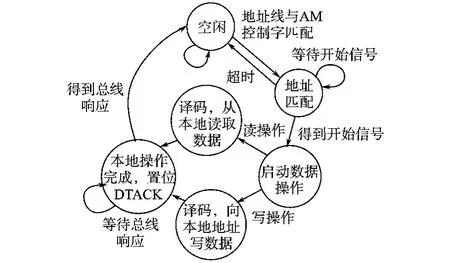

本文中所开发的Slave接口逻辑用Verilog状态机[2]来实现,该状态机各状态及其转换关系如图1所示。

图1 VM E总线Slave接口逻辑状态机Fig.1 State machine for VME slave interface

状态机各个状态的具体操作分别为:1)空闲状态,接口逻辑判断总线的地址信号是否与板卡地址位以及修饰码(AM)相同,FPGA板卡采用的地址和数据线宽为 A24D16,即地址修饰位AM[5∶0]为0x39;2)地址匹配状态,地址判断无误后状态机进入地址匹配状态,在本状态下检测AS和DS信号线来判断是否有Master的数据传输启动信号;3)启动数据操作,判断地址线上的寄存器地址位来确定片选信号以及片上寄存器地址,还将通过读/写信号线来确定数据方向,此后转入读写操作,等待状态读写操作完成后状态机进入结束状态;4)结束状态,接口逻辑拉低DTACK信号线,示意数据操作完成,并监视AS和DS获取Master响应来判断是否继续进行读写操作或者完成操作释放对总线的访问权,Slave接口逻辑进入空闲状态,等待下一次数据传输。

3 基于FPGA的空间矢量调制

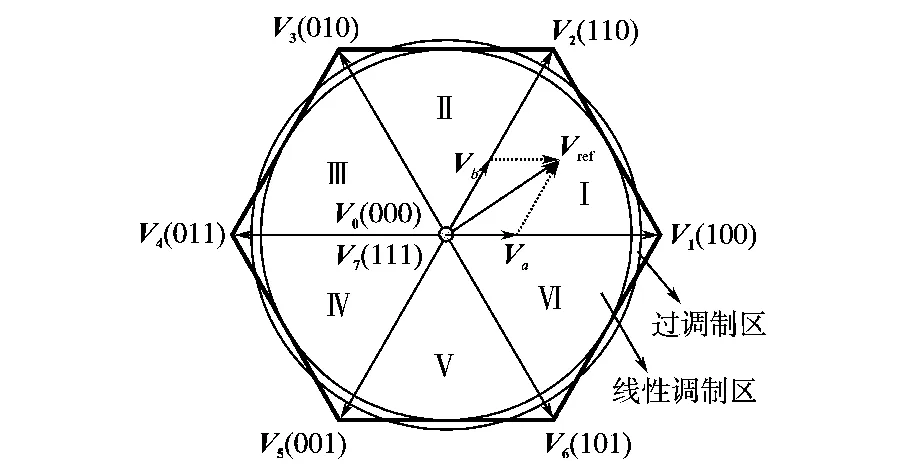

为了使设计的系统具有通用性,合理的划分嵌入式系统的软硬件功能是非常必要的。在本文中,VME主控制器完成数据采集以及控制算法,产生相应的电压控制信号,为电压参考矢量在静止两相坐标系上的分量,见图2。

图2 两电平电压空间矢量Fig.2 2 level voltage space vectors

在通过VME接口逻辑接收到总线数据后,FPGA通过三相两电平电压空间矢量调制产生逆变器驱动信号。

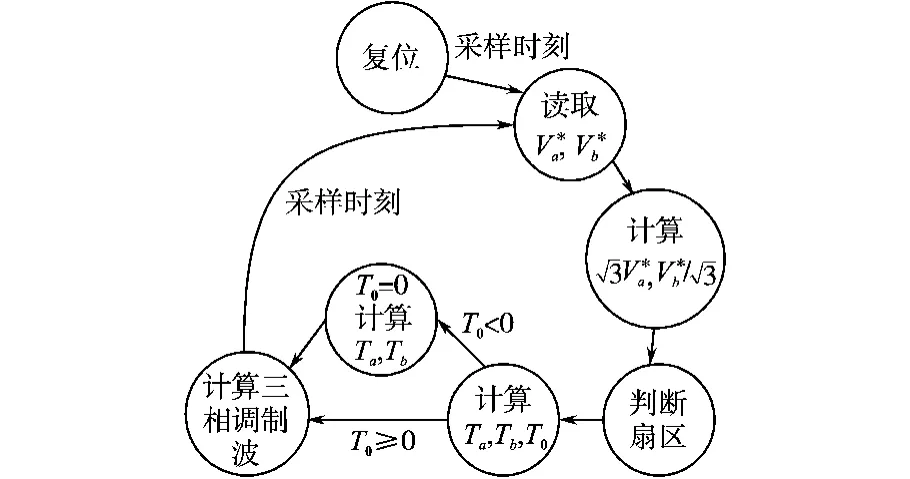

本文利用Verilog语言编写状态机来实现基于FPGA实现的电压空间矢量调制算法。状态机如图3所示。

图3 电压空间矢量调制状态机Fig.3 State machine of SVPWM

具体各个状态描述为:复位,启动后的状态,当接收到运行命令以及到达采样时刻后进入读取数据状态。读取,读取由VME总线传送的数据。由于所采用的FPGA器件只能进行定点运算,所以必须首先规定CPU板卡与FPGA之间数据的格式。上位机产生的电压控制信号进行相应的定标,定标方法为

式中,hcarrier-Δ为三角载波的最大值。

这样定标的好处是可以方便比较计算出来的调制波与载波。

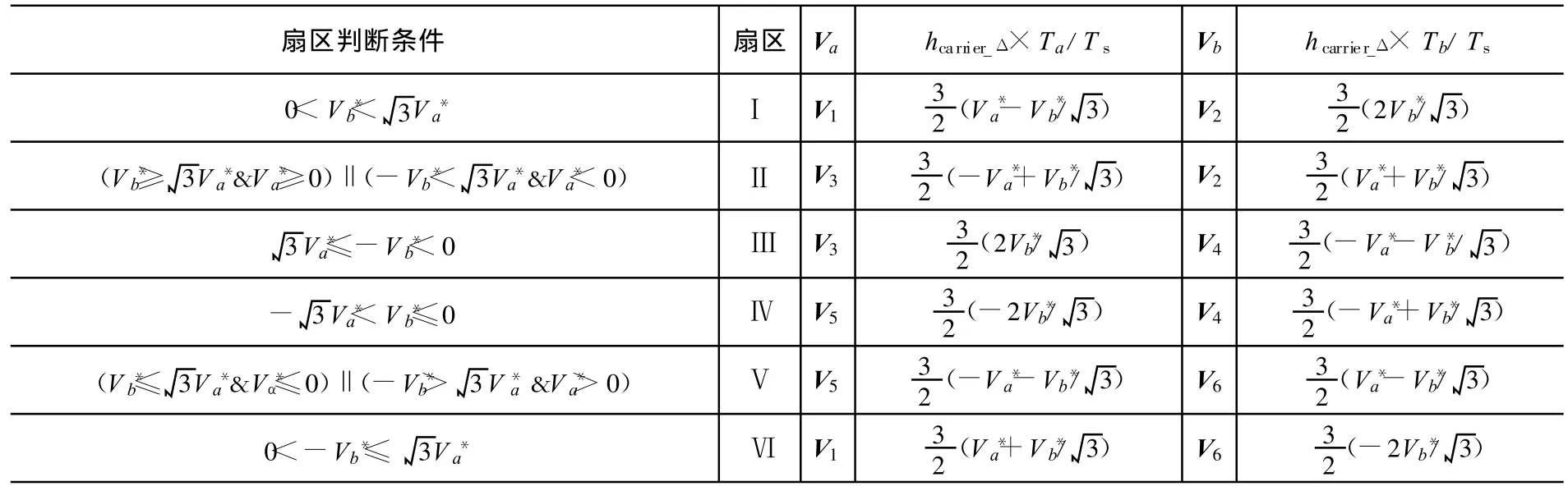

表1 扇区判断,各扇区对应的非零开关状态及其作用时间Tab.1 Secto r judgment,effective voltage vectors and their dwell time applied for each sector

判断扇区,按照表1来判断给定电压矢量所在扇区,并确定用来合成电压指令的非零开关状态Va和Vb。

时间计算,按照伏秒平衡原理一个开关周期内电压指令的作用可以用相邻的两个开关状态合成,表1给出了每个扇区的判断条件,各扇区对应的开关状态及其持续时间,由于V*a和V*b为对应三角载波的定标值,所以计算得到的为Ta和Tb在周期Ts内的定标。用采样周期减去 Ta和Tb则是零矢量的持续时间T0,当开关指令位于线性区(T0>0)则状态机接下来计算调制波并确定开关序列,若T0<0则需要按照过调制的算法重新计算Ta和Tb。

过调制,当调制比大于0.907时空间矢量调制进入超调区域Ⅰ,这时T0<0。为了增加对直流母线电压的利用率,设T0=0并采用以下方程来重新确定Ta和Tb[3]:

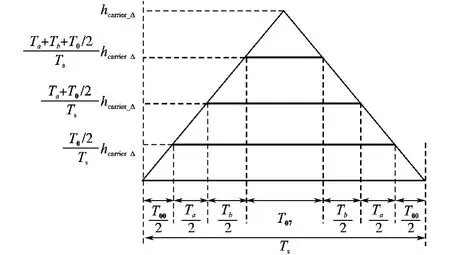

确定调制波,计算的 T0,Ta和Tb决定了2个非零矢量和零矢量分别的持续时间,接着按照调制策略来选择相应的开关序列。本文中开关序列的确定方式采用传统的7段式,如图4所示。

图4 7段式开关状态序列Fig.4 Seven segment switching pattern

4 硬件系统与试验结果

4.1 硬件系统

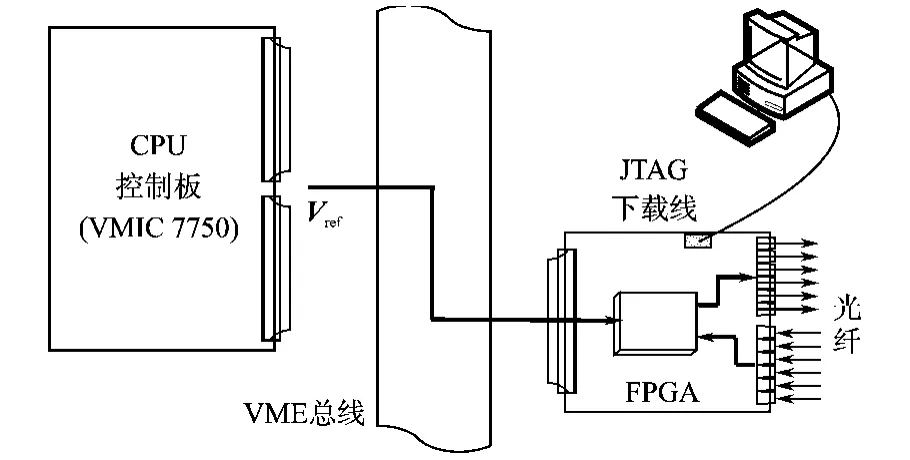

本系统硬件采用美国GE公司的VME总线CPU板卡VMIVME7750,7750配有1.26 GHz Intel Pentium III CPU、128M 内存和Intel 815E芯片组,运行 VxWorks实时操作系统,针对该CPU卡采用的开发工具是IOWorks。FPGA板卡上采用 Xilinx公司SPARTAN 3 xc3s400芯片,开发软件采用 ISE WebPACK 9.2i和Chip Scope评估版本。异步电机的参数为额定电压=380 V,额定功率 =3 kW,额定转速 =2 880 r/min。

控制算法采用开环V/f比控制,开关频率为1 kHz,7750板卡的主要工作是根据速度曲线和设定的V/f比值产生速度指令和与之相对应的电压参考矢量,将该矢量在静止两相坐标系中的分量对母线电压进行定标并分别通过VME总线传递给相应的地址。FPGA板卡的Slave接口逻辑通过总线进行译码并读取电压分量,接着通过空间矢量调制算法输出驱动脉冲来对逆变器进行控制。系统框图如图5所示。

图5 实验系统框图Fig.5 Experimental system diagram

为了方便调试FPGA内部程序的运行,使用了Xilinx公司的ChipScope软件对器件内部寄存器进行采样验证。ChipScope可以将逻辑分析仪软件核(ILA)方便地加入到所开发的模块中,从而可以查看FPGA中任何寄存器变量的值[4]。图6为用ChipScope得到的线性调制(ma=0.8)和超调(ma=0.94)时的三相相电压调制波。采集时ChipScope中的触发脉冲设定为三角调制载波的下溢信号,即当三角波到达0时对调制波进行采样,每采集512次后将数据通过JTAG口传送给PC进行绘图。FPGA寄存器内部的数据由7750板卡通过VME总线写入,从图5可以看出VME接口数据传输准确无误。

图6 FPGA计算得到的调制波波形Fig.6 Modulation waveforms calculated by FPGA

4.2 实验结果

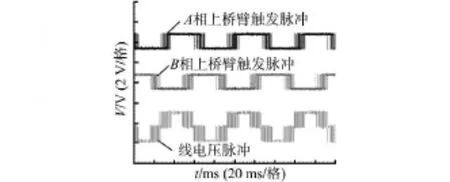

图7和图8分别是线性调制(ma=0.8)和超调(ma=0.94)时由FPGA输出的A相,B相上桥臂的触发脉冲,同时图7、图8中还给出了示波器计算出的线电压波形。

图7 线性调制(ma=0.8)时A,B相上桥臂触发脉冲以及线电压Fig.7 Pulse waveforms for upper legs of phase A,B and line voltage in linear modulation(ma=0.8)

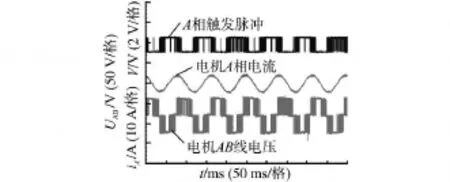

图9为利用本控制器对1台15 kW异步电机的实验结果,图9中由上到下分别为A相上桥臂驱动脉冲,电机A相电流以及AB线电压。由图9可见波形良好,试验结果表明基于FPGA的VME总线电机控制系统可以很好地完成控制任务。

图8 过调制(ma=0.94)时A,B相上桥臂触发脉冲以及线电压Fig.8 Pulse waveforms for upper legs of phase A,B and line voltage in overmodulation(ma=0.94)

图9 异步电机实验波形Fig.9 Induction motor ex periment waveforms

5 结论

本文详细介绍了基于FPGA的VME总线从卡接口和两电平电压空间矢量调制算法,作为研究VME总线交流调速系统的第一阶段成果,本系统具有良好的控制性能,并且大大地节省了系统成本。下一步工作是针对目前的系统开发中断接口,实现高性能的控制算法。

[1]ANSI/IEEE Std 1014-1987.A Versatile Backplane Bus:VMEbus[Z].1987.

[2]Donald E T homas,Philip R Moorby.T he Verilog·Hardware Description Language[M].Springer,1996.

[3]Zhou Zaoy ong,Li Tiecai,Takahashi T,et al.Design of a U-niversal Space Vector PWM Controller Based on FPGA[C]∥Applied Power Electronics Conference and Exposition,APEC2004.Nineteenth Annual IEEE,2004,3:1698-1702.

[4]Xilinx Inc.ChipScope Pro Software and Cores User Guide[Z].2007.