FPGA在大功率多相变频调速系统中的应用

2010-06-06刘东黄进陈高杨家强袁宝成姜海博

刘东, 黄进, 陈高, 杨家强, 袁宝成, 姜海博

(浙江大学电气工程学院,浙江 杭州 310027)

0 引言

随着现代工业的发展,大功率驱动装置的需求日益增加,三相电机是通过增加每相串联绕组匝数,实现高压大功率。利用多电平技术实现高压大功率是解决这一问题的主要途径。但由于器件的串并联,系统的可靠性下降。在电机功率和相电流一定的情况下,电机相数增加可使所需供电电压下降,多相电机正是通过增加电机相数,来实现低压大功率。大功率的多相电机,可采用低压变频器,避免了功率器件的串联带来的静态、动态均压问题。多相逆变器供电的多相电机系统为实现大功率交流调速系统另辟蹊径[1-3]。

随着电机相数增加,PWM驱动信号会成倍增加。例如,一个十五相感应电机变频调速系统需要30路PWM信号[4]。目前,还没有一款商用芯片能提供如此多通道的PWM接口,一些常用的电机专用控制芯片,如TMS320C28335和MC56F8366,至多能提供16路PWM信号。因此,对于类似于上述应用场合,仅采用这些专用芯片来扩展PWM通道,不仅会造成电路设计复杂,可靠性降低,最主要的是很难完成同相功率器件的同步触发,而且需要复杂的控制逻辑。同时,基于软件的DSP或者MCU在实现SPWM/SVPWM触发信号时需要较长的时钟周期,微处理中不确定的中断响应会导致PWM脉冲的相位抖动。

现场可编程门阵列(Field Programmable Gate Array,FPGA)芯片内部包含的逻辑门数从几百到几千万,具有可任意配置的几百个I/O口,并且开发周期短,可灵活配置实现多种功能而无需改动硬件电路[5-6]。本文提出了一种基于 PWM IP核的多路PWM发生器的设计方法,利用搭积木的方法构建多路PWM发生器,并利用FPGA的硬件并行性和可扩展性,设计高频率的三角载波发生器,以提高系统的可靠性和集成度。

1 基于PWM IP核的多路PWM发生器

1.1 通用PWM IP核的构建

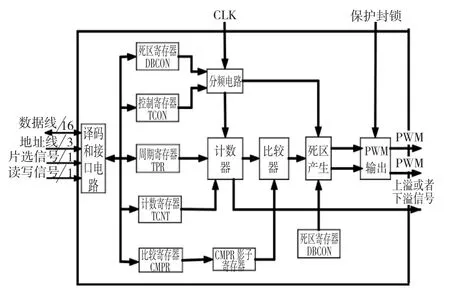

通用PWM IP核是针对不同的应用场合而设计的,应具有较好的可设置性,如开关周期、死区时间、PWM模式以及功率保护等设置。本文采用的PWM IP核与TI公司DSP内部的PWM发生器在功能上基本相同,开关周期和死区时间可进行宽范围设置。只需对IP核内的寄存器进行相应设置,即可产生所需的 PWM 信号,具体结构如图1 所示[7-8]。

图1 通用PWM IP核总体结构Fig.1 Overall architecture of universal PWM IP core

1.2 高频率三角载波发生器

在SPWM调制算法中,载波发生器是其中的核心部分,一般用于产生可逆的三角波。在常用的TI公司用于电机控制的专业DSP处理芯片中,如TMS320C28335,16位采样精确度的可逆三角波时钟主频最高为150 MHz,载波频率为1.14kHz。而FPGA中的主频可比DSP的主频高,例如Altera公司的一款低端FPGA cyclone EP1C6240C6的主频可达405 MHz,因此可产生同等采样精确度下更高频率的可逆三角波,比如300 MHz时钟主频下载波频率可达2.28kHz,从而提高载波频率。然而主频提高,FPGA的时序约束就非常紧张,时序要求很难达到。

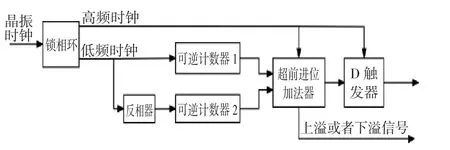

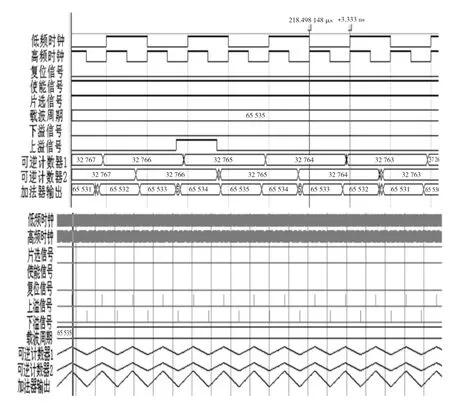

本文采用如图2所示的方法来实现高频率的16位三角载波发生器,晶振时钟通过锁相环倍频产生上升沿或下降沿严格对齐的两路时钟,其中低频时钟频率是高频时钟频率的二分之一。分别采用2个可逆计数器对低频时钟的上升沿和下降沿计数,并将2路计数值在以高频时钟为主频的超前进位加法器中相加,最后经过一个D触发器输出。同时,该载波发生器还在三角波最大值或最小值处产生上溢或下溢信号,作为影子寄存器的加载信号。取晶振时钟为30 MHz,经锁相环产生300 MHz高频时钟和150 MHz低频时钟,其实现的16位高频三角载波发生器后仿真波形如图3所示。

图2 16位高频三角载波发生器原理Fig.2 Principle of the 16-bit high frequency triangular carrier generator

图3 16位高频三角载波发生器后仿真波形Fig.3 Post-simulation waveforms of the 16-bit high frequency triangular carrier generator

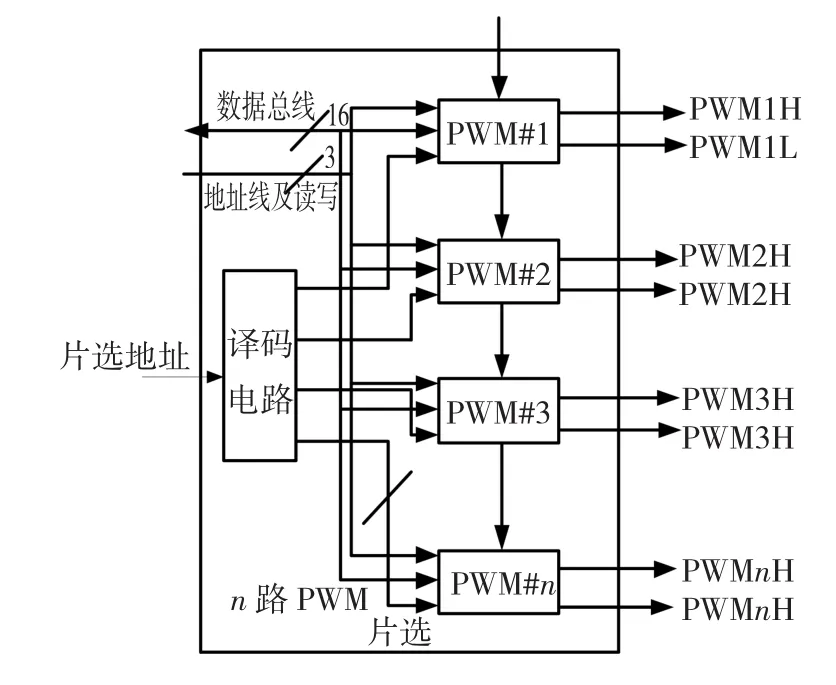

1.3 多路PWM的产生

只要FPGA芯片资源允许,利用PWM IP核以搭积木的方式就能设计出任意数量的PWM发生器。图4为多路PWM基本结构,直接把IP核的数据线、地址线、控制线和时钟线相连,通过一个简单的译码电路产生相应PWM IP核的片选信号,就可调用多个PWM IP核,产生多路PWM信号。

由于每个PWM IP核都有独立的控制寄存器、周期寄存器、死区寄存器,与此同时,所有PWM IP核都共用同一时基,因而每个PWM IP核工作可以完全独立并保持同步,容易实现PWM的各种调制策略。

图4 基于IP核的多路PWM发生器结构Fig.4 Multi-PWM generator configured by PWM IP cores

2 FPGA在多相变频调速系统中的应用

2.1 系统结构及控制策略

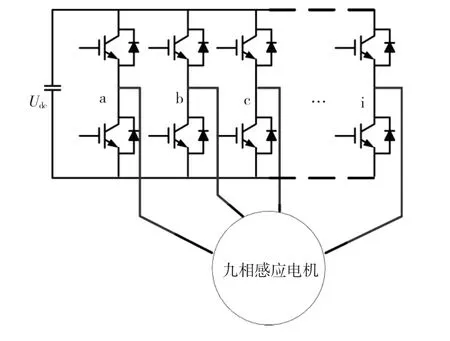

本文构造了一个18路PWM发生器,用于九相感应电机电压源逆变器系统中,其拓扑结构如图5所示,电机绕组星型连接[9]。

图5 九相电压源逆变器拓扑图Fig.5 Topology of a nine-phase voltage sour

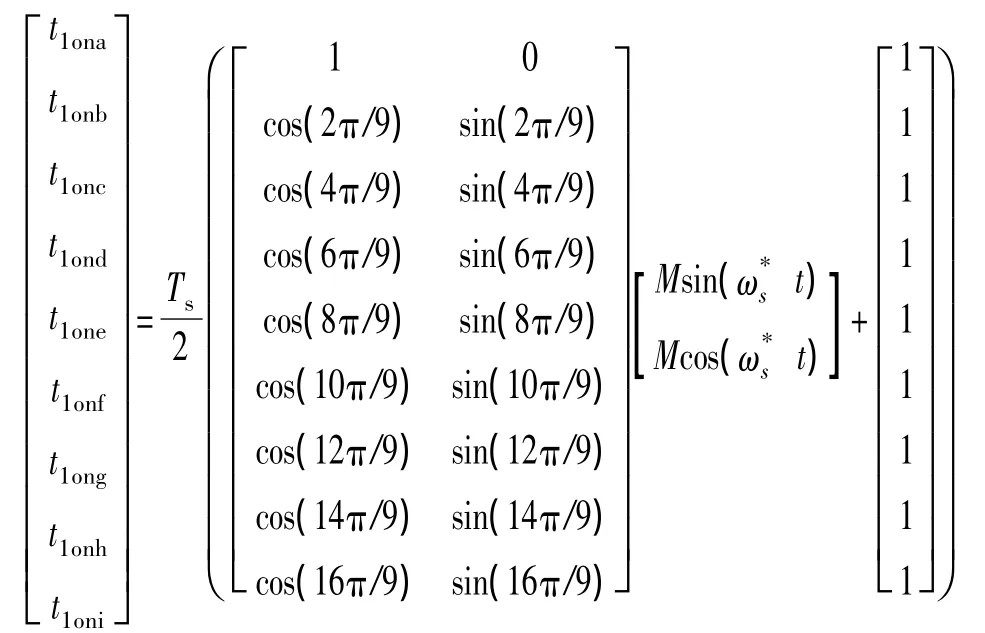

控制策略采取基于SPWM调制的VVVF控制,SPWM采用对称规则采样法,其脉冲宽度可表示为

式中 Ts为采样周期;M 为调制比;[t1ona,t1onb,t1onc,t1ond,t1one,t1onf,t1ong,t1onh,t1oni]为各相 SPWM 脉冲宽度。

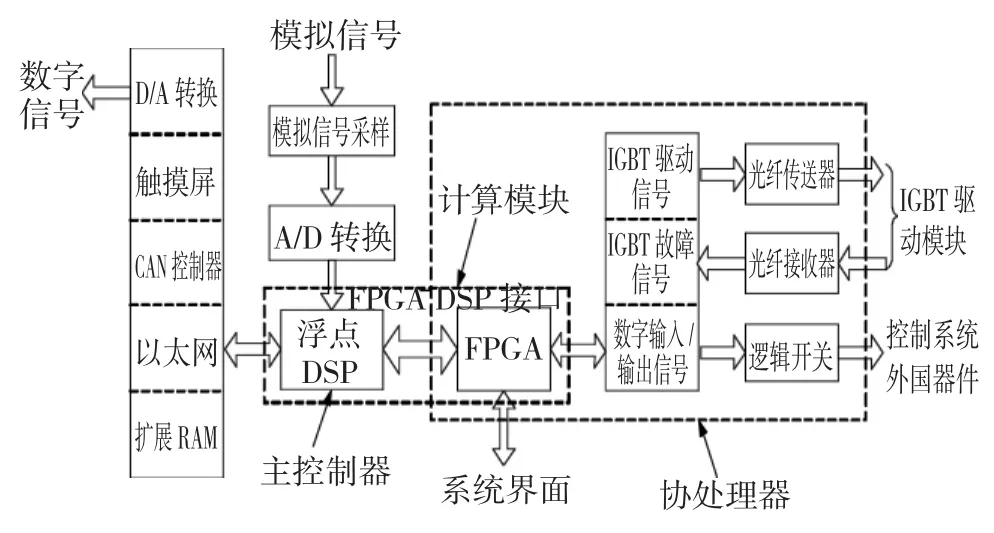

2.2 基于FPGA和DSP的硬件控制平台

变频调速系统的控制平台如图6所示,该平台主要由两部分组成:主控制器和协处理器。主控制器的核心芯片是TI公司一款浮点32位DSP TMS320C28335,外接A/D转换器、D/A转换器、触摸屏、CAN、以太网以及EEPROM等外围控制芯片;协处理器的核心芯片是Altera公司的一款工业级FPGA芯片cyclone EP1C6240C6,外接光纤接收器、光纤发送器、逻辑开关、数字输入输出等外围控制器件。

在该平台中,SPWM参考信号的计算,变频变压控制算法的实现以及与PLC的通讯等任务主要由DSP完成,FPGA则主要完成多相PWM波的产生,系统的故障保护以及数字I/O口扩展等功能。FPGA中载波发生器的上溢和下溢信号作为DSP的外部中断信号,当中断响应后,DSP进行SPWM参考信号计算,并将计算得到的SPWM脉冲宽度通过DMA传输给FPGA,同时从FPGA中读取故障信息和数字I/O口输入状态。

FPGA和DSP共用一个30 MHz的晶振时钟,该时钟通过FPGA内部的锁相环产生两路上升沿或下降沿严格对齐的时钟,其中低频时钟150 MHz,与DSP内部时钟一致,高频时钟300 MHz,用于产生高频率的三角载波,本文采用的调制波频率为50 Hz,三角载波频率为8kHz。

图6 基于FPGA和DSP的控制平台Fig.6 Control platform based on FPGA and DSP

2.3 故障保护及数字I/O口扩展

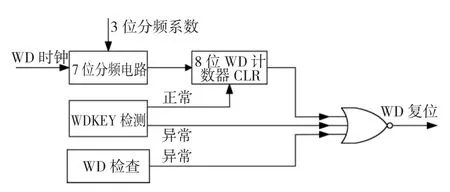

FPGA中的故障保护模块主要由自检保护、看门狗电路以及IGBT故障保护三部分组成。自检保护是指FPGA在上电初始化之后进行自检,验证PWM发生器等模块逻辑是否正确;看门狗电路如图7所示[10],用于检测FPGA是否正常工作,后仿真波形如图8所示;IGBT故障保护是指当IGBT逆变模块出现故障时,FPGA能及时封锁PWM输出,保护系统。

图7 看门狗电路结构框图Fig.7 Block diagram of the watchdog circuit

图8 看门狗电路后仿真波形Fig.8 Post-simulation waveform of the watchdog circuit

由于FPGA具有很多可任意配置的I/O口,可用于数字I/O口和其他外围器件的扩展,可以大大节省DSP的GPIO口,提高系统集成度。

3 实验结果及其分析

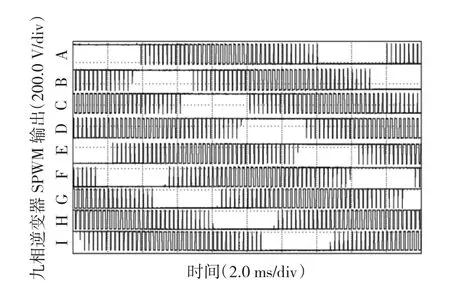

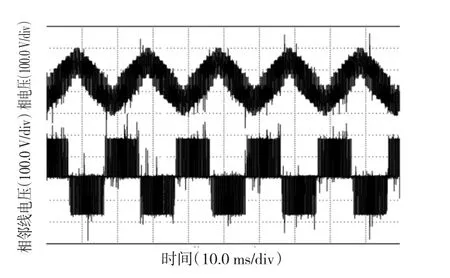

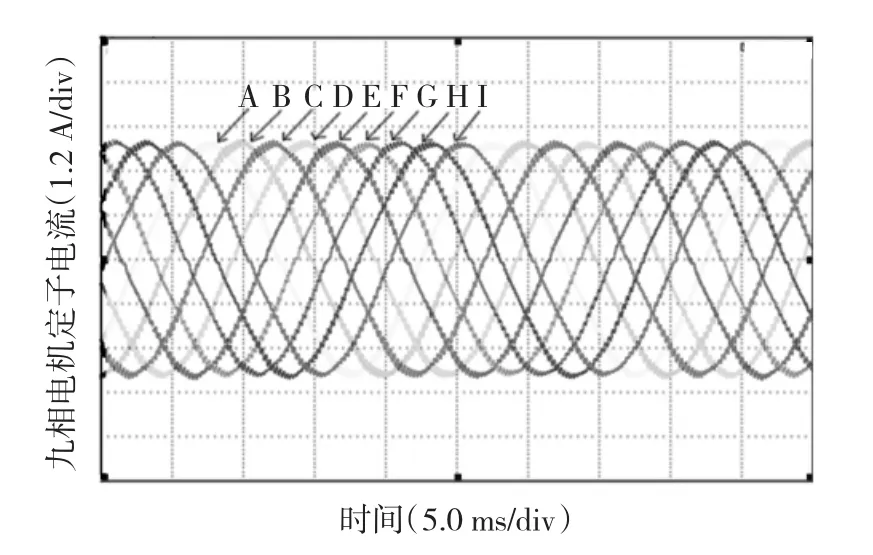

根据上文提到的系统结构和硬件控制平台,构建了一套多相变频调速系统,以一台九相感应电机为例,在该系统下实现了基于SPWM调制的变频变压控制。九相感应电机的额定参数为:额定功率PN=15 kW;额定转矩TN=150 N·m;额定相电压UN=230 V;额定电流IN=9 A;极对数np=3;额定调制波频率f=50 Hz。采用日本YOKOGAWA公司的波形记录分析仪(型号DL750)对逆变器输出的九路SPWM进行测量,测量结果如图9所示,九相感应电机的相电压、相邻线电压以及定子电流分别如图10、图11所示。可以看出,九路SPWM输出具有很好的同步性,无相位抖动,电机相电压和定子电流正弦,谐波少。

图9 九相电机SPWM输出Fig.9 SPWM outputs of the nine phase motor

图10 九相电机相电压和相邻线电压Fig.10 Phase voltage and adjacent line voltage of the nine phase motor

基于FPGA的高速性,FPGA可用作IGBT逆变模块的故障保护,IGBT驱动模块采用瑞士CONCEPT公司的 2SD315A。当 IGBT发生故障时,2SD315A会产生相应的故障信号,并将故障信号传输给 FPGA,FPGA接收到故障信号后立即封锁PWM输出。实验波形如图12所示,从局部放大图中可以看出,当IGBT故障信号由低变高时,下桥臂PWM输出在几个FPGA主频时钟周期内发生响应,PWM输出变为高阻状态(IGBT低有效),同一桥臂的两路PWM输出同时被封锁,可以有效保护IGBT模块,提高系统可靠性。

图11 九相电机定子电流Fig.11 Stator currents of the nine phase motor

图12 故障发生时FPGA封锁PWMFig.12 PWM block by FPGA when fault happens

4 结语

本文采用FPGA以PWM IP核的方式实现了多通道PWM发生器,利用FPGA的硬件并行性和可扩展性,对系统进行有效的故障保护和I/O口扩展,提高了系统的可靠性和集成度。基于FPGA和DSP构建多相变频调速系统,在此系统下可方便实现多相电机的各种控制策略。实验结果表明FPGA应用于多相大功率变频调速系统具有通用性、灵活性和高可靠性,为多相变频器的进一步推广应用提供了参考。

[1]赵品志,杨贵杰,刘春龙.五相电压源逆变器SVPWM优化算法[J].电机与控制学报,2009,13(4):516-522.ZHAO Pinzhi,YANG Guijie,LIU Chunlong.Optimal SVPWM algorithm for five-phase VSI[J].Electric Machines and Control,2009,13(4):516-522.

[2]KATS Y.Adjustable-speed drives with multiphase motors[C]//1997 IEEE International Electric Machines and Drives Conference,May 18 - 21,1997,Milwaukee,USA.1997:TC2/4.1 -TC2/4.3.

[3]张敬南,丛望,代科.多相Y绕组同步电动机数学模型研究[J].哈尔滨工程大学学报,2007,28(7):758-761.ZHANG Jingnan,CONG Wang,DAI Ke.Research on a mathematical model of a multi-phase Y-coil synchronous motor[J].Journal of Harbin Engineering University,2007,28(7):758-761.

[4]HOU Lijun,SU Yanmin,CHEN Lin.DSP-based indirect rotor field orient control for 15-phase induction machines[C]//2002 IEEE Region 10 Conference on Computers,Communications,Control and Power Engineering,October 28 - 31,2002,Beijing,China.2002,3:2057 -2060.

[5]颜景斌,刘嘉辉,谢金宝,等.矢量控制速度伺服系统的 FPGA实现[J].电机与控制学报,2007,11(1):17-20.YAN Jingbin,LIU Jiahui,XIE Jinbao,et al.FPGA implementation of the vector-controlled speed servo system [J].Electric Machines and Control,2007,11(1):17 -20.

[6]吴恒,王淦泉,陈桂林.CORDIC算法在基于FPGA的PMSM控制器中的应用[J].电机与控制学报,2009,13(z1):113-118.WU Heng, WANG Ganquan, CHEN Guilin. Application of CORDIC algorithm in FPGA based PMSM controller[J].Electric Machines and Control,2009,13(z1):113 -118.

[7]李建林,王立乔,李彩霞,等.基于现场可编程门阵列的多路PWM波形发生器[J].中国电机工程学报,2005,25(10):55-59.LI Jianlin,WANG Liqiao,LI Caixia,et al.Multi-PWM pulse generator based on FPGA [J].Proceedings of the CSEE,2005,25(10):55-59.

[8]胡海兵,姚文熙,江辉鸿,等.任意路通用PWM波形发生器的设计[J].电工技术学报,2008,23(12):115 -118.HU Haibing,YAO Wenxi,JIANG Huihong,et al.Design of a universal PWM generator with arbitrary number of PWM channels[J].Transactions of China Electrotechnical Society,2008,23(12):115-118.

[9]杨家强,黄进,康敏,等.多相感应电机的电子变极技术[J].电机与控制学报,2009,13(3):322 -326.YANG Jiaqiang,HUANG Jin,KANG Min,et al.Electronic pole changing technique of multi-phase induction motor[J].Electric Machines and Control,2009,13(3):322 -326.

[10]王叶辉,林贻侠,严伟.监视跟踪定时器电路的CPLD实现[J].测控技术与设备,2003,29(12):36-38.WANG Yehui,LIN Yixia,YAN Wei.Design of watch - dog timer circuit with CPLD [J].Electronic Engineer,2003,29(12):36-38.