基于CPLD的PWM发生器设计

2010-05-11耿伟松于海东

耿伟松,于海东

(扬州大学 能源与动力工程学院,扬州 225009)

基于CPLD的PWM发生器设计

耿伟松,于海东

(扬州大学 能源与动力工程学院,扬州 225009)

0 引 言

自从全控型电力电子器件问世以后,就出现了采用脉冲宽度调制的高频开关控制方式,形成了直流PWM调速系统[1]。脉宽调制变换器的作用是:用脉冲宽度调制的方法,把恒定的直流电源电压调制成频率一定、宽度可变的脉冲电压序列,从而改变平均输出电压的大小,以调节电机转速。

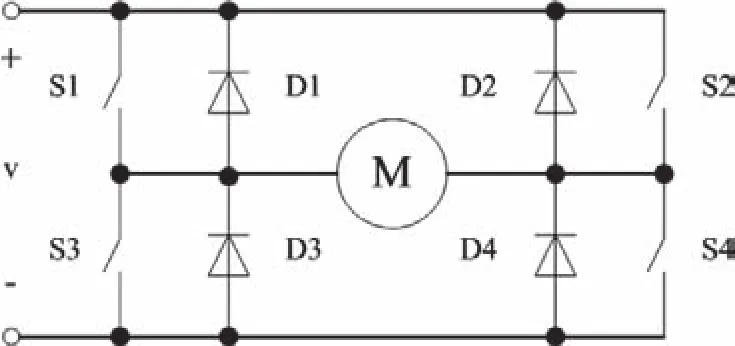

PWM变换器电路有多种形式,可分为可逆和不可逆两大类。其中可逆PWM变换器主电路有多种形式,最常用的是桥式(H形)电路。桥式变换器在许多动力系统中得到了广泛的应用(如直流驱动,直流-交流逆变器,开关电源等等)。

1 PWM发生器的设计

桥式变换器应用在直流电机调速系统中的主要电路结构如图1所示,开关控制基本上采用PWM技术。

图1 桥式变换器原理图

PWM信号发生器一般是通过模拟电路或者是基于微处理器的软件控制技术来实现,但随着高速开关器件的涌现,对于复杂的调制技术,即使采用最先进的DSP(数字信号处理器)也很难实现。

随着超大规模集成电路的集成度和工艺水平的不断提高,专用集成电路ASIC的设计成本在不断降低。CPLD/FPGA是实现ASIC的主流器件,它们具有极大的灵活性和通用性,工作速度快,开发效率高,成本低,可靠性好。近年来,CPLD在电机控制系统中的应用收到了系统设计人员越来越多的重视。用CPLD来设计PWM发生器将会简化控制系统的硬件和软件设计,获得更高的开关频率,减少微处理器的计算工作量。

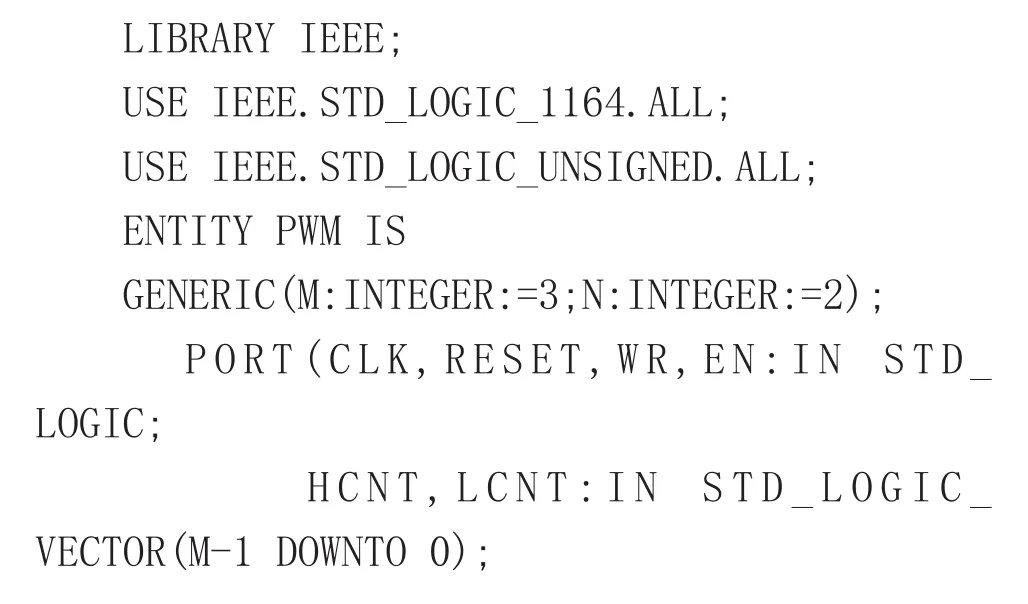

VHDL具有与具体硬件电路无关和与设计平台无关的特性,并且具有良好的电路行为描述和系统描述的能力,并在语言易读性和层次化、结构化设计方面表现了强大的生命力和应用潜力[2],因此本文选用VHDL语言进行编程,用一片CPLD设计了PWM发生器。

由于桥式PWM变换器的工作状态是确定的,所以采用状态机方式来编程[3]也是情有可原,虽然只有六个状态,但其程序实现起来是很复杂的。用数字比较器代替模拟比较器、用线性计数器代替锯齿波发生器来产生PWM信号[4,5]的设计方法也很繁琐。在分析了桥式PWM变换器工作原理的基础上,本文采用了一种巧妙的方法来设计,其原理简单,程序容易实现。

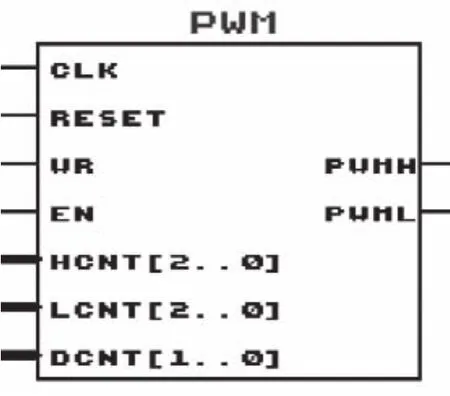

图2 PWM发生器端口图

图2为所设计的PWM发生器端口图,各引脚主要功能如下:

R E S E T:复位信号,输入,高电平有效,复位后发生器处于初始状态。

CLK:时钟信号,输入,用来接收外部时钟电路产生的信号。

WR:写信号,输入,低电平有效。若其有效,则装入计数器初值。

EN:使能信号,输入,高电平有效。若其有效,则计数器开始计数。

PWMH:输出信号,控制图1中的开关S1和S4。若PWMH=’1’,则开关闭合,否则断开。

PWML:输出信号,控制图1中的开关S2和S3。若PWML=’1’,则开关闭合,否则断开。

HCNT:HCNT计数器的数据输入端口,宽度3位。其初值的大小决定PWMH信号的作用时间。

LCNT:LCNT计数器的数据输入端口,宽度3位。其初值的大小决定PWML信号的作用时间。

DCNT:DCNT计数器的数据输入端口,宽度2位。其初值的大小决定死区的持续时间。为避免图1中处于同一个桥臂的两个开关S1、S3或者S2、S4的同时导通所引起的短路,特设置此间隔时间。

若该PWM信号发生器应用在基于微处理器的电机控制系统中,则HCNT、LCNT、DCNT等三个数据端口共8位与微处理器的数据总线连接。三个端口的宽度可根据实际应用灵活修改。三个计数器均为减法计数器。

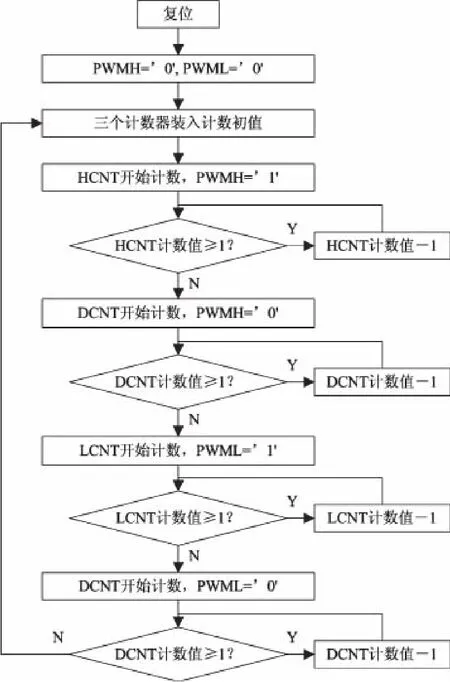

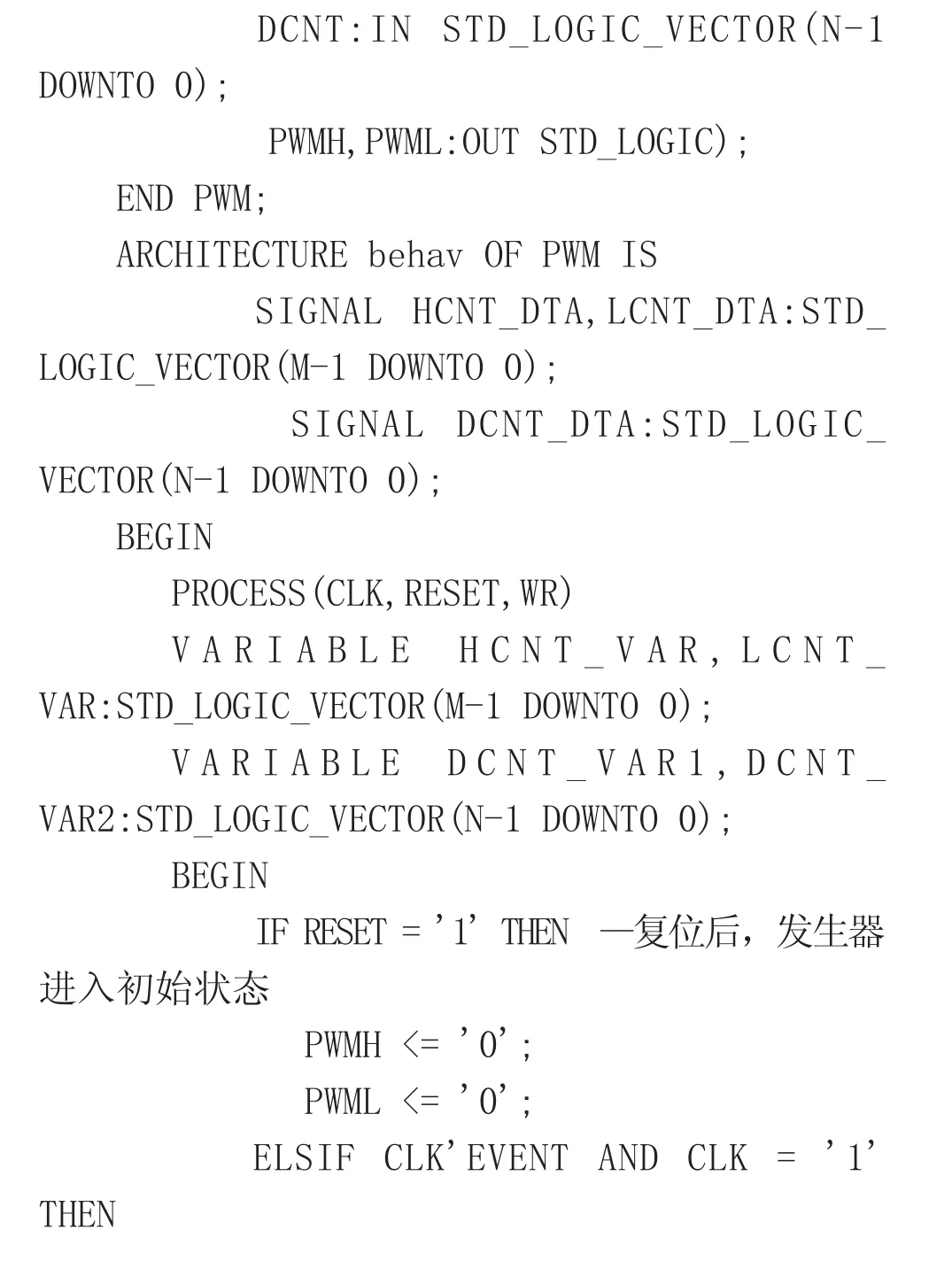

图3是PWM发生器的设计流程图,VHDL源程序清单如下:

图3 PWM发生器设计流程图

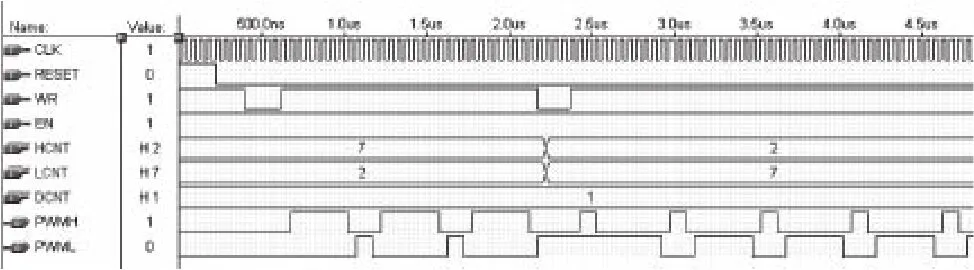

上述程序在ALTERA公司的MAX+plus II 10.2环境下编译通过,适配的CPLD器件为ALTERA公司的EPM7032LC44-6,仿真结果如图4所示。图4中对2组计数初值进行了仿真,第1组中HCNT、LCHT、DCHT的计数值分别为7、2、1,则PWMH、PWML的作用时间为7个和2个时钟周期,结合图1可知电机上获得的平均电压为正值,电机正转;第2组中HCNT、LCHT、DCHT的计数值分别为2、7、1,则PWMH、PWML的作用时间为2个和7个时钟周期,可知电机上获得的平均电压为负值,电机反转。一个PWM开关周期是7+2+1+1=11个时钟周期。改变HCNT和LCNT的计数初值,则可改变施加在电机上的平均电压及极性,从而实现电机的调速和可逆运转。由此可看出本文的设计是正确的。

图4 仿真波形图

2 结论

由于CPLD的I/O引脚多、规模大、支持重复擦写,因此只要在此基础上修改完善即可实现不同功能的PWM发生器,本文所采用的设计方法也适用于交流电机调速系统中SVPWM发生器的设计。本文所设计的PWM发生器很容易与微处理器连接,这种基于CPLD的设计方法,可使得电机控制系统的外围电路变得非常简洁,系统的可靠性和性能大大提高。

在近期内,微处理器与CPLD/FPGA 仍有很强的互补性[6],但从长远来看,在大部分的电子设计领域,微处理器、A/D、D/A 和RAM 等必将以各种软硬核的形式统一于CPLD/FPGA 中,片上系统SoC已成为电子设计的趋势。目前广泛应用的基于微处理器的电机控制系统今后可采用全硬件来实现,从而克服微处理器速度慢、复位慢,且不可靠,程序易“跑飞”等致命弱点。

[1]陈伯时.电力拖动自动控制系统-运动控制系统(第3版)[M].北京:机械工业出版社,2003.

[2]潘松,黄继业.EDA技术实用教程(第3版)[M].北京:科学出版社,2006.

[3]Alexander Arbit,Dan Pritzker,Alon Kuperman,and Raul Rabinnovici.A DSP-Controlled PWM Generator using Field Programmable Gate Array[C].Proc. IEEE Convention of Electrical and Electronics Engineers, 2004:325-328.

[4]冯小平,张林,赵焕军.一种基于CPLD实现的数字化PWM波形产生器[J]. 现代电子技术,2003(3):71-72.

[5]铁勇,郭改枝,李媛,等.基于CPLD控制的直流电机PWM控制器的设计[J].内蒙古大学学报(自然科学版),2006(6):667-671.

[6]陈祥涛,张前进.基于单片机与CPLD的步进电机PWM驱动技术[J].现代电子技术,2008,31(5):113-115.

A PWM generator designed with CPLD

GENG Wei-song, YU Hai-dong

H形桥式变换器在多种动力系统中有着广泛的应用。在电机控制中,H桥中开关的控制一般采用PWM控制技术。采用VHDL硬件描述语言设计了基于CPLD的PWM发生器,并使用Max+PlusⅡ进行仿真验证,仿真结果验证了设计的正确性。设计中采用了一种巧妙的方法来实现,其原理简单。基于CPLD的PWM发生器将会简化控制系统的硬件和软件设计,获得更高的开关频率,其应用这将大大简化直流电机控制系统的设计并且改善系统的控制性能。

H桥;PWM发生器;CPLD;VHDL;Max+ Plus Ⅱ

耿伟松(1990-),男,江苏连云港人,本科在读,研究方向为电气工程及自动化。

TM383.6

B

1009-0134(2010)06-0151-03

10.3969/j.issn.1009-0134.2010.06.50

2010-03-24