基于有限状态机的数字温度传感器控制系统设计*

2010-04-26王晓磊李宏生

王晓磊 李宏生

(东南大学微惯性仪表与先进导航技术教育部重点实验室 南京 210096)

1 引言

有限状态机(Finite State Machine,FSM)及其技术是实用数字系统设计中实现高效率高可靠逻辑控制的重要途径,是一种简单、结构清晰、设计灵活的方法,它易于建立、理解和维护,特别应用在具有大量状态转移和复杂时序控制的系统中,更显其优势。

有限状态机模型可以用下面包含5种元素的集合来表示{X,Y,S,f,g},假设S={S1,S2,…,Sk}是FSM中状态的集合;X={X1,X2,…,Xn}是FSM中输入的集合;Y={Y1,Y2,…,Ym}是FSM中输出的集合;f为状态转移函数,表示由输入信号变量X和当前状态X决定下一个状态,即:XY→S;g为输出函数,表示由输入信号变量X和状态S决定状态机的输出变量Y,即:XS→Y。从上面定义可以看出,有限状态机包含5类基本要素:即状态、输入、输出、转移函数及输出函数。它们分别用矢量函数表示如下[1]:

根据有限状态机是否使用输入信号,分为Moore型有限状态机和Mealy型有限状态机。Moore型状态机的输出只与当前的状态有关而与输入无关,而Mealy型状态机的输出不仅与当前状态有关,还与当前的输入有关,它们共同决定Mealy状态机的输出。本控制系统采用Moore型有限状态机实现数字温度传感器的控制。

2 DS18B20的读写方式[2]

DS18B20是单总线式数字温度传感器,支持“一线总线”接口,测量得到的数据为数字量,不需要经过模数转换。每一次命令和数据传输都是从主机启动写时序开始,如果要求从机回送数据,在写命令后,主机需启动读时序接收数据。

DS18B20有严格的信号时序,包括:

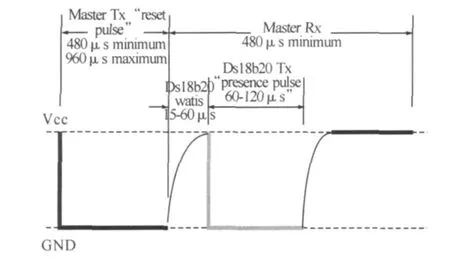

1)复位脉冲和应带脉冲

单总线上的所有通信都是以初始化序列开始。主机输出低电平,保持低电平时间至少480μ s,以产生复位脉冲。接着主机释放总线,4.7kΩ上拉电阻将单总线拉高,延时 15~60μ s,并进入接收模式。接着DS18B20拉低总线60~240μ s,以产生低电平应答脉冲,若为低电平,再延时480μ s。如图1所示。

图1 复位与应答脉冲

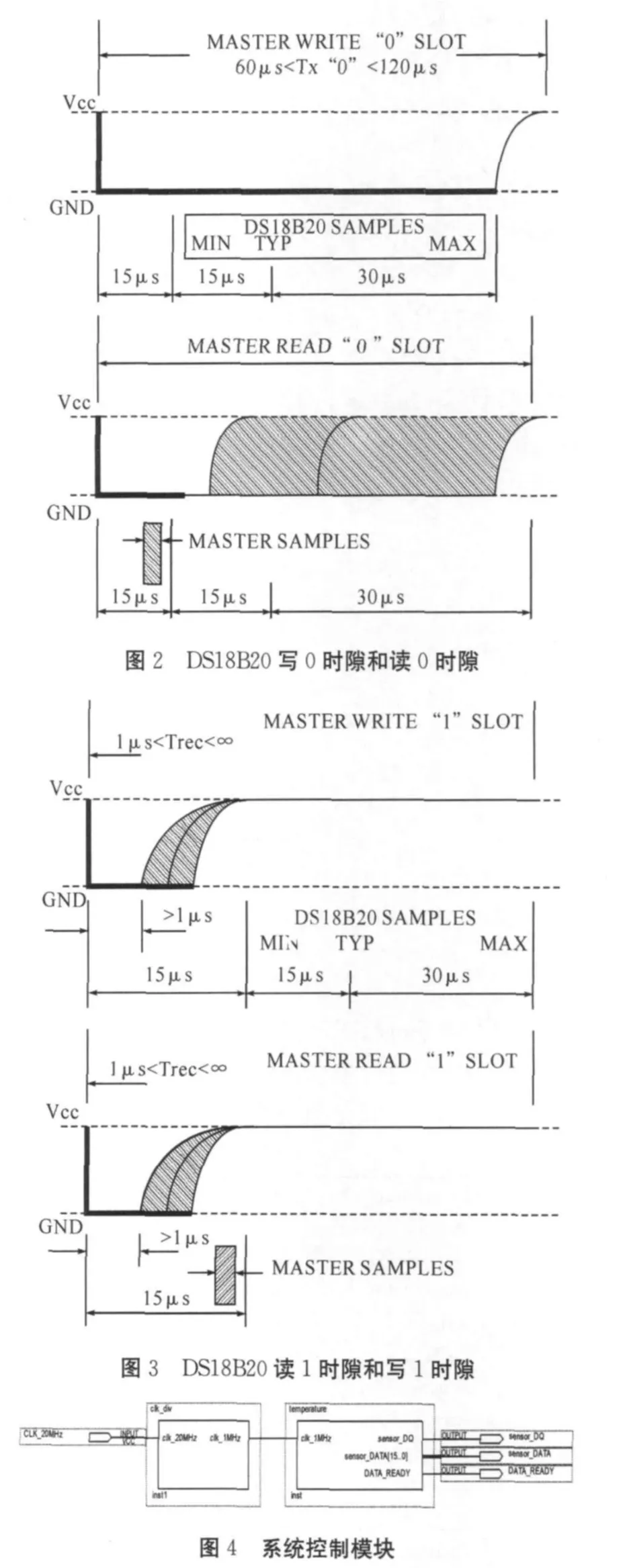

2)写时隙

写时隙包括写0时隙和写1时隙。所有写时隙至少需要60μ s,且在2次独立的写时隙之间至少需要1μ s的恢复时间,两种写时隙均起始于主机拉低总线。

3)读时隙

DS18B20仅在主机发出读时隙时,才向主机传输数据,所以,在主机发出读数据命令后,必须马上产生读时隙,以便从机能够传输数据。所有读时隙至少需要60μ s,且在2次独立的读时隙之间至少需要1μ s的恢复时间。每个读时隙都由主机发起,至少在时隙起始后的15μ s之内采样总线状态。

3 温度控制模块

本设计采用Altera公司的 EP2C8T144I8N CYCLONEⅡ芯片作为系统控制器[3]。

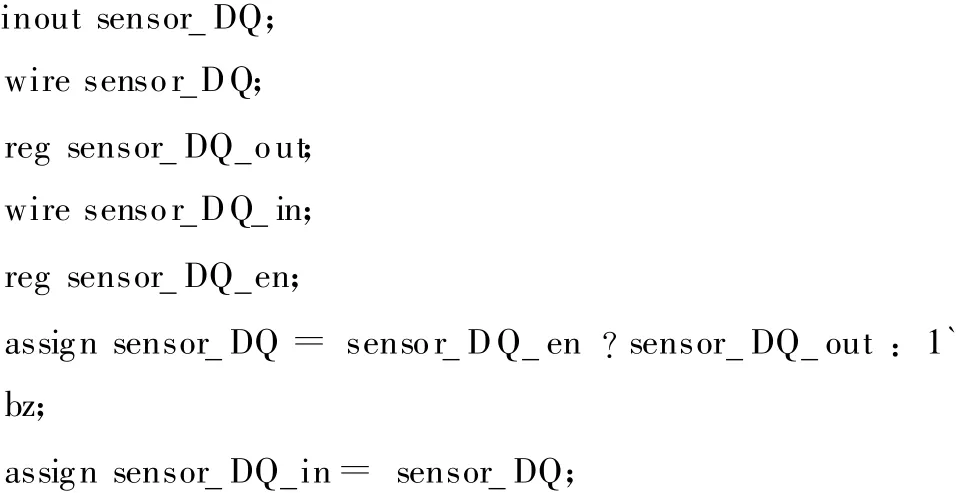

控制模块包括clk_div分频模块和Temperature状态机控制模块。clk_div模块功能是将系统时钟20MHz分频为1MHz;temperature模块功能是向DS18B20输出控制命令,并将DS18B20并将测量得到的数字温度值输出。

在FPGA芯片中,一般信号线用做总线等双向数据传输的时候就要用到INOUT类型了。inout在具体实现上一般用三态门来实现。三态门的第三个状态就是高阻‘Z'。当inout端口不输出时,将三态门置高阻。在 Temperature控制模块中,sensor_DQ引脚在VerilogHDL语法中定义为inout类型,此引脚连接DS18B20的DQ引脚[4]。

本系统设计中,定义了:

对于sensor_DQ_out,可以通过组合逻辑或者时序逻辑根据sensor_DQ_in对其赋值。通过控制sensor_DQ_en的高低电平,从而设置sensor_DQ是输出数据还是处于高阻态,如果处于高阻态,则此时当做输入端口使用,sensor_DQ_en可以通过相关电路来控制。

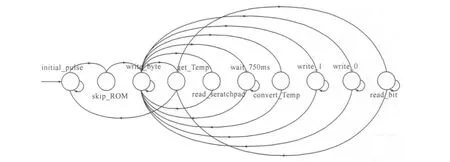

4 有限状态机实现时序控制

为了保证测量数据的可靠传输,任一时刻单总线上只能有一个控制或数据信号。访问DS18B20的操作顺序遵循以下三步:

第一步:初始化;

第二步:ROM命令;

第三步:DS18B20功能命令;

单总线数字温度传感器DS18B20时序控制流程图如图5所示。

图5 状态机时序控制流程图

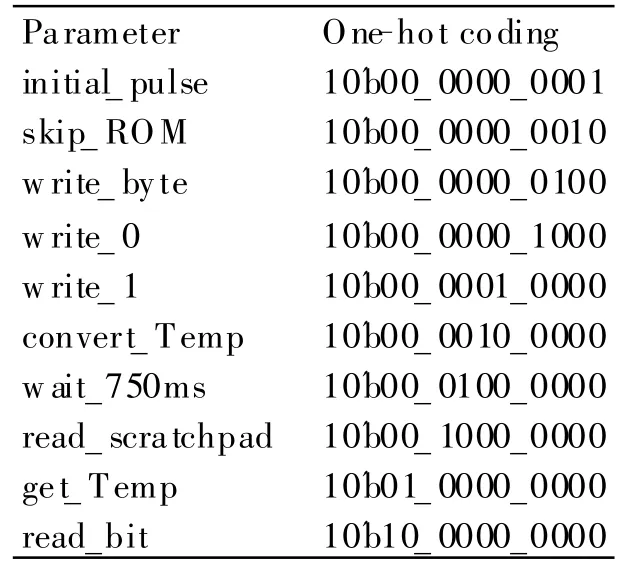

采用VerilogHDL语言描述此Moore型有限状态机,FPGA通过单总线对DS18B20进行操作,其one-hot编码定义的状态变量如表1所示[5]。

表1 one-hot编码定义

其中,initial_pulse:复位和应答脉冲状态,用于DS18B20的初始化,以及主从器件通信的开始;程序中首先发送480μ s的低电平,而后释放总线90μ s,然后再释放总线400μ s,检测器件的应答脉冲。

skip_ROM:跳过ROM状态。当主机检测到应答脉冲后,发出ROM命令,本系统只连接单个DS18B20,故发出跳过 ROM(skip ROM)命令CCh。

write_byte:写字节状态。由于DS18B20功能命令均为一个字节长度,故用于其他写指令状态的调用。

write_0:写 0时隙状态,用于主机向DS18B20写低电平;程序中写时隙15μ s,拉低总线;而后FPGA 发送60μ s的低电平;再经过10μ s的恢复时间,这就完成了写数据0。

write_1:写 1时隙状态,用于主机向DS18B20写高电平;程序中写时隙15μ s,拉低总线;而后FPGA 发送60μ s的高电平;再经过10μ s的恢复时间,这就完成了写数据1。

convert_Temp:温度转换状态;FPGA发送命令数据44h,用于主机启动温度转换。

wait_750ms:等待器件温度转换状态;主机发出温度转换命令后,进入wait_750ms状态,等待传感器温度转换,以及数据存储。

read_scratchpad:读暂存器(scratchpad)状态;FPGA发送命令数据BEh。

get_Temp:读取温度转换数据状态,主机命令DS18B20读取温度值。

read_bit:位读取状态;传感器转换后的数据存于暂存器,主机通过单总线一位一位的读出,存于寄存器中;程序中先2μ s读时隙,而后延时10μ s;再经过3μ s的读数据时间,而后延时 55μ s,这样就完成了一位数据的读出[6]。

5 Signal TapⅡ硬件调试[7]

嵌入式逻辑分析仪Signal TapⅡ主要用于分析数字系统的检测和故障诊断问题,是数据域测试中一种非常有效的测试方式。它在对系统硬件模块进行监测时,是将测得的样本数据暂存于目标器件的RAM中,然后通过器件的JTAG端口和USB BlasterⅡ下载线一起将样本数据信息传出并送入计算机进行数据分析。通过实践证明,在 FPGA上用这种方法抓取数字信号更便捷,更准确,易实现更高的精度。

其调试的基本步骤如下[8]:

1)打开Signal TapⅡ编辑窗;

2)调入待测信号;

3)相关参数设置。首先设置采样时钟;其次设置采样深度;最后设置触发条件;

4)下载、启动并查看数据。

当测试程序下载到FPGA并运行后,用Signal TapⅡ抓取DS18B20的输入输出端口以及读取温度数据信号如图6所示。

图6 Signal TapⅡ调试图

6 结语

文中分析了DS18B20的工作原理,并采用有限状态机设计其控制逻辑,相比单片机控制,更具有实时性,实现了温度采集接口,该接口可以作为一个独立模块嵌入到其他电路组成的应用系统中。

有限状态机作为数字逻辑理论的一个重要组成部分,不仅是重要的软件基础理论,而且在硬件设计中也发挥着重要的作用,特别是在利用EDA技术进行可编程ASIC设计时。

[1]Zhang Peiren,Zhou Yanping.A Large-Scale Temperature Alarm System Based on 1-Wire Bus and CAN bus[J].Control&Automation,2003(2):25~26

[2]李钢,赵彦峰.1-Wire总线数字温度传感器DS18B20原理及应用[J].现代电子技术,2005,28(21):77~79

[3]周岳斌.基于FPGA的数字温度传感器接口设计[J].现代电子技术,2007,12:51~52

[4]何文龙,房建东.基于FPGA的数字温度传感器控制方法[J].电子测量技术,2008,11:178~181

[5]刘小平,何云斌,董怀国.基于VerilogHDL的有限状态机设计与描述[J].计算机工程与设计,2008,29(4):958~960

[6]王凌,宋扬等.基于有限状态机的飞行器自毁系统时序控制设计[J].现代电子技术,2009,8

[7]胡文军,李英辉.嵌入式逻辑分析仪在FPGA设计中的应用[J].微计算机信息,2007,23:211~212,203

[8]袁火平,卢艳娥,等.基于SignaltapⅡ的高速数据采集系统[J].微计算机信息,2008,24:9