基于Verilog HDL的新型DDS的结构设计

2010-03-27苑文举陈晓霞

苑文举, 陈晓霞, 蔡 翔

(长春工业大学计算机科学与工程学院,吉林长春 130012)

0 引 言

直接数字频率合成(Direct Digital Synthesizer,DDS)技术是一种新的全数字的频率合成原理,它从相位的角度出发直接合成所需波形。这种技术由美国学者J.Tiercy,M.Rader和B.Gold于1971年首次提出。随着现场可编程门阵列(Field Programmable Gate Array,FPGA)、复杂可编程器件(Complex Programmable Logic Device,CPLD)等技术的出现以及对DDS理论上的进一步探讨,使得DDS技术得到了飞速的发展。DDS技术是第三代频率合成技术,与传统的频率合成技术相比,具有分辨率高、变频速度快、相位变化连续等特点,易于扩展和数字化集成,容易实现对输出信号的多种调制,广泛应用于通讯、雷达、遥控测试、电子对抗以及现代化的仪器仪表等许多领域。

文中讨论了用FPGA(EP3C25Q240C8)实现DDS,结合硬件描述语言Verilog HDL在Modelsim 6.2b中来完成,用ARM(S3C2440)来实现数字移相的波形发生器的设计方法。

1 DDS的结构设计[1-3]

1.1 典型DDS的信号源结构及工作原理

该移相信号发生器是基于DDS技术而实现的,其原理框图如图1所示。

图1 典型DDS的结构框图

该方案的设计主要是将数据地址的偏移量映射为信号间的相位值[4]。它是由ARM系统、锁相环、相位累加器、波形存储器、数模转换器以及低通滤波器组成。其工作原理是:由键盘输入频率和相位控制字,在时钟脉冲的作用下,累加器将频率控制字与累加相位数据相加,累加的结果存入相位寄存器中。相位寄存器一方面将加法器在上一次累加产生的结果反馈到累加器的输入端与频率控制字继续累加,另一方面其输出的地址分成两路:一路直接从波形存储器中取出波形幅度的数据,经D/A转换器和低通滤波器将波形数据转换成参考信号,另一路则通过相位加法器与相位控制字相加,形成移相信号的地址码,从波形存储器中取出波形幅度数据,经过D/A转换和低通滤波器将波形数据转换成所需要的移相信号。当相位累加器累积满量程时就会产生一次溢出,这样就完成了一个周期性的动作。

1.2 新型DDS的结构设计及工作原理

为了实现提高整个系统的工作频率[5],就需要提高数字电路的工作频率。而对于大多数利用FPGA来实现数字电路的DDS系统来说,FPGA的工作频率最多也只能达到几百兆赫兹,这样就远远低于DAC的工作频率,不能满足要求。

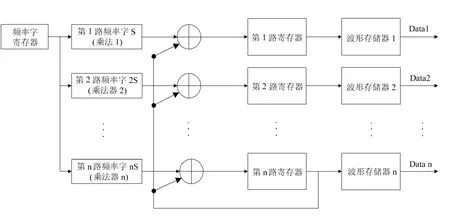

并行数据相位生成电路及相应的波形存储器结构如图2所示。

图2 并行数据相位生成电路及相应的波形存储器结构示意图

这里的新型DDS的结构主要是并行相位生成电路,它可以在一个时钟周期内同时生成多个数据的相位,然后进行多个波形存储器同时查表来获得多个数据。

在用FPGA设计DDS电路时,累加器是决定DDS性能的一个关键部分。这里采用并行的数据相位生成电路:它包含有多路的相位生成电路,每路的相位生成电路包括一个加法器和一个频率字寄存器。第1路的频率字设为S,第2路频率字寄存器的值就为2S,第3路频率字寄存器的值为3S,依次类推,第n路频率字寄存器的值即为nS。且第1路相位生成电路的输出为最后1路的相位和第1路频率字寄存器S的相加值,第2路的输出为最后1路相位和第2路频率字寄存器2S的相加值,依此类推,最后1路的输出即为本路频率字寄存器的累加值。且每一路的相位生成电路的输出都各自经过一个波形数据存储器作为查找表,然后通过查表将数据读出。查表后读出的数据再经过一个并串转换器将n路并行数据转换成一通道的数据输出,最后经过D/A转换器转换成模拟量,把存入的波形重新合成出来。

并行相位生成电路产生的数据相位个数M与FPGA的工作频率、DAC的工作频率有关:

由于本设计中采用AD9779A,FPGA为EP3C25Q240C8,所以,这里的数据相位个数M为5,相位累加器的位数为48位,波形存储器的寻址地址为12位。

1.3 并-串转换模块[6-7]

16通道的5位并行数据转换成1位的串行数据,关键在于多通道信号的同步控制,并行数据送出时钟和并串转换时钟是5分频的关系。即并串转换模块的输入时钟是系统时钟的5倍。并串转换模块的原理如图3所示。

图3 并串转换模块的原理图

2 系统的调试与输出

所设计的新型DDS结构在Modelsim6.2b中输出正弦波的功能仿真如图4所示。

图4 新型DDS输出正弦波数字仿真图

由图中可以看出,当系统时钟输入为100 MHz时,频率控制字为0x4FF0000000,正弦波输出频率为122.5 kHz,且改变频率控制字就可以改变波形的输出频率[8]。在仿真正确后,将工程编译生成的.sof文件下载到Altera公司的EP3C25Q240C8中做验证。经过测试表明,电路的实际结果与仿真结果完全一致,符合设计的要求。

3 结 语

系统采用一种并行的数据相位生成电路的方法来设计一种新型的DDS结构,在一个时钟内能同时生成多个数据,从而突破了FPGA工作频率的限制,可以向D/A提供超过1 GHz以上的数据采样率。系统操作方便且运行稳定。

[1] 白居宪.直接数字频率合成[M].西安:西安交通大学出版社,2007.

[2] National Instruments Corporation.Understanding direct digitub synthesis[Z].2006.

[3] Analog Devices Inc.A technical tutorial on dignal synthesis[Z].1995.

[4] 付莉,潘明.基于FPGA数字移相信号发生器设计[J].桂林电子科技大学学报,2009,25(5/2):175-176,107.

[5] 周俊峰,陈涛.基于FPGA的直接数字频率合成器的设计与实现[J].国外电子元器件,2003,1(1):4-6.

[6] 何柯.800兆高速任意波形产生硬件平台研究与实现[D]:[硕士学位论文].成都:电子科技大学,2007.

[7] 蒋迺倜,江涛,陈建军.并串转换法合成多通道宽带DDS信号[J].雷达与对抗,2009(4):31-34.

[8] 胡力坚.基于DDS的任意波形发生器设计与实现[D]:[硕士学位论文].西安:西安电子科技大学,2009.