EEPROM单元抗辐射版图设计技术

2010-02-26田海燕周昕杰

赵 力,田海燕,周昕杰

(中国电子科技集团公司第五十八研究所,江苏 无锡 214035)

1 引言

EEPROM作为非挥发的存储设备,大量用于航空航天及军事领域。但由于太空及军事应用环境的复杂性,存储单元常常会受到辐射的影响而使关键数据丢失或器件失效。如何满足太空及军事领域的需要,提高EEPROM的抗辐射性能,是多年来研究热点之一[1~2]。文章在现有的工艺基础之上,研究了如何通过版图解决EEPROM存储单元受辐射的影响,改进了原有单元的版图,增强了单元抗辐射的性能,并将其成果应用到实际工作中。

2 辐射效应分析

经国内外研究,EEPROM器件的14MeV中子和31.9MeV质子的辐射效应不是单粒子效应,而是一种总剂量效应[3]。所以对于EEPROM单元受辐射影响,主要考虑总剂量效应。总剂量效应对EEPROM单元的影响主要表现为:

(1)对浮栅或ONO存储介质层的影响,造成存储电荷的浮栅或ONO介质层漏电,使得所存的数据丢失;

(2)在场氧化层侧壁形成正电荷堆积,使一个单元内的源/漏端之间漏电,使器件失效;

(3)在场氧化层下形成正电荷堆积,使相邻单元管之间的隔离失效,形成静态漏电流通道,使器件失效。

由于EEPROM工艺的限制,影响(1)只能通过改变器件结构和存储机制来克服[4]。而影响(2)和(3),可通过改进版图的方式来修改。

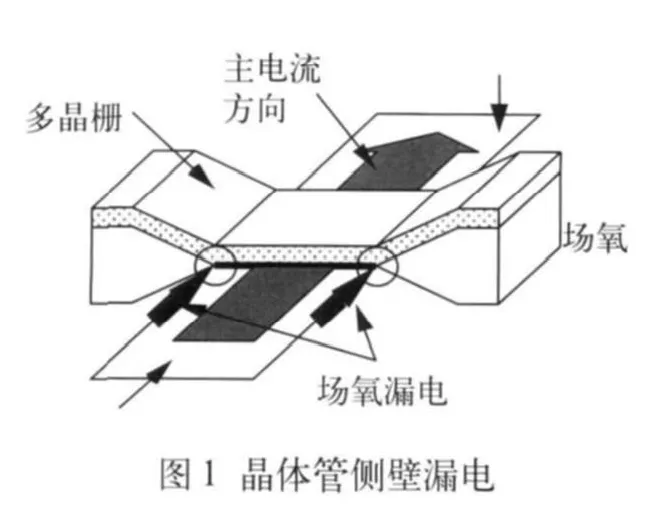

首先分析影响(2)的漏电机制。采用自对准工艺制作的晶体管,多晶硅栅淀积在薄氧化层上,源/漏由没有被多晶硅覆盖的有源区注入形成,这种工艺制造出的电路密集度高,但使多晶硅栅在场氧和栅氧过渡区产生了一个寄生晶体管,这个寄生晶体管对总剂量效应十分敏感。因为场氧和栅氧化层在辐射条件下,会电离电子-空穴对;由于陷阱的俘获作用,在Si/SiO2系统的SiO2一侧堆积正电荷,形成界面态,严重影响到晶体管的I-V特性,随着辐射剂量的增加,边缘寄生晶体管漏电流也迅速上升,当漏电流增加到接近本征晶体管的开态电流时,晶体管会永久开启,导致器件失效。图1为该机制漏电示意图。

接下来分析影响(3)的漏电机制。场氧化层本来是为相邻晶体管绝缘隔离的,但由于总剂量效应,在场氧中会电离电子-空穴对;由于陷阱的俘获作用,在Si/SiO2系统的SiO2一侧堆积正电荷,形成界面态,有可能形成场氧下反型的漏电结构,如图2所示。场氧漏电沟道能延伸到邻近晶体管的源/漏区,这将增大VDD到VSS的静态漏电流。

图2 场氧下漏电

3 EEPROM抗辐射版图设计

EEPROM单元制成工艺包括了FLOTOX和SONOS两种。

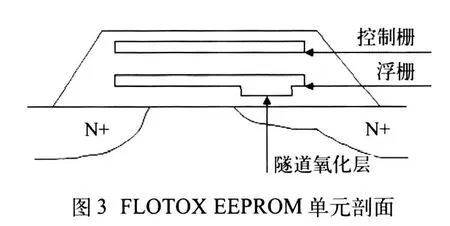

FLOTOX是利用两层多晶,其中一层多晶作为浮栅,存储电荷。栅和漏之间有一层隧道氧化层(Tunnel Oxide),浮栅上的电荷通过隧道氧化层实现“写入(Write)”和“擦除(Erase)”的功能。

控制栅接高压、漏极接地时,电场方向由浮栅指向N+埋层,电子由N+埋层通过隧道氧化层到浮栅;漏端接高压,而栅接地时,电场漏极指向浮栅,浮栅上的电子通过隧道氧化层到达漏区。浮栅在充电和放电两种状态时,EEPROM存储管的阈值电压是不同的,因此可以代表存入两种不同的状态,浮栅由于带上不同的电荷状态,可以用来表示逻辑“1”和“0”。FLOTOX EEPROM单元剖面图如图3所示。

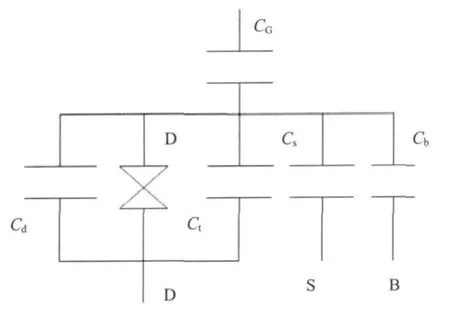

在设计FLOTOX EEPROM单元版图时,采取管内隔离和管间隔离的方法,解决存储管漏电问题。但其版图设计难度在于,在兼顾抗辐射性能的同时,还要考虑到单元内电压耦合比问题。电压耦合比直接决定其性能和可靠性。存储管等效电路如图4所示,图中Cpp为两层多晶之间的电容,是两个栅平板电容与侧壁电容的总和,Cd为浮栅和漏区之间的电容,D为隧道效应二极管,Ct为隧穿栅氧化层电容,Cs为浮栅和源区间的电容,Cb为浮栅和衬底的电容。

当擦除时,控制栅加高压VCG,漏区、源区、衬底都接地。有如下关系[5]:

Vtue为隧道氧化层中的电压。

其中令Ke为擦耦合系数:

当写入时,控制栅接地,漏接VD,而源端悬浮。有如下关系:

其中令Kw为写耦合系数:

图4 FLOTOX存储管等效结构

综上所述,在设计FLOTOX 版图时,在满足抗辐射要求的同时,应注意选取器件浮栅和控制栅的面积,满足器件电压耦合比的要求,使器件性能得到优化。

SONOS结构的EEPROM如图5所示。利用F-N 隧穿效应或者热电子发射机制,将电荷存在绝缘的ONO介质层。通过存储和抽取电子,改变器件的阈值电压[6]。在设计时,由于只使用到单层的多晶,不需要考虑电压耦合比,只需要考虑器件抗辐射性能即可。

图5 SONOS单元剖面图

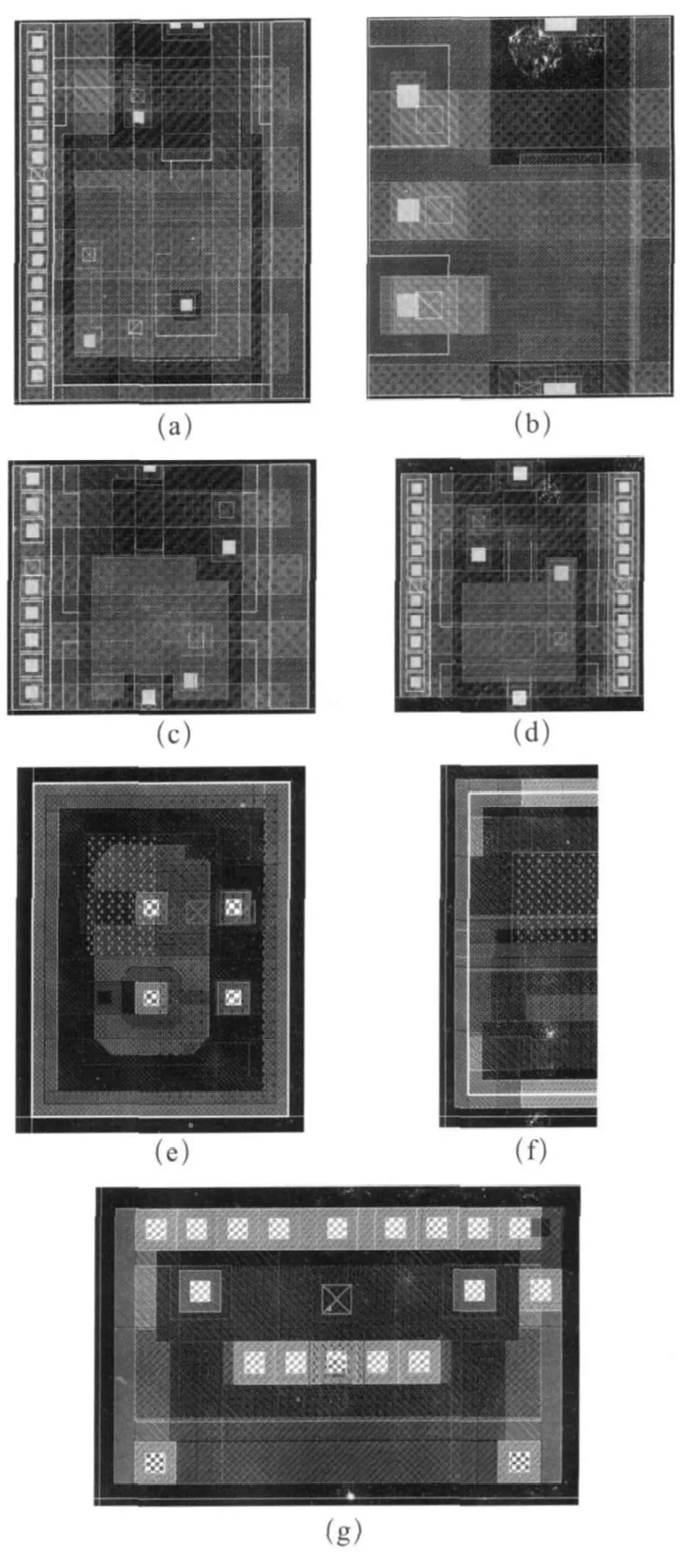

图6为几种EEPROM抗辐射版图。采用了管内隔离和管间隔离的方法,使得管内源/漏端和相邻两管源/漏端之间没有场氧介入,或是将场氧隔开,不让场区下形成漏电通道。表1给出了单元版图的相关参数。

图6 EEPROM抗辐射版图

表1 抗辐射单元版图参数

4 小结

通过对EEPROM存储单元漏电机理的分析,基于FLOTOX和SONOS工艺,在版图中通过管内加固和相邻管之间隔离加固的方法,设计了多种抗辐射版图。同时也指出了在设计FLOTOX EEPROM单元版图的同时,必须兼顾到器件操作电压耦合比。为目前芯片的设计提供了有力的技术支持,同时也为以后抗辐射版图设计提供了有用的参考。

[1]E.S. Snyder, P.J. McWhorter, et al. Radiation Response of Floating Gate EEPROM Memory Cell [J]. Nuclear Science,1989,36(6):2 131-2 139.

[2]D.Willams, D. Adams, et al. Radiation Hardened 64k/256k EEPROM Technology [A]. Int’l Nonvolatile Memory Technology Conference.

[3]贺朝会,耿斌,等.浮栅ROM与SRAM的辐射效应比较分析[J].电子学报,2003,31(8):1 260-1 263.

[4]M .H. White, D. Adams, et al. Characterization of Scaled SONOS EEPROM Memory Device for Space and Military System [A]. In: 5th Annual Non-Volatile Memory Technology Symposium[C]. IEEE Electr Devices Soc, 2004: 51-59.

[5]于宗光,许居衍,魏同立.双层多晶硅Flotox EEPROM单元的优化设计[J].应用科学学报,1997,15(1): 82-88.

[6]Wang Y, M.H. White. An Analytical Retention Model for SONOS Nonvolatile Memory Devices in the Excess Electron State [J]. Solid State Electr, 2005, 49:97-107.