基于Avalon-ST接口帧读取IP核的设计和应用*

2010-01-27邓超,付扬

邓 超,付 扬

(北京工商大学 计算机与信息工程学院,北京 100048)

基于Avalon-ST接口帧读取IP核的设计和应用*

邓 超,付 扬

(北京工商大学 计算机与信息工程学院,北京 100048)

研究基于Avalon-ST接口帧读取的IP核设计应用,通过Avalon-ST接口将外部存储中不同格式的帧数据转化为视频流输出。根据Avalon总线协议及Avalon-ST视频协议研究设计方案,使用Verilog HDL语言对模块进行硬件设计,并将实现的模块进行测试。结果表明,该IP核与Altera公司提供的Frame Reader模块相比,突破了现有的Frame Reader只支持紧缩格式的局限,使其功能更加完善,并且该IP核占用的资源少,工作频率更高,性能得到了优化,实用性更强。

Avalon-ST;帧读取;IP核;SoPC

可编程片上系统 SoPC将软核处理器 Nios II、存储器、I/O等IP核集成到单片FPGA上,它同时具有软件和硬件所固有的特点。利用SoPC Builder将自定义的IP核加入到Nios II系统中,充分发挥IP核的可移植性、复用性,提高产品设计效率[1]。IP核通过 Avalon总线与Nios II进行数据交互,Avalon片内总线成为 CPU与 IP核交流的桥梁,直接影响系统的整体效率。Avalon总线是 Altera公司专门为 SoPC而推出的一套片内总线系统,与Nios系列的处理器软核一起,二者构成了Altera公司SoPC方案中的核心部分。Avalon总线标准规定了Avalon-MM(Memory Mapped)和 Avalon-ST(Strming)两种接口[2]。使用SoPC技术进行视频数据处理时,两种接口的不同使用可以提高系统的运行速度。Avalon-ST接口是一种单向点对点的高速接口,主要针对的是高速数据流的传输,减少数据流处理中的瓶颈,特别适合处理图像和视频数据,利用 Avalon-ST接口进行视频处理,可极大地提高系统的处理速度[3]。

本设计研究了如何将从外部存储器中读取的视频数据转换为满足Avalon-ST视频处理协议的视频流,针对 Altera公司提供的视频及图像处理套件中 Frame Reader IP核只支持紧缩格式的使用局限,设计并实现了紧缩和平面两种帧格式的帧读取IP核。

1 Avalon-ST视频处理协议

带有 Avalon-ST接口的 IP核可以用来处理要求高带宽、低延迟、单向性的数据。典型应用包括多路复用数据流、数据包及DSP数据处理等。Avalon-ST接口信号既可以用来描述传统的没有确认信号的简单数据流,也可以描述复杂的带有传输协议或多通道交叉存取的数据包传输。行标志位(Interlacing)4位。宽为一帧图像每行所包含的像素数,高为一帧或一场中包含的行数。隔行标志位Interlacing的前两位指明了下一个视频数据包是否为隔行扫描方式,00表示逐行扫描方式,10表示偶数场,11为奇数场。当前两位为10或11时,标志位中的后两位用于隔行数据的同步。

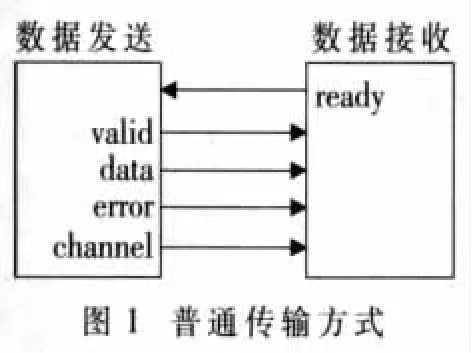

Avalon-ST接口包含两种传输方式:普通传输方式和包传输方式[4]。普通传输方式如图1所示。

图中写明了用到的接口信号,带箭头的横线表示端口的作用方向,省略了端口接收端的信号名称。当 ready信号有效时,发送端通过data端口发送数据,valid信号指明了发送的数据是否有效。channel为通道号,error信号为错误标识号,零值代表传输无误。

包传输方式是在普通传输方式的基础上增加了startofpacket、endofpacket、empty三个信号,实现了对封包型数据传输的支持。Startofpacket信号用来标识包的开始,endofpacket表示包的结尾,empty代表了包结尾的补零个数。

Altera公司提供的视频及图像处理套件可以方便、灵活地对视频和图像进行处理。它提供通用的 Avalon-ST接口及Avalon-ST视频处理协议,使用Avalon Memory-Mapped(Avalon-MM)接口连接外部存储器模块并进行实时控制,可以很方便地通过MegaWizard面板进行参数设置及硬件生成。视频及图像处理套件中的IP核使用 Avalon-ST视频处理协议,该协议以封包的方式通过Avalon-ST接口传输控制数据和视频数据。在很大程度上减小了视频处理系统对外部控制逻辑的需求。

Avalon-ST视频处理协议将包分成若干个记号,每个记号代表一段单独数据。传输前需要确定一个周期中并行传输的记号个数及记号位宽,每个记号最小为4位。传输的视频数据包只能是未压缩的视频数据,控制数据包用来对输入的视频数据进行配置。每个包并行传输的第一组记号中,最低4位为包类型标识符。0代表视频数据包,1~8为用户自定义包类型,9~14保留将来使用,15表示控制数据包。

一个视频数据包包含完整的逐行扫描帧或隔行扫描场的像素值,按图像平面中从左上到右下的顺序扫描发送,发送前需要确定颜色模式 Color Pattern和每个像素占用的比特数。每个像素对应传输中的一个记号,其位宽也决定了记号的位宽。颜色模式是对颜色平面采样的组织形式,每种颜色模式都可按并行方式传输或串行方式传输。一般常用的颜色模式有RGB、YCbCr、YCbCr(4:2:2)和YCbCr(4:2:0)。

完整的 RGB和YCbCr型视频数据包结构如图 2所示。

控制数据包用来传输控制信号,除了4位的包类型标识符15外,还包含宽(Width)16位、高(Height)16位、隔

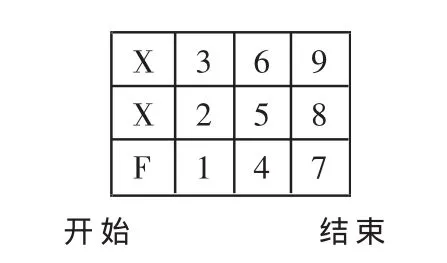

图3 并行传输的控制数据包

每次发送视频数据包之前必须先发送控制数据包,每个控制数据包一般由10个有效记号组成,每个记号只使用最低4位,其余位不使用。第一个有效记号为包类型标识符,剩下的9个有效记号为宽、高和隔行标志位。图3为并行传输3个记号的控制数据包。

图中第一列记号是包类型标识符,F为十六进制数,等于十进制数中的15。记号1~4的低4位共同组成16位的帧宽,记号5~8的低4位组成16的帧高,记号9的低4位为隔行标志位(Interlacing 4位)。

2 帧读取IP核的硬件设计

2.1 总体设计方案

利用SoPC技术进行视频数据处理时,待处理的原始视频数据可以是由外部设备输出的视频信号,也可以是存放在外部存储器中的视频数据。当视频数据存放在存储器中时,SoPC系统需要使用 Avalon-MM接口从外部存储器中读取视频数据,然后通过Avalon-ST接口将原来的视频数据转为满足 Avalon-ST视频处理协议的视频流,以方便之后使用Altera视频及图像处理套件对视频进行处理。因此系统中需要一个帧读取IP核来完成这种转换。

一帧完整的图像其像素数据在存储器中有多种组织形式,按颜色空间可以分为 RGB型和YUV(YCbCr)型。如果是YUV模型,又可以按组织方式分为平面型和紧缩型,按采样比可分为4:4:4、4:2:2和4:2:0等。一般RGB模型均为紧缩型,按像素值的位数不同可分为RGB24、RGB32等。总的说来,常用的数据格式有RGB24、 RGB32、YV12、I420等几种。

现有的 Altera公司提供的视频及图像处理套件中Frame Reader模块可以将存储器中视频数据转为满足Avalon-ST视频处理协议的视频流,但该 IP核只支持紧缩格式,原始数据在存储器中必须按像素扫描顺序连续存放。而实际中有多种帧格式,例如 I420是平面格式,这种情况就无法使用Frame Reader了。

在实际应用中,由于 Altera的 Frame Reader使用限制,作者自行研发了帧读取 IP核(Frame Reader),除了实现紧缩格式的视频数据转为满足 Avalon-ST视频处理协议的视频流,还能实现I420到 RGB24的平面格式的转换。

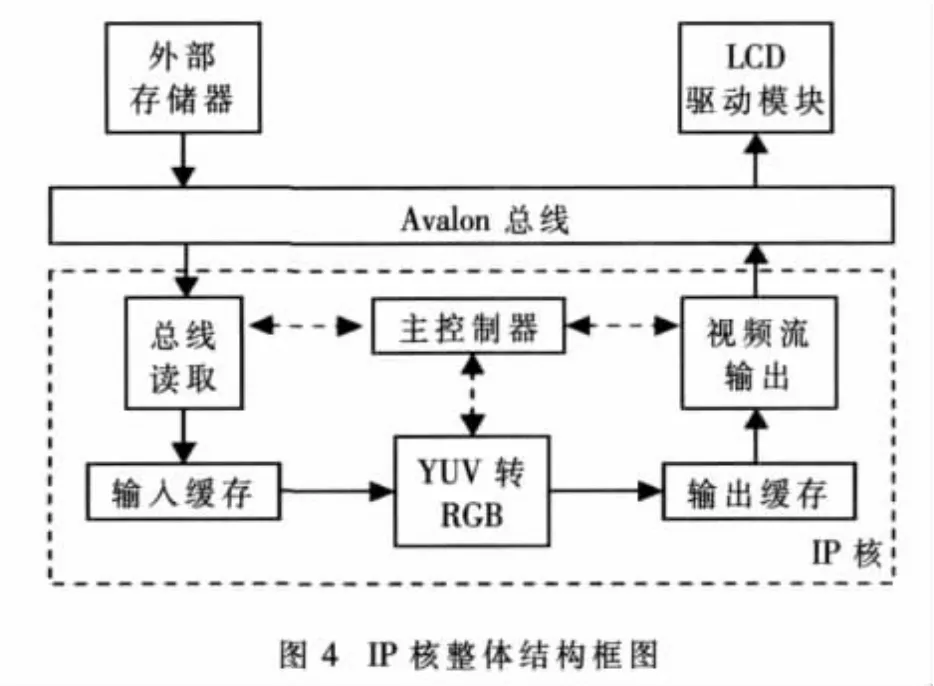

该 IP核应包含 Avalon总线读取模块,帧格式转换模块、视频流输出模块,以及控制器和控制寄存器组。如图4所示。Avalon总线读取模块用于访问 Avalon总线,从而读取外部存储器中的视频数据。帧格式转换模块完成YUV向RGB的转换,视频流输出模块用来产生满足Avalon-ST视频处理协议的视频流。

图中实线为数据流向,虚线为控制信号流向。双向箭头同时表示了主控制器的控制信号,以及被控模块的反馈信号。

2.2 Avalon总线读取模块

Avalon总线读取模块使用基于地址读写的 Avalon-MM接口,这种接口包含主端口和从端口。主端口能主动发起传输信号,从端口对传输信号进行响应,两种接口在数据传输过程中通过 Avalon交换结构相连接。Avalon总线读取模块需要读取视频数据,并能够主动对Avalon总线发起读取信号,因此应使用 Avalon-MM主端口。

当总线读取模块工作时,主控制器传入地址和读入字节数目等参数后启动该模块,该模块对总线发起数据读取操作。由于外部存储器中的视频数据为I420格式,即采样比为 4:2:0,因此每读取一行视频数据,要读取两次Y分量、一次U、V分量,这样就完成了采样比4:2:0到4:4:4的转化。该模块内部包含一个FIFO作为输入缓存,当模块从总线上读取数据后,直接将数据按读入的顺序输入FIFO,以便后续模块处理。

2.3 颜色空间转换模块

RGB和YUV两种颜色模型之间的转换可按下式计算[5]:

RGB24格式是紧缩型格式,在存储器中是按扫描顺序连续存放的,每个像素分量占8位,共24位。I420格式是颜色模型为YUV,采样比为4:2:0的平面格式。Y、U、V三个分量在存储器中分别占用单独的一片存储区域,Y分量的数目与原始帧的像素个数一致,U、V分量只是原始像素个数的1/4。把Y分量平面按2×2进行划分,相邻构成正方形的4个Y分量划为一组,每组共用一个U、V分量。例如:Y_0,0、Y_0,1、Y_1,0、Y_1,1四个分量共用U_0,0和V_0,0。

RGB24和 I420转换公式需要浮点运算,而 Verilog-HDL语言无法直接处理浮点数[6],因此设计中将原公式放大2n倍后再进行处理,然后再缩小相应的倍数。颜色空间转换模块时序如图5所示。当iDVAL信号为1时,表示输入数据Y、Cb、Cr有效,模块处理完后,oDVAL信号置1,此时输出数据Red、Green、Blue有效。

2.4 视频流输出模块

经过颜色空间转换模块处理后的数据,按顺序写入作为输出缓存的FIFO。从图6中可以看出,当dout_ready信号有效时,视频流输出模块首先发送控制数据包。输出的数据流为并行传输模式,每个周期同时传输3个记号(symbol),每个记号占 8位。将 dout_data信号改写为并行8位模式,可以看出视频流为 176×144的逐行扫描数据。

startofpacket和endofpacket分别标记了数据包的开始和结尾。控制数据包发送结束后,第二个周期开始发送视频数据;一帧视频数据完全发送完后,开始等待发送下一帧数据。

3 帧读取IP核的测试

测试平台是以Altera公司Cyclone II EP2C35F 672C8 FPGA芯片为核心的 SoPC开发平台,该平台同时配备了16 MB的 Flash、2 MB的 SSRAM以及 16 MB的 SDRAM等。搭建出使用Nios II软核处理器的SoPC系统,然后将帧读取模块作为组件接入该SoPC Builder系统。

本设计使用Quartus II 9.1进行综合与仿真,综合后的结果如表1所示。

表1 模块综合结果

通过测试发现,本文设计的IP核占用的逻辑单元略少于Altera公司的 Frame Reader IP核,可综合的最高工作频率fmax也较高,且在功能上更完善。由于 IP核具有颜色空间转换功能,减少了 Nios II软件开发的负担,因此使用该IP核开发SoPC视频处理系统更加方便、灵活,系统性能可得到进一步提升。

本文针对传统的视频处理系统,研究了一种基于Avalon-ST接口的帧读取模块的设计。该IP核突破了现有的Frame Reader模块局限,解决了传统视频处理系统的传输接口瓶颈问题。该IP核在视频处理系统的使用中,具有较大的灵活性、优越性。SoPC的IP核复用技术使得设计成果具有很强的实用性、通用性和扩展性。

[1]李兰英.Nios II嵌入式软核-SoPC设计原理及应用[M].北京:航天航空出版社,2006.

[2]Altera.Avalon Interface Specifications[DB/OL].[2009-11]. http://www.altera.com.

[3]Altera.Quartus Version 9.1 Handbook[DB/OL].[2009-11]. http://www.altera.com.

[4]Altera Video and Image Processing Suite User Guide[DB/ OL].[2009-11].http://www.altera.com.

[5]IAIN E.G.Richardson H264 and MPEG-4 Video Compression[M].John Wiley&Sons Ltd Press,2003.

[6]UWE M B.数字信号处理的 FPGA实现[M].北京:清华大学出版社,2007.

The design and application of frame reader based on Avalon-ST interfaces

DENG Chao,FU Yang

(Computer and Information Engineering Institute,Beijing Technology and Business University,Beijing 100048,China)

:Research a IP core design and applications of frame reader based on Avalon-ST interface,IP core read data through the Avalon-ST interfaces from external storage in the frame data in different formats into a video stream output.According to Avalon bus protocol and the Avalon-ST video protocol design,using Verilog HDL language module hardware design,and implementation of the module for testing.The results show that the IP core and frame reader modules provided by the Altera compared to break the existing frame reader limited to tighten format to make it function more perfect,and the IP core occupies less resources,higher operating frequency,performance been optimized,more practical.

Avalon-ST;frame reader;IP core;SoPC

TN47

A

0258-7998(2010)09-0024-04

北京市教育委员会面上项目(KM200910011008)

2010-08-15)

邓超,男,1985年生,硕士研究生,主要研究方向:嵌入式片上系统设计及视频信息处理。

付扬,女,1962年生,副教授,主要研究方向:嵌入式片上系统设计及多媒体信息处理。