基于FPGA的PCI总线接口设计

2009-07-16黎德文胡小文

黎德文 胡小文

[摘要]介绍在FPGA上实现PCI总线接口的设计方案,在主控与用户功能模块之间的进行数据交换,以突发写方式进行大量数据的高速传输。重点描述用户逻辑接口模块的程序设计,满足PCI总线时序要求,提高系统效率和性能。

[关键词]PCI总线 接口 FPGA

中图分类号:TP3文献标识码:A文章编号:1671-7597(2009)0420031-01

一、PCI总线及其接口概述

PCI(Peripheral Component Interconnect)总线即外围部件互连总线,是由Intel公司1991年首先提出的,工作频率是33Mhz,具有32bit总线宽度,理论上最大传输率为132MByte/s,比传统的ISA总线5MByte/s速率高得多。而且使用PCI总线一个突出的特点就是CPU占用率极低。在需要的高数据率和低功耗的场合,PCI总线颇受青睐。尤其是PCI SIG在1995年公布了PCI总线规范2.1版本后,PCI总线更加受到业界的重视并被越来越多的高档微机和服务器所采用。

PCI接口设计一般有两种实现方案:第一种是采用专用的PCI接口芯片实现,可以避免复杂的PCI协议,缩短开发周期,降低开发难度。但系统结构受接口芯片的限制,不能灵活地设计目标系统,且成本较高。第二种是使用可编程逻辑器件FPGA实现。这种方案可以根据整个系统的实际需要仅选择实现PCI协议的某些子集,同时将另外的一些重要的功能集成到同一个器件上,这样就使得所设计的PCI接口具有很强的针对性和灵活性,与此同时又可以极大地降低这个系统的成本。

PCI的外部设备既可以作为PCI总线从设备(Target),实现基本的传送要求,也可以作为PCI总线的主设备(Master),访问其他PCI总线设备及系统的其他的资源。ALTERA公司提供了多种不同功能的PCI MegaCore。例如:pci_mt64(支持64位的Master/Target接口),pci_t64(支持64位的Target接口),pci_mt32(32位的Master/Target接口),pci_t32(32

位的Target接口)等。因为突发读写过程,PCI总线写效率要比读效率高得多,故我们选用pci_mt32,既作为PCI总线从设备接收写数据,也可以作PCI主设备向主控写数据。

二、PCI总线在FPGA中的实现

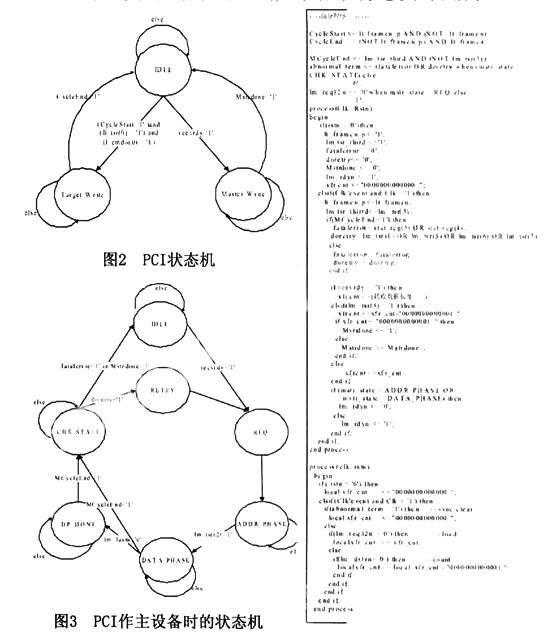

PCI总线在FPGA中的实现框图如图2所示,PCI总线在系统中主要完成主控与FPGA用户功能模块之间的数据传输。要实现PCI接口设计,我们需要做的工作是与pci_mt32相连的用户逻辑接口设计,以满足PCI总线严格的同步时序要求,实现数据的快速、有效传输。

三、用户逻辑接口设计

当主控向FPGA写数据时,用户逻辑接口模块在lt_dxfrn='0'时将接收到的数据l_dato存在FIFO里面,并在接收完数据时向用户功能模块发送transrdy脉冲信号,用户功能模块开始读取FIFO中的数据。

而当用户功能模块处理完数据后,即向用户逻辑接口模块中RAM写入数据,写完所有数据后向用户接口模块发送recvrdy脉冲信号。用户逻辑接口模块接收到recvrdy脉冲信号后向pci_mt32发送lm_req32信号,pci_mt32随后向PCI总线仲裁器发送reqn信号,并接收到有效的gntn信号后变为PCI主设备,将RAM中的数据写到主控内存。

PCI状态机如图2所示,而PCI作主设备时的状态机如图3所示。

四、传输波形

主控向FPGA写数据时,pci_mt32作从设备时的波形如图4所示。

FPGA向主控写数据时,pci_mt32作主设备时的波形如图5所示:

五、结束语

本文介绍了在FPGA上实现PCI总线接口的设计方案,在主控与用户功能模块之间的进行数据交换,以突发写方式进行大量数据的高速传输。在时钟频率33MHz下,平均数据率可达400Mb/s以上,数据传输效果很好,完全符合pci总线的要求,这种设计提供了灵活的接口控制,实现快速、可靠的数据传输。

参考文献:

[1]PCI MegaCore Function User Guide,Version 4.2December 2006.

[2]PCI Local Bus Specification,Revision 2.3,October 31,2001.