LEON2应用于数字机顶盒CPU的FPGA仿真

2009-05-12朱旭徐良波

朱 旭 徐良波

摘 要:采用免费软核LEON2作为数字机顶盒的CPU可以降低产品成本。为了使LEON2软核能更快更好地应用于数字机顶盒,选择先在FPGA开发板上建立基于LEON2处理器的一个原型,通过这个原型对硬件性能进行仿真,并且还可以在线修改程序,这样就很容易验证系统的性能,加速软件开发调试流程。经过在FPGA开发板上的仿真,对基于LEON2的系统测试取得了预期的效果。

关键词:LEON2;片上系统;嵌入式系统;知识产权核;现场可编程门阵列

中图分类号:TP368.1文献标识码:B

文章编号:1004 373X(2009)02 030 03

FPGA Simulation of LEON2 Applied to Digital Set-top Box CPU

ZHU Xu,XU Liangbo

(710 Research & Development Institute of CSIC,Yichang,443003,China)

Abstract:Selecting free IP core LEON2 for CPU of Digital Set-top Box (STB) can reduce the cost.For LEON2 applied to STB faster and better,firstly prefer to set up a prototype based on LEON2 processor on FPGA,through the prototype to emulate the hardware capability,and to modify program online,afterward validate the system capability easily,and the flow of program exploitation can be accelerated.A prospective effect of test to the system based on LEON2 through the FPGA simulation is gained.

Keywords:LEON2;system on chip;embedded system;IP core;FPGA

0 引 言

近年来,随着数字多媒体业务和Internet网络的迅速发展,新型数字机顶盒可以有效利用我国巨大的有线电视网络资源,完成视频点播、数字电视的接收及接入Internet等综合业务功能。

1 数字机顶盒总体设计方案

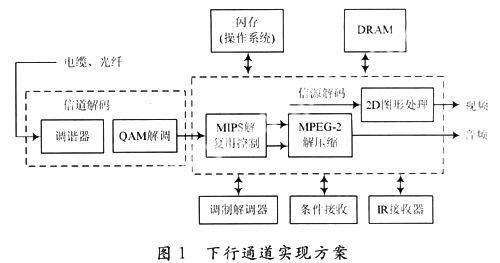

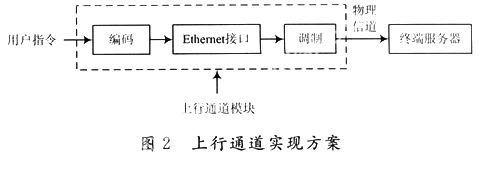

数字机顶盒分为两个通道,下行通道接收来自电缆或光纤的有线电视信号,上行通道传输从客户端到服务器端的指令。

下行通道方案如图1所示,调谐器接收来自有线网的高频信号,通过QAM解调器完成信道解码,从载波中分离出包含音、视频和其他数据信息的传送流(TS)。传送流中一般包含多个音、视频流及一些数据信息。解复用器则用来区分不同的节目,提取相应的音、视频流和数据流,送入MPEG-2解码器和相应的解析软件,完成数字信息的还原。对于付费电视,条件接收模块对音、视频流实施解扰,并采用含有识别用户和进行记账功能的智能卡,保证合法用户正常收看。MPEG-2解码器完成音、视频信号的解压缩,经视频编码器和音频D/A变换,还原出模拟音、视频信号,在常规彩色电视机上显示高质量图像,并提供多声道立体声节目。

上行通道方案如图2所示,用户发送指令,然后经过编码符合网络通信协议,从以太网接口传输到调制器,再经物理信道传给终端服务器。

2 LEON2处理器

嵌入式CPU是数字电视机顶盒的心脏,当数据完成信道解码以后,首先要解复用,把传输流分成视频、音频,使视频、音频和数据分离开。CPU是嵌入式操作系统的运行平台,它要与操作系统一起完成网络管理,显示管理、有条件接收管理、图文电视解码、数据解码、视频信号的上下变换等功能。

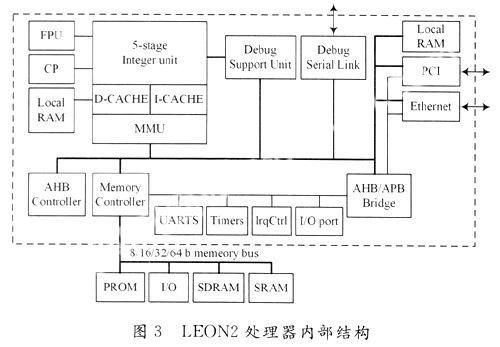

LEON系列32位RISC处理器核的第一个版本是LEON1,它是由欧洲航天局主持设计开发的。LEON1的设计初衷是为了使欧洲能够摆脱在航空航天高性能嵌入式处理器上对美国的严重依赖。以Jiri Gaisler为首的设计团队在完成LEON1后从欧洲航天局独立出来,成立了Gaisler Research 公司,后来就推出了LEON2处理器。LEON2是一个可配置的微处理器核,使用SPARC V8指令集,它的源代码由可综合的VHDL代码构成。LEON2内部结构如图3所示。

LEON2的整数处理单元是5级流水线设计,采用SPARC V8(IEEE-1754)指令和体系结构,具有分离的数据Cache和指令Cache。LEON2的整数单元包括一个可选的16×16 的MAC单元,能够完成基本的DSP运算,同时还提供了浮点运算单元(FPU)的接口和协处理器(CP)的接口,可以扩展浮点运算和DSP处理。LEON2选用了ARM公司的AMBA 2.0片上总线标准,用于连接内存控制器、定时器、中断控制器、UART接口、PCI接口、10/100 Mb/s以太网接口等模块。LEON2同时还提供1个调试支持单元和1个调试串口,用于支持片内调试。LEON2的一个非常重要的特点就是具有很好的可配置性。使用者根据自己的需要,通过一个用tcl/tk脚本编写的图形化界面,对LEON2内核的绝大多数模块进行配置,比如可以配置Cache的大小和访问方式,是否支持硬件乘/除法,是否需要内存。

Gaisler Research 公司还提供了比较完善的基于LEON2的GNU软件开发环境。使用者可以使用TSIM或GRMON进行LEON内核的调试仿真。LECCS是专门针对LEON的交叉编译系统,可以进行C/C++的编译和调试。SnapGear Linux是基于LClinux的实时Linux内核,它的LEON版提供了对LEON处理器的全面支持,可以支持MMU和NOMMU等不同配置方案。

由以上描述可以看出,LEON2具有强大的硬件配置和完备的软件开发环境支持,可以承担数字机顶盒CPU要求的各种信号处理任务。

3 在FPGA开发板上建立LEON2的SoC平台

3.1 硬件平台的建立

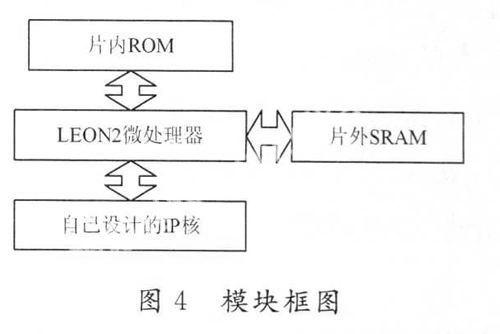

图4就是基于LEON2的平台的模块框图。LEON2处理器作为核心部分,片内ROM存放Monitor负责系统初始化和将程序拷贝到片外SRAM内的任务,片外RAM是FPGA开发板上Memory,用来存放程序和数据。设计的IP核通过AHB总线和LEON2相互交互。

FPGA开发板主要有以下资源:50 MHz有源时钟;1块Altera公司的核心FPGA芯片EP2C20F484C8,逻辑单元18 752个;2片512 KB的IS61LV25616AL SRAM芯片组成32 b宽共1 MB容量,其中每片设计为可兼容1 MB,总共最大可扩充到2 MB;JTAG接口(通过JTAG接口可以从PC机上对EP2C20F484C8进行编程);串口与计算机COM1相连,可以用于程序下载。

将配置好的LEON2的VHDL代码,加入设计的HDL代码,一起使用Synplify综合工具生成FPGA的网表文件;然后使用Quartus进行布局布线,将LEON2核同片内ROM和片外SRAM连接,布局布线完成后生成相应的SOF文件;通过JTAG端口将SOF文件下载到片子上去,对FPGA硬件进行配置,最后占用 FPGA资源是5 800个逻辑单元,可以达到的时钟频率最大为46 MHz。

3.2 软件设计

由于Quartus软件可以预先配置EP2C20F484C8片上ROM,所以可以在LEON2的片上ROM预先配置好的1 KB大小的Monitor软件。Monitor的主要作用是在LEON2系统reset初始化时首先对处理器初始化,对LEON2的存储配置寄存器进行配置;然后向UART口发送启动信息;等待UART信息。当软件部分使用交叉编译器LECCS在PC上编译完毕后, PC机通过UART口和FPGA开发板相互通信,就可以将编译好的srec文件下载到FPGA开发板上,放置在片内ROM里面的Monitor程序就读入程序的内容以及程序的起始地址。开始Monitor将srec程序拷贝到SRAM程序区,等全部程序下载好以后,Monitor最后1条程序就会自动跳转到程序的起始位置,执行SRAM里的程序。这样就可以反复修改程序,反复下载程序,便于软件的开发和调试。

4 结 语

通过将片上系统映射到FPGA,这样可以在接近运行速度的前提下,验证硬件和软件。这样不仅为软件部分能尽早地进行开发与调试工作提供了原型,同时也可以在实际运行中发现一些在系统设计中没有注意的地方。最终可以缩短设计周期,同时为ASIC设计一次成功提供了更大的把握。

在FPGA开发板上建立基于LEON2处理器的SoC平台后,使用这个原型系统,就可以很容易验证系统的性能,并且加速软件开发调试流程。

参考文献

[1]Gaisler Research.LEON2 Processor User′s Manual (XSTEdition),Version 110127,2005.

[2]邵洋,单睿,张铁军,等.基于可配置处理器的SoC系统级设计方法[J].计算机工程与应用,2006,42(26):96-98.

[3]张雁,曾田.VHDL及高层综合[J].计算机与数字工程,2003,31(3):67-69,36.

[4]刘军,郭立,郑东飞,等.开放性32位RISC处理器IP核的比较与分析[J].电子器件,2005(4):158-162.

[5]Altera Corporation.Nios Embedded Processor Development Board.2002.

[6]LEON DSU Monitor User′s Manual(Version 1.0.11).2003.

[7]ALTERA Corp.Excalibur Embedded Processor Solutions:Nios.2002.

[8]RAJSUMANR.System on a Chip:Design and Test[M].Artech House,2000.

[9]MOURADS.Principle of Testing Electronic System[M].John Wiley & Sons,Inc,2000.

[10]林金永.面向SOC的设计方法研究[J].航天控制,2004,22(2):68-71.

[11]陈秀玲,周欣,陈黎平.新的片上可编程系统(SOPC)解决方案Nios[J].今日电子,2003(7):10-12.

[12]雷绍充,梁锋,邵志标.对SoC芯片全面验证的仿真结构的研究[J].半导体技术,2004(4):114-117.