基于AD9230的高速信号处理器

2009-04-29杨宝华

摘要:介绍了一种基于AD9230的高速信号处理器,给出了系统实现的具体方案,并对各部分硬件电路的设计进行了阐述。该信号处理器可以在硬件平台不变的情况下,通过改变软件程序即实现不同功能并应用于不同的系统,具有较高的通用性和实用价值。

关键词:高速信号处理器 FPGA 软件无线电

1.引言

随着电子技术的发展,高速A/D转换器件以及高速信号处理芯片的推陈出新,高速信号处理器具有处理速度快、灵活、精确、抗干扰能力强、体积小及可靠性高等优点,满足了对信号快速、精确、实时处理及控制的要求[1]。

本文主要采用了ADI公司生产的高速A/D模数转换器AD9230实现信号的采集,利用ALTERA公司生产的Stratix系列器件EP1S60完成信号的预处理,最后利用TI公司定点DSP芯片TMS320C6202完成高速信号处理算法的实现。

2.系统工作原理及组成

该高速信号处理器的系统组成框图如图1所示,主要包括了系统时钟产生电路、信号调理电路、模拟数字转换电路、FPGA及其外围电路以及DSP电路。具体的高速信号处理器原理框图如图1所示。

2.1 时钟电路设计

ADF4360芯片提供8 /9或16 /17两种计数模式,一般情况下,当输出频率较高的时候选用16 /17计数器,输出频率较低的选用8 /9计数器。其中f0进行A 次(P+1)分频和(N-A)次P分频[2],最终输出f0=[(P×B)+A]×fDDS/R。根据该芯片的配置时序以及上述公式,选择参考时钟为12MHz,最终输出200MHz,按公式计算出各个参数后,通过对R、C、N三个寄存器写24bit控制字即可完成配置。由于该系统中CN=10uF,因此C寄存器和N寄存器之间的时间间隔T必须满足T≥10ms[3]。

2.2 AD采样电路

AD9230是ADI公司推出的一种12位、250MSPS的高速、低功耗A/ D转换器。AD9230具有片内基准电压和跟踪和保持,两个并行LVDS输出模式(ANSI-644和IEEE 1596.3降范围连接),以便更好和FPGA接口,而双数据速率(DDR)模式能减半所需并行输出数。DDR以及IEEE 1596.3降低了连接LVDS范围选择,进一步把功耗降低到385 mW[4]。

2.3 FPGA电路设计

该设计中FPGA采用的是ALTERA公司Stratix系列器件EP1S60。Stratix系列FPGA是ALTERA公司于2002年新推出的高密度FPGA器件,基本结构主要包括:逻辑阵列块(LABs),每个逻辑阵列块由10个逻辑单元(LE)组成,LABs用于实现用户设计的逻辑功能;输入输出块(IOBs),IOBs提供封装引脚和LAB之间的接口,LABs利用一个通用的布线矩阵实现互连。此外,Stratix系列器件结构还包括以下与布线矩阵相连的一些电路:TriMatrix存储块,时钟延迟锁相环(PLL)[5]。

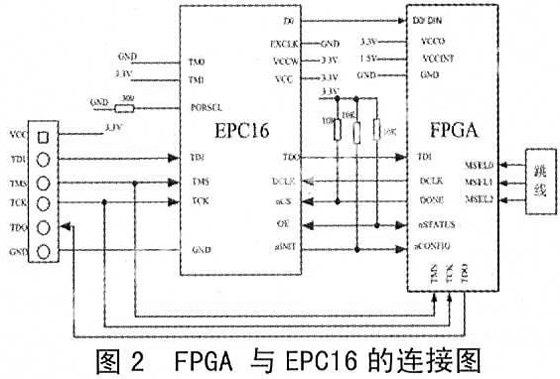

该设计中配置器件EPC16采用被动串行方式加载FPGA,用下载线单独加载FPGA 时,Mode选项用JTAG方式;用下载线单独加载EPC16时,Mode选项可以在JTAG方式和被动串行方式之间选择,具体FPGA 与EPC16的连接如图2所示。

2.4 DSP电路设计

该系统DSP采用的TI公司定点TMS320C6202,C6202能否正常工作,从原理角度来分析只与芯片本身一些信号的设置有关系。TMS320C6202整个EMIF外部空间最大容量为64MB,处理器内部将它分成四个子空间,并对每个子空间提供独立的选通信号,即CE0-CE3。当处理器设置为ROM引导时,上电后首先从CE1空间读取64KB数据到地址0处,然后程序从地址0处开始执行,所以引导FLASH必须配置在CE1地址空间。TMS320C6202有两种存储器映射方式:MAP0和MAP1。通过扩展总线的XD[4..0]利用上拉/下拉电阻进行复位时的芯片启动模式设置。系统中将存储器映射方式设置为1,即地址0处的存储器在内部,芯片自加载方式为8bitROM方式[6]。

3.结论

本文介绍了一种基于AD9230的高速信号处理器的设计与实现,该设计基于软件无线电设计理念,利用高速A/D转换器实现信号的采集,同时该设计中采用了高端的FPGA实现信号的预处理,由于FPGA具有设计灵活、可编程的特点,因此,可以采用硬件描述语言实现部分复杂的算法,其处理速度方面具有较高的性能。利用DSP最终实现高速信号处理器中的复杂算法。基于AD9230的高速信号处理器具有较强的通用性,可广泛应用于各种工程领域,具有一定的应用价值。◆

参考文献:

[1] 蒲凯,陈福深,龚赤坤. 基于FPGA的高速信号处理系统设计与实现[J],电子元器件应用,2008.10

[2] 林巧莉.基于ADF4360系列的小型化频率综合器设计 [J]. 电讯技术,2008.10

[3] 张星 周克生. 基于ADF4360-7的频率合成系统 [J].世界电子元器件,2007.2

[4] 沈琰 李龙江. AD9240及其在中频数字化接收机中的应用[J],科学技术与工程,2009.2

[5] 丁智青,王春峰,杨辉. 某宽带一维成像系统的FPGA设计技巧[J],电子工程,2007.4

[6] 黄斌,李晓明,王晶.基于TMS320C6202B的100M超高速数据采集系统[J],仪器仪表用户,2004.11

作者简介:杨宝华(1982-),男,蒙古族,内蒙古鄂尔多斯,西北民族大学计算机科学与信息工程学院(二级单位),学生,专业计算机科学与技术。