高速图象采集卡设计

2009-04-29佟大鹏刘丹

佟大鹏 刘 丹

摘 要:现代化生产和科学研究对图像采集系统的要求日益提高。传统的图像采集卡速度慢、处理功能简单,不能很好地满足特殊要求,因此,我们构建了高速图像采集系统。它主要包括图像采集模块、图像低级处理模块以及总线接口模块等。这些模块是在FPGA中利用VHDL编程实现的。由于VHDL设计灵活、编程方便,易于在FPGA中实现并行运算和流水线结构;所以,高速图像采集系统的速度快、适应性好。

一、系统设计

本系统中专用视频处理器采用Philips公司的可编程视频输入处理芯片SAA7111A。它通过简洁的I2C总线与其它器件和设备连接可以将视频信号转换为多种格式的数字号。

最复杂的信号莫过于视频信号。视频信号中除了包含图像信号之外,还包括了行同步信号、行消隐信号、场同步信号、场消隐信号以及槽脉冲信号、前均衡脉冲、后均衡脉冲等。因而,对视频信号进行A/D转换的电路也非常复杂。Philips公司将这些非常复杂的视频A/D转换电路集成到了一块芯片内,从而生产出功能强大的视频输入处理芯片SAA7111A,为视频信号的数字化应用提供了极大的方便。

二、工作原理

系统复位完成FPGA程序加载后,先由FPGA的I2C总线模块对SAA7111初始化,本系统中SAA7111A的初始设定为:一路模拟视频信号输入、自动增益控制、625行50Hz 、PAL制式、YUV422 16bits数字视频信号输出、设置默认的图像对比度、亮度及饱和度。之后等待采集图像的命令。初始化成功后,SAA7111实时处理模拟视频信号,输出亮度和色度信号,同时输出点时钟信号,行、场同步信号,行、场参考信号,奇偶场标志信号等。本系统使用灰度图像,没有使用色度信号,所以数据线为8位

系统采集图像的命令由计算机发出,启动FPGA的采集同步模块。采集同步模块发出采集标志信号,采集一帧图像,通过写数据模块产生写地址和写信号将数据存储到SRAM中。采集结束时,采集标志信号撤消,采集同步模块复位,等待下一次采集命令。FPGA处理完1帧图像数据后,通过读数据模块生产读地址和读信号来实现将SRAM中的图像信息读出并通过PCI总线传送到计算机中。

在图像采集过程中,我们使用的是512×512的图像,即一帧图像采集512行,奇数场和偶数场各采集256行,每一行采集512个像素。因此,需要通过行延时模块进行行选择,滤掉无效行,通过像素延时模块进行像素选择,以选择需要的像素。[4]

三、用VHDL硬件描述语言完成采集控制模块的行为描述

采集控制模块又包括几个子模块。因为SAA7111采用的是I2C总线,所以采集控制模块应包括:模拟I2C总线模块、采集同步模块、SRAM读写模块。

1.利用I2C协议对SAA7111配置的具体实现

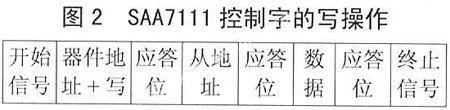

使用FPGA模拟的I2C接口可以对SAA7111提供的多个控制字进行读写,从而完全控制SAA7111的运行。对SAA7111的控制字的写过程如图2所示。

I2C协议中器件地址是7位,加上读写位构成一个完整的字节。SAA7111的器件地址是0100,101,加上读写位后:器件地址+写=0100 1010即4AH;器件地址+读=0100 1011,即4BH。从地址是器件内部分配的地址。SAA7111提供了00~1F、40~62共43个控制字。SAA7111读控制字的过程如图3所示。

I2C协议中的读操作比写操作复杂:首先完成对器件地址和从地址的写操作;然后发送4BH,可以开始接收数据;数据传输结束时发送终止信号。

编写VHDL语言如下:

library ieee;

USE ieee.Std_Logic_1164.all;

LIBRARY lpm;

USE lpm.lpm_components.all;

process(nReset,eclk)

begin

if(nReset='0')then

int<='0';i_ack_r<='0';

elsif(eclk'vent and eclk='1')then

if(nce='0'andnAwe='0')then

if(core_en='1'and eadd="001")then

--写入命令寄存器

i_ack_r<=cr(47);

end if;

else

i_ack_r<='0'; --自动清除

end if;

int<=cmd_done_ack and ien;

end if;

Eint<=int and(not i_ack_r_;end process;命令码

采集同步模块

整个图像采集部分是一个VHDL语言文件。FPGA采用串行主模式,从SPROM中读取配置数据,完成自身配置。Set_sample.vhd采集同步模块,它是图像采集部分的一个块语句,输入输出信号为:

pcicon0-IN,启动采集图像信号;

vref-IN,场参考信号;

rts0-IN,奇偶场标志信号;

sig_frame-OUT,采集同步输出信号,高电平有效,用于图像采集和总线管理模块;

sig_field-OUT,采集同步场参考信号,采集1帧图像的场参考信号。

源程序如下:

set_sample:block

signal flagct:std_logic_vector(2 downto 0);

begin

process(pcicon0,vref)

begin

if(pcicon0='O')then

flagct<="01";

elsif(vref 'event and vref='1')then

if(flagct="001"and rts0='1')then

flagct<="010";

elsif(flagct="010")then

flagct<="011";

elsif(flagct="011")then

flagct<="100";

end if;

end if;

end process;

process(flagct)

begin

if(flagct="010" or flagct="011")then

sig_frame<='1';

else

sig_frame<='0';

end if;

end process;

sig_field<=sig_frame and vref;

end block;

当pcicon0引脚再现大于等于场周期(20ms)的低电平信号时,可以确保该模块处于触发状态,在下一个奇数场出现时,(rts0=1),根据SAA7111的场参考信号产生具有两场时宽的采集同步信号(sig_frame)。该信号有效时为图像采集阶段,对SRAM1写入数据;该信号撤消时采集同步模块自动复位,等待下一次采集命令,同时FPGA1开始读取SRAM1中数据进行处理。采集同步信号有效的同时输出采集同步场参考信号,用于采集图像数据。◆