基于Verilog计算精度可调的整数除法器的设计

2009-03-19叶显阳张海勇皮代军秦水介

叶显阳 张海勇 皮代军 秦水介

摘 要:传统整数除法算法采用多次相减的方法来实现运算,相减的过程耗费了大量时钟脉冲,而且对运算结果的最后一位没有进行处理。针对传统的整数除法器,提出一种基于Verilog计算精度可调的整数除法器的设计方法,运用移位、循环减法和四舍五入的方法对数据进行处理,提高了处理速度和精确度。用Cadence公司的NC-Verilog仿真器对所设计的除法器进行仿真验证,结果显示该除法器达到了预期功能。

关键词:整数除法;Verilog;处理速度;精确度

中图分类号:TN402文献标识码:B

文章编号:1004-373X(2009)03-146-02

Design of Integer Divider with Adjustable Precision Based on Verilog

YE Xianyang,ZHANG Haiyong,PI Daijun,QIN Shuijie

(Laboratory for Photoelectric Technology and Application in Guizhou Province,Guiyang,550025,China)

Abstract:Traditional integer division algorithm used many subtraction to achieve the operation,the process by spending a lot of clock pulse,but also the results of the operation did not deal with the last one bit. Due to the traditional integer divider,an integer divider with adjustable precision based on Verilog is designed in this paper. The process velocity and precision of the divider are improved by using the methods of circulating subtracting and rounding to process data. The simulation for the divider is carried out by the NC-Verilog of the Cadence Company and the results indicate the good function.

Keywords:integer division;Verilog;process velocity;precision

基金项目:教育部“优秀青年教师资助计划”(教人司[2003]355);留学回国人员科研启动基金;2006年度教育部博士点基金项目;贵州省优秀青年科技人才培养计划基金(合同号:黔科合人字No.2013)

0 引 言

除法器是电子技术领域的基础模块,在电子电路设计中得到广泛应用。目前,实现除法器的方法有硬件实现和软件实现两种方法。硬件实现的方法主要是以硬件的消耗为代价,从而有实现速度快的特点。用硬件的方法来实现除法器的研究很多,如利用微处理器实现快速乘除法运算,FPGA实现二进制除法运算,模拟除法器等[1-5];而通过软件实现的除法器算法,可以大大提高器件的工作频率和设计的灵活性,可以从总体上提高设计性能,而设计高效实用的算法是除法器的关键,故除法器的算法研究成为现今热点。

目前,软件方面主要是通过减法算法来实现除法运算,把被除数作为被减数,除数作为减数,作减法,直到被减数小于减数为止,记录能够相减的次数即得到商的整数部分。将所得的余数乘以10 作为被减数,除数作为减数,作减法,差重新置入被减数,反复相减,直到被减数小于减数为止,记录能够相减的次数即得到商的十分位数值。依此继续下去,可得到商的百分位数值,千分位数值,……,要精确到哪一位,就依次做到哪一位[6,7]。此方法的缺点是速度慢,而且最后一位的精度不高,为了克服以上的缺点,这里设计一种算法在软件上改进了除法器运算的准确性和处理速度。

1 设计方法

对于任意给定的两个整数fenzi和fenmu,设fenzi为被除数,fenmu为除数。为了得到两个数相除的十进制结果,本设计主要通过下面的算法来实现,假如要保留小数点后面的n位有效数字,首先把fenzi乘以10的n次方,赋值给寄存器变量data0;接着把fenmu分别乘以10的(n+m),(n+m -1),(n+m -2),…,1,0次方分别赋值给(n+m+1)个不同的变量data(n+m+1),data(n+m),…,data1,其中m是fenzi和fenmu的位数之差(当fenzi的位数多于fenmu时,m为正,否则为负);先求出商的最高位的值,如果data0大于data(n+m+1),则计数器自动加1,再把data0和data(n+m+1)的差值赋给data0,再相减直到data0的值小于data(n+m+1),此时计数器的计数值就是最高位的值;依此用同样的方法继续下去,就可得到各个位上的值[8-10]。对最后一位进行四舍五入处理,当相减后的data0<data1时,再通过比较data0*2是否大于data1,如果大于data1,则最后一位计数器的值加1,否则不变,最后把得到的整体值除以10的n次方,也就是小数点往左移动n位。传统除法算法由于采用多次相减的过程来实现,相减的过程耗费了大量时钟脉冲,而且对运算结果的最后一位没有进行处理;而本设计是通过采用位扩展使除数和被除数位数相同,进而对每一位进行分开处理,减少了做减法运算的次数,从而提高运算速度;同时采用四舍五入的方法对运算结果进行处理,提高准确性。

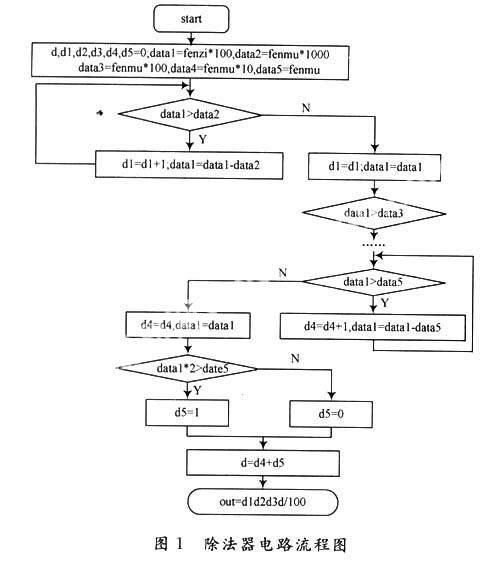

上面算法是一种顺序方式,用Verilog硬件描述语言很容易实现,图1为流程图,其中假定fenzi为3位的整数,fenmu为2位的整数,除法运算精确到百分位。

2 仿真结果及分析

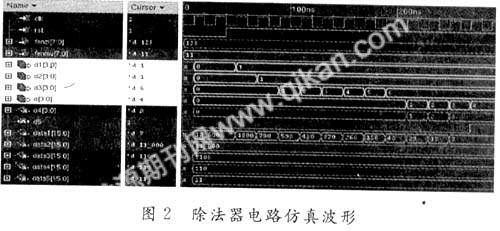

对上述的流程图用Verilog描述语言编程,在Cadence的NC-Verilog仿真器下仿真,设输入的fenzi和fenmu的值分别为128和11,仿真波形如图2所示。

从图2的波形可以看出,输出结果为1 164,除法运算要精确到百分位,所以往左移动2位,其最终的值为11.64,而实际的值为11.636 36……,经过四舍五入得到的结果完成正确。从仿真时间来看,对于相同的数值输入,本设计只用了12个脉冲,而普通除法器至少需要20个脉冲(128/11=11余7,70/11=6余4,40/11=3余7,11+6+3=20),相比之下本设计的除法算法有很大的优势。

然而对于两个位数相差很大的数相除,则本设计的速度优势更加的明显,本设计每一位的运行时间都不会超过9个时钟脉冲,因此进行n位计算的总脉冲也不会超过9n个,而传统的除法运算需要多个时钟脉冲,一般会是本设计时钟脉冲的数倍。该算法同样适合小数的运算,只要把小数化成整数,再做同样的处理,就可以得到精确的结果。

3 结 语

通过对除法器算法的改进,用四舍五入的方法对数据进行处理,使得到的结果准确性有了进一步的提高;运用移位、循环减法,实现数据的高速运算,并能任意设定计算的精度。运用此方法在软件方面设计除法器对速度和准确性的提高有积极意义。

参考文献

[1]王江,黄秀荪,陈刚,等.一种RISC 微处理器的快速乘除法运算设计与实现[J].电子器件,2007,30(1):162-166.

[2]祁建海,贺知明.基于FPGA的16位定点复数的快速求模[J].电讯技术,2005(6):210-212.

[3]刘慧英,戴春蕾,高茁.高性能除法电路仿真与实现[J].仪表技术与传感器,2006(6):38-39.

[4]白永强,沈绪榜,罗旻,等.一种高阶除法器的设计与实现[J].微电子学与计算机,2006,23(1):64-66.

[5]黄秀荪,叶青,仇玉林.高速除法器设计及ASIC实现[J].微电子学与计算机,2008,25(2):133-135.

[6]高茁,张泾周.高性能数字运算单元设计研究[D].西安:西北工业大学,2005.

[7]陈玉丹,齐京礼,陈建泗.基于VHDL的8位除法器的实现[J].软件时空,2006,22(13):277-278.

[8]华东.一种新的除法器算法的研究[J].浙江工贸职业技术学院学报,2006,6(3):60-65.

[9]朱卫华,郑留平.可任意设定计算精度的整数除法器的VHDL设计[J].理论与方法,2008,27(2):16-18.

[10]朱维乐,钱贵锁,杨刚,等.高速整数开方电路的流水线设计[J].电子科技大学学报,2008,37(2):229-231.

作者简介 叶显阳 男,1982年出生,浙江人,微电子学与固体电子学专业,贵州大学在读研究生。研究方向为数字集成电路。

张海勇 男,1981年出生,河北人,微电子学与固体电子学专业,贵州大学在读研究生。研究方向为数字集成电路。

皮代军 男,1983年出生,贵州人,微电子学与固体电子学专业,贵州大学在读研究生。研究方向为数字集成电路。

秦水介 女,1963年出生,教授,博士,博士生导师。主要从事微电子机械系统,激光与光电子技术研究。