透过专利看微处理器的技术发展(十)

2009-01-20徐文苑武晓岛谢学军

徐文苑 武晓岛 谢学军

摘要:在对几个重要EDA公司关于低功耗相关专利的调研基础上,本文分析了EDA行业的主要公司Cadence、Synopsys、Magma的低功耗技术,着重分析了Cadence的相关专利,包括申请年代与UPC分类,为了解EDA中的低功耗技术,进行产品研发提供线索和思路。

关键词:专利文献;EDA工具;低功耗

1引言

随着超深亚微米技术和系统芯片技术的日益成熟,便携式电子产品获得了迅猛的发展和快速的普及,开发周期也越来越短,对开发和生产成本的制约也日趋严格,对性能要求也越来越高。便携和无线通讯消费电子设备的功耗考虑已经成为很多产品规范的主要考虑因素。即便是有线设备以及在过去电池电力不成问题的其它产业领域,封装、稳定性和冷却成本也使得功耗成为更小尺寸工艺中的突出问题。特别是当设计转向90 nm以下工艺节点之后,功耗管理成为整个设计和制造链中的一个重要考虑。

功耗问题在集成电路设计中并不是一个新问题。从早期双极型晶体管的广泛使用到如今CMOS电路成为集成电路设计的主流,功耗一直是促成集成电路变革和发展的主要原因之一,但是当工艺节点进入90nm后,晶体管在亚阈值区的漏电流问题日益凸现,CMOS静态功耗骤增,功率管理开始成为一个重要的考虑因素。当工艺节点不断减小,即进入45nm以后,栅极氧化层厚度越来越薄,栅极漏电流增加,漏电流现象更加严重,功耗也会因此陡增。CMOS电路的低功耗优势面临着挑战,功耗又一次成为了阻碍集成电路持续发展的问题所在。

目前来看似乎还没有一种新的工艺可以马上解决低功耗的问题,电路结构、流水线、存储系统、总线、并行处理、编译、操作系统以及算法和应用程序设计等方面,都需要考虑降低功耗的方法。这就迫使业界必须从集成电路的设计初期就开始采用低功耗设计技术。但是现在产品设计的时间短,上市时间(time to market)紧迫,而这一重要因素能决定产品成败,因此最好在设计早期进行有效的功率评估,借助有效的EDA工具来完成低功耗设计能保证面市时间。因此下面我们就对几家重要的EDA生产商的技术及专利进行分析。

2EDA中的低功耗技术及专利

由于设计上的复杂度及缺乏EDA自动化手段的原因,长期以来设计师只能采取手工分析的方法来解决功耗问题,这样的方法由于缺乏灵活性,使得效率低下,上市时间长,芯片故障风险高,功耗及性能之间难以权衡。因此借助于EDA工具来完成自动化设计是非常必要的。

Cadence、Synopsys、Magma这几家公司的产品在EDA行业内占据有主导地位,他们的低功耗解决方案各有异同,在EDA工具的低功耗的相关专利中,Cadence公司的数量最多,其次是Synopsys和 Magma。其中Cadence公司在低功耗技术上共有34件专利,Synopsys共有5件低功耗专利,这包括被它收购的Synplicity和Avanti的低功耗专利,Magma是近几年兴起的EDA公司,但是唯一一家为客户提供数字 IC 热分析工具的供应商,该工具集成在Blast-Rail产品中,相关专利共有4件。本文将主要以Cadence的34件低功耗专利为样本来分析EDA工具的低功耗技术解决方案的发展。

3Cadence 的低功耗技术与专利

3.1 Cadence的低功耗技术

Cadence 的 低功耗解决方案(Low-Power Solution)是第一套完整的低功耗芯片设计、验证和实现的解决方案。而Cadence也成为首家能向设计师提供在寄存器传输级自动实现低功耗技术的解决方案的EDA公司,并保证能够在验证、前端实现和物理实现步骤的全过程使用一个通用的格式正确执行(如图1所示),它能满足设计工程师在较短的设计周期内追求低功耗的迫切要求,同时通过极高的测试覆盖率保证产品质量。这种解决方案可以看做一个集成环境。其中,Cadence的“Power Forward Initiative,PFI”工具通过使用CPF格式来实现低功耗设计。CPF是在设计过程初期详细定义节约功耗技术的标准化格式,从设计到验证再到实现均可标识,从而保证了整个流程的一致性。该解决方案既避免了费时费力的人工操作,也大大降低了与功耗相关的芯片故障,并在设计过程初期提供功耗的可预测性,促进了IP复用。而基于SystemVerilog的“开放式验证方法学(Open Verification Methodology,OVM)”是Cadence最新一代的高速硬件加速与模拟技术,Cadence Incisive功能验证及Encounter数字IC设计平台等,都是Cadence低功耗解决方案的重要组成部分。CPF是可在设计初期详细定义功耗架构的标准化格式,因此在设计流程初期就可提供功耗的可预测性,这对降低日益增长的设计成本及流片一次成功非常有利。将这种方法应用于低功耗设计,能降低风险,将手动调整的需要降到最低,使用强劲的验证方法,设计团队可以消除源自功能和结构缺陷的芯片故障风险,带来更高的效率和更短的上市时间,主要是指通过在流程中减少迭代次数,并控制芯片的重新投片,设计团队可以有效解决上市时间问题。还有就是改进的芯片质量(QoS):通过流程初期易于使用的“假设”探索,设计师可以确定最理想的功率结构,以实现目标规格。随后,实现流程中的优化引擎能够对时序、功率和面积目标进行最适当的权衡。

从2007年伊始,围绕针对低功耗IC设计的标准,两大EDA阵营就展开了激烈竞争。一方是由Cadence公司开发,Si2(Silicon Integration Initiative)的低功耗联盟(LPC)管理的CPF;而另一方则是由Synopsys、Mentor Graphics和Magma Design Automation公司支持的UPF。UPF和CPF都允许用户在整个RTL-to-GDSII设计流程中定义功率设计意图和约束条件,并且二者的实现方法也非常相似。

3.2 Cadence早期的低功耗专利

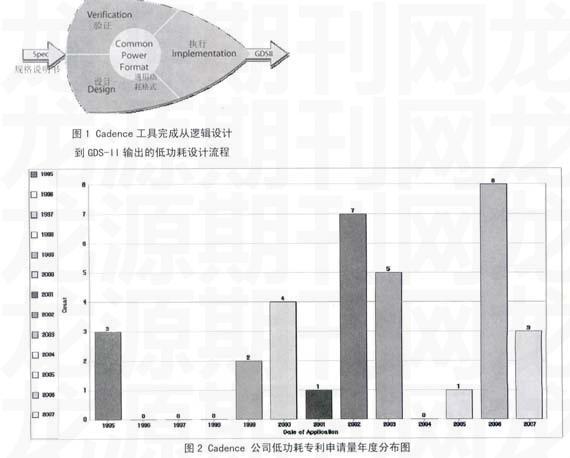

通过使用数据库检索得到Cadence降低功耗的专利共有34件,图2为Cadence公司的低功耗设计专利的申请年份分布图,以1999年为界限将专利分为两个阶段,在1999年之前仅有三件低功耗的专利;从1999年开始,关于低功耗专利的数量开始增加,除2004年以外,几乎每年都有一定数量关于低功耗的专利,到了2006年,仅是EDA中低功耗技术的专利数量就达到8件,可见cadence公司在推广低功耗技术解决方案的同时,也开始进行相关技术的专利布局。

1995年Cadence公司曾申请了三个关于EDA工具中降低功耗的专利,并于1997年获得授权,通过分析发现这三个专利的主要发明人相同,分别是Saldanha Alexander、McGeer Patrick,发明内容近似。这三件专利都是优化在门级电路综合时对输入端充电的功耗,所使用的功耗模型也相同,每个门电路输出端的功耗与扇出的个数成正比。

专利US5649166的发明点在于设计一个仲裁选择电路和一个仲裁门电路,该方案适用于有至少两个主要输入端的电路,仲裁门电路耦合到电路的主要输出端,该电路耦合到输入端,当冲裁电路重新选择时,重要门电路则耦合到新的输入端。专利号为US5696692的专利发明点是设计了一个条件选择的电路,包括一个两位的“或”树,和一个与门,将与门耦合到“或”树和主要输入端。通过加入仲裁电路或者条件选择电路的导通,控制晶体管的动态功耗。专利号为US5682519的专利也是通过电路控制开关节点的功耗。

这三件专利十分相似,但是从不同的角度来控制电路中晶体管消耗的能耗,可见Cadence公司对这一技术的保护力度。

3.3 Cadence近年来的低功耗技术

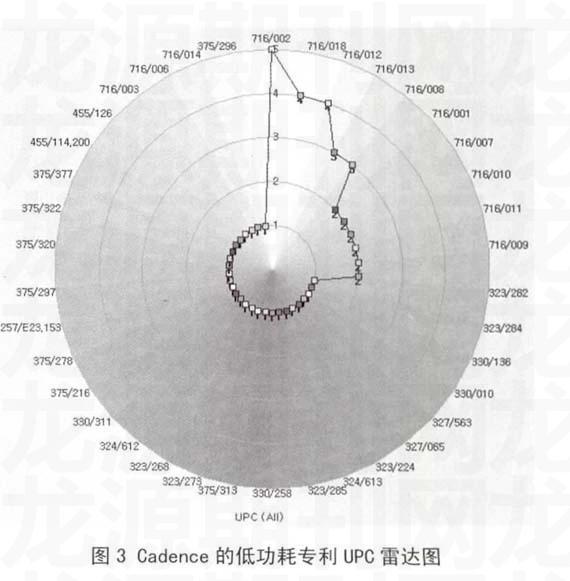

1999年后Cadence申请的专利被划分为近年来cadence的低功耗技术,这些专利最大的特点在于数量多,内容分布广泛,通过UPC分布的雷达图就能看出。发明点设计低功耗技术中的各方面,从系统级设计方法,到晶体管的功耗模型评估,从仿真到验证都有涉及。专利覆盖的范围与前面分析的Cadence公司正建立起一套完整的低功耗方案这一趋势是吻合的。

4Synopsys的低功耗技术与专利

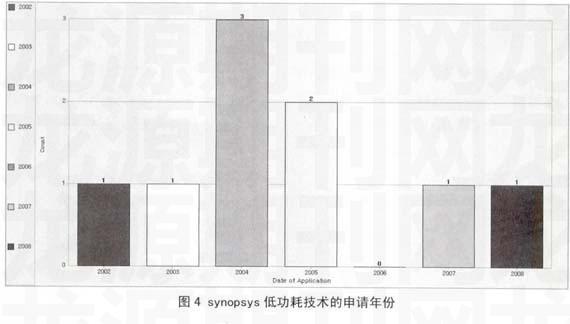

Synopsys的低功耗技术相对比较少,资料显示Synopsys曾收购了Avanti,和Synplicity公司,因此对这两家公司的相关专利进行检索。共得到9件专利。

Synopsys的专利集中在多电压、是否采用电源关断、采用片上还是片外电源管理、低功耗IP的选择等方面。在这阶段的评估,一方面是通过对过往系统的评估经验,一方面可以通过快速原型设计,对设计原型进行功耗估算。

5Magma公司的低功耗技术与专利

MAGMA公司是唯一一家为客户提供数字IC热分析工具的供应商,该工具集成在这家公司的Blast-Rail产品中。这些工具采用了一种可升级的多项式泄漏模型,可获得片上温度变化的精确读数。用户在全芯片级上确认热点,并在工具判定热点后进行深入分析。通过检索发现,有四件相关专利,这些工具都采用了一种升级的多项式泄漏模型,可获得片上温度变化的精确读数。用户在全芯片级上确认热点,并在工具判定热点后进行深入分析。

6结论

EDA中的低功耗设计技术越来越受到重视,通过专利我们发现,几乎所有关于EDA的低功耗专利都是2000年以后的,并日益增加,这主要是因为现在产品的设计周期短,上市时间要求紧迫,因此需要借助EDA工具中的低功耗设计方案来实现功耗的自动优化。由此可见,EDA厂商不仅仅提供的是设计工具,还需要根据客户的设计需求提供问题的解决方案。

根据专利的重要性可将专利分为:核心专利,重要专利、普通专利。所谓核心专利是指在某一领域占有重要地位,他人很难避开的专利保护范围,具有很高的商业价值的专利;所谓重要专利是指在技术或者商业方面具有较高价值的专利。但是从EDA几个占据主导地位的公司申请的低功耗专利来看,还没有发现建立起战略性的专利布局。

通过专利分析可知,不同低功耗技术的EDA支持没有形成体系。因此,有效的低功率设计要求设计团队、IP供应商以及工具和解决方案提供商之间展开协作。只有通过实施连贯一致的方法,并将这些方法运用在供应链赖以存在的整个工具领域,电子行业才能真正解决低功率设计所面临的不断增长的挑战。

作者简介

徐文苑,工业和信息化部软件与集成电路促进中心专利分析师,集成电路设计硕士,研究方向为微处理器设计,主要从事处理器技术领域的专利分析。

武晓岛,工业和信息化部软件与 集成电路促进中心项目经理,计算机应用技术硕士,主要从事高端通用芯片技术领域的专利分析。

谢学军,工业和信息化部软件与集成电路促进中心主任助理,微电子学与固体电子学专业博士,知识产权司法鉴定人。主持“IP评测及规范化技术研究”和“高端通用芯片知识产权分析”等多个国家级项目,重大专项嵌入式CPU知识产权评估组组长,在计算机体系结构、IP核标准、知识产权深度分析和司法鉴定方面有研究。