传输距离对芯片供电影响的研究

2024-10-31高思明

摘 要:芯片工作所需的能量供应,是通过传输路径送达其内部的。在传输过程中,存在电压压降、效率损耗与电压动态响应等情况,其在高功率大电流的芯片供电应用中尤为明显。针对此情况,研究了传输距离对芯片供电的影响,并对研究结果进行了分析。报告了芯片供电的传输距离对功耗、电压、电源设计所带来的影响和困难等现状;提出了通过缩短电源传输距离来实现优化芯片供电质量及提高电源有效使用率的设计方案的调查与仿真,通过对调查和仿真结果进行比照分析,验证了所提策略的有效性与可行性。

关键词:传输距离;电源分配网络;传输损耗;电源仿真

中图分类号:TM910 文献标识码:A 文章编号:2096-4706(2024)17-0009-05

0 引 言

芯片,即集成电路(Integrated Circuit, IC),是一种小型化电子器件或部件的方式,是电子产品中不可或缺的存在。芯片有多种,常见的有中央处理器(Central Processing Unit, CPU)、存储(Memory)、图形处理器(Graphics Processing Unit, GPU)等,以及在计算机领域常用的基板管理控制器(Baseboard Management Controller, BMC)、复杂可编程逻辑器件(Complex Programmable Logic Device, CPLD)等。芯片在云计算、通信、人工智能、工业互联网及汽车与消费电子等各个领域广泛应用[1]。

芯片是在电能驱动下实现运算或逻辑关系处理的,其工作离不开稳定可靠的电源供应。芯片电源的特性包含有电压稳定性、电流的不确定性、电源干扰源以及电能总功率等。电源对芯片的重要性显而易见,芯片正常工作的必要条件之一,就是其电源的高可靠性。随着现代电子技术的快速发展,以及绿色能源体系的逐渐完善,芯片的供电技术也在其越来越受到重视的大环境下,在性能及效率等各个方面取得较快发展。

当前应用中,芯片一般是在印刷电路板[2](Printed Circuit Board, PCB)上进行设计。芯片供电具体实现方式为电源转换部分布局在距离芯片一定距离的外围位置,电源转出芯片所需电压后,通过铜箔分别将电源输出正负极与芯片的电源引脚和地引脚相连,电流通过电源正通过铜箔到达芯片电源引脚,其回路通过芯片地引脚经铜箔返回至电源输出负极。连接电源与芯片的铜箔的长度,即为芯片的供电传输距离。供电传输距离的长短是影响芯片供电质量的一个重要因素,其直接影响着芯片的电压稳定性(电压波动大小)、电源功耗[3]及可靠性等。本研究旨在针对服务器产品中现有的芯片供电设计方法以及在应对供电传输距离所带来的影响的应对策略进行分析,提出一种对芯片供电传输距离进行优化的策略,并通过理论分析与仿真结果对比,对所提策略进行验证,以达成提高芯片供电质量、降低系统电源功耗、提高系统电源稳定性的目的。

1 传输距离的影响

当芯片供电的传输距离在长度上存在差异时,必定也会在电源各个方面产生不同的影响,在服务器产品的芯片电源设计中,较为常见的影响有以下几点。

1.1 芯片供电电压

众所周知,导体是有电阻和电感特性的[4],作为电流传输载体,其自身电阻与电感对电流传输产生阻滞与消耗效应。具体影响形式:电阻效应表现为在导体上产生与电阻和电流成正比的电压降;电感效应表现为对不同变化频率的动态电流,产生与不同效应电压波动。

由于产品设计中,电路实现都是在PCB上进行设计的,PCB中的铜箔的电阻计算:

(1)

其中R为电阻(Ω);ρ为铜箔电阻率(Ω·m);L为铜箔长度(m);S为铜箔截面积(m2)。

电压降的计算:

(2)

从式(1)中可看出,铜箔电阻与供电传输距离成正比,故供电传输距离越长,则其电阻越大。继而结合式(2),因芯片所需电流是由芯片本身决定,可知,电压降的设计影响因素只有电阻,也就是说仅由供电传输距离这一设计因素决定。

PCB中铜箔的电感计算公式:

(3)

其中L为电感,l为走线长度,W为线宽。

由式(3)可得,W越大,l越小,则PCB走线分布电感越小。感量随l大致呈比例变化,但W增加约10倍方才减少约50%的感量。

电流变化时,电感对电压波动的影响为:

(4)

其中UL为电压波动,di/dt为芯片负载变化时,电流的变化率,其单位为A/s(安培每秒)。

通过式(3)和式(4)知,供电距离的长度决定铜箔电感量,从而决定了芯片供电电压的波动量。

据上分析,芯片的供电距离对芯片供电电压方面有较直接的影响。

1.2 系统电能损耗

电流通达芯片之路径,由于电阻与电感的存在,致使电压产生压降与波动。此压降与波动除对电源稳定性的影响,也影响着电能损耗[5]。电能损耗的关联因子主要是电阻,其上产生的损耗功率:

(5)

电能损耗与电阻成正比关系,直观的,即其与传输距离是正比关系。电源损耗是指传输中浪费掉的能量,以热的形式浪费掉,芯片所能利用的电能与电源输出的总电能之比称之为电源使用效率。可知,芯片供电,以电源转换效率高者为佳。随着当前芯片计算量高速提升,其功率也成倍增加,而传输中的损耗与电流的平方成比例关系,导致损耗急剧上升,系统工作所需功率值也更加巨大。除了对电能带来巨大浪费外,对系统的电源配置也是一个巨大的挑战。

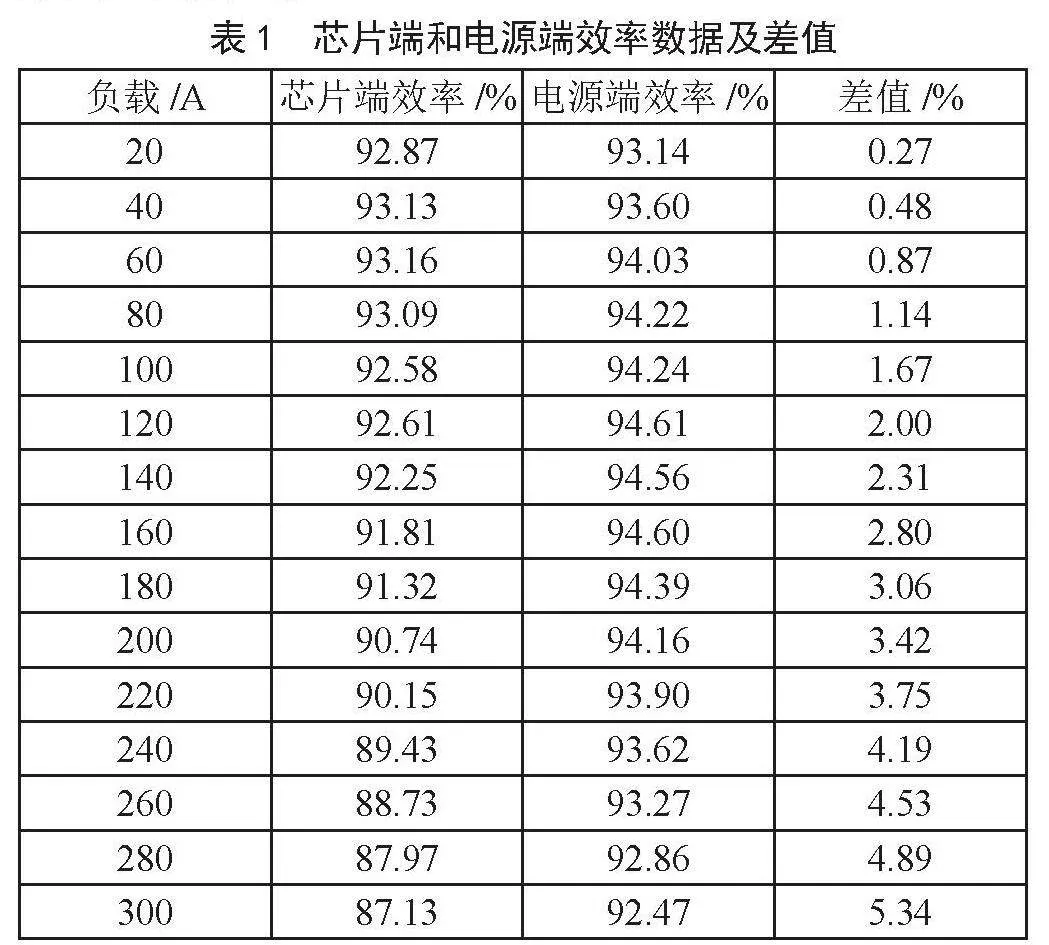

表1为某服务器产品中分别测量得到的芯片端和电源端所得电源转换效率的数据及差值对比,其主要差异在于,芯片端的效率较电源端的效率多出了传输距离上的损耗。

由表1数据可直观的看出,在负载逐渐增加的过程中,损耗的差值也在逐渐增加,且在300 A时达到了最高的5.34%,造成能源的极大浪费。

1.2.1 电源噪声与干扰

电源噪声[6]是电磁设计中必须考虑的因子,噪声除了对电源本身的质量产生极大的负面作用,还极易对其周边的信号带来致命的影响。传输路径中因各种因子造成的电压波动,是为电源噪声的较主要的来源。供电距离与电压波动成正比,则其电源噪声也是同向关系,同样的供电情况下,传输距离较长的设计方案,其产品所带有的电源噪声危害也会更大。

1.2.2 电源分配网络

电源分配网络[7](Power Delivery Network, PDN)主要有三个作用,一是为负载提供干净稳定的供电环境;二是为高速信号提供低阻抗、低噪声的工作条件;三是避免电磁干扰(Electromagnetic Interference, EMI)辐射。不同的电感与电阻特性导致电源在恒流传输中表现出电压压降及非恒流传输时表现出电压波动问题,这对芯片的正常工作是有害的。

2 传输距离影响的常规应对策略及缺点

总结供电距离带来的影响的几点因素,归根结底是其传输路径上的寄生电阻、寄生电感等导体的固有特性,对电源的传输产生了设计预期之外的表现,使得设计质量不达预期。针对第1部分内容中所提出的几点影响,业内较为常规的应对策略有以下措施。

电压压降与波动的应对方案有两种常用方法。第一是增加印刷电路板(Printed Circuit Board, PCB)上电源传输铜箔的宽度与厚度。其实质就是通拓宽电源通流面积,从而起到减小路径上的寄生电阻抗与寄生电感的目的。此举是十分有效也是最常用的一种解决方案,但缺点也极为明显,需要占用更多的设计空间,会影响到产品的设计可行性,同时也会增加设计成本。第二个实用方法,则为增置滤波电容器。电容器的特性,可以抵消电源路径上寄生电感的影响,从而有效的抑制电源波动。电容器的放置需要额外的PCB面积,同时带来物料的增加和成本上升。

传输电能损耗的影响是不可避免的,目前基本没有较为有效的解决方法可以将芯片损耗有效的控制在一定范围内。传输路径上的电能损耗,主要的影响因子是寄生电阻,降低导体电阻的方法,一是设计中使用低电阻率的材料,采用高导电[8]率的铜箔,其寄生电阻必然小,此举可降低传输损耗。二是拓宽截面积,如增宽或者增厚铜箔,将寄生电阻的值降下来,从而降低损耗。然而这些做法均只能在一定程度上起到作用,无法解决传输距离的影响,与之而来的是成本较大上升,此种方式性价比不高。随着芯片功耗越来越高,电流越来越大,而随着芯片运算量的增加,传输损耗也同步呈现增加趋势。

电源噪声及其带来的干扰,会严重影响PCB信号布局。当前采用多种方法避免电源噪声,如选用调节能力更强的电源、选用抗干扰元件,等等,但因为实施难度较大,并非常规适用方法。硬件设计时,常规噪声处理方法一是保持高隔离空间,二是地线处理与屏蔽。高隔离空间即在信号与电源平面间保持一定距离,使信号在电源噪声的干扰能量空间之外,保障信号的质量不受影响。地线处理是指在信号走线附近增加地孔,或者增加地走线并打孔的方式,将电源噪声通过地隔离,并通过地将其导入大地,起到保护信号的目的;屏蔽则是将信号用大地包围,使其完全独立走线,从而规避电磁噪声。以上三种方式,均可起到一定降噪场效果,但也意味着需要更多的避让空间,需要更大的PCB面积来达成设计目标,对设计可行性带来巨大挑战。

当前针对PDN的优化方案主要是根据芯片本身的特性制定符合其稳定工作的PDN曲线,通过在芯片供电系统中使用不同频率(高频、中频、低频)和电容值的电容来起到优化PDN的作用。通过对不同容值与不同工作频率点的电容进行合理分配使用的方法,可将PDN控制在一定范围。其主要缺点是需要数量较多的不同规格的电容器,带来的问题,一是需要足够的设计空间摆放电容,二是电容器的成本压力较大。

3 芯片供电距离优化策略及分析

3.1 优化策略理论分析

针对前文所述理论及问题点,提出了一种针对芯片供电距离的优化策略,通过该策略进行理论分析与电源仿真[9],来阐明其可实现性。

结合所述长传输距离带来的影响及其导致的不良结果,以及常规应对策略的被动性,提出可极大缩短芯片供电传输距离的一种设计策略,该策略基于当前芯片设计,通过将当前的水平方向供电模式,设计成为在芯片底部设计供电电源的竖直方向供电方式。为方便说明,定义芯片所在位置为PCB正面,与之对应的另一侧称之为PCB背面。实现方式为,首先,将设计在PCB正面的芯片所需电源布局移除,其传输路径一并移除;继而将电源改置于PCB背面,其位置大概与芯片相当,重点是将电源输出点布局于芯片用电管脚所对应位置;最后,将电源输出布于PCB背面,再通过铜箔与通孔将其与正面芯片的电源管脚通连。基于此策略的设计,需要将PCB背面到机箱的距离扩大至容许电源零件布局。

经上,电源由芯片同侧布局,水平传输至芯片的供电方式设计为在芯片背侧布局而且沿竖直方向传输的方式。

所提策略主要论点在于,物理上极大缩短了电源传输距离的长度。先是将电源水平方向传输距离缩短至接近于零,继而确定竖直方向上电源的传输距离仅约为PCB的厚度,一般在1.6~3 mm以内。

竖直方向供电的实际意义表现在,在物理布局上极为有效地解决了芯片供电传输距离上导体的寄生电阻与寄生电感的客观存在与不可规避性,通过电源设计的优化,理论上极大消除了传输过程中所产生的电压电降、电压波动、传输损耗、电源噪声与PDN设计中的难点瓶颈。

3.2 仿真分析

在PCB中分别进行两种布局,一为电源与芯片放置与PCB的正面侧,电源输出电感到芯片的距离约为2 720 mil,之间通过宽度为1 313 mil的铜箔相连,以远距离传输代称;第二种为电源放置于芯片所处位置的PCB背面位置,电源在PCB背面通过铜箔与过孔与芯片电源管脚相连,以近距离传输代称。两种方案的差异约为2 720 mil的供电距离。

通过直流仿真(IR-Drop压降与传输损耗),交流阻抗等效仿真(电感,Inductance)与PDN仿真的结果对比,分别从3个维度对两种供电方式表现的差异化进行剖析,得出其优势与劣势,以下分析仿真结果。

3.2.1 直流仿真

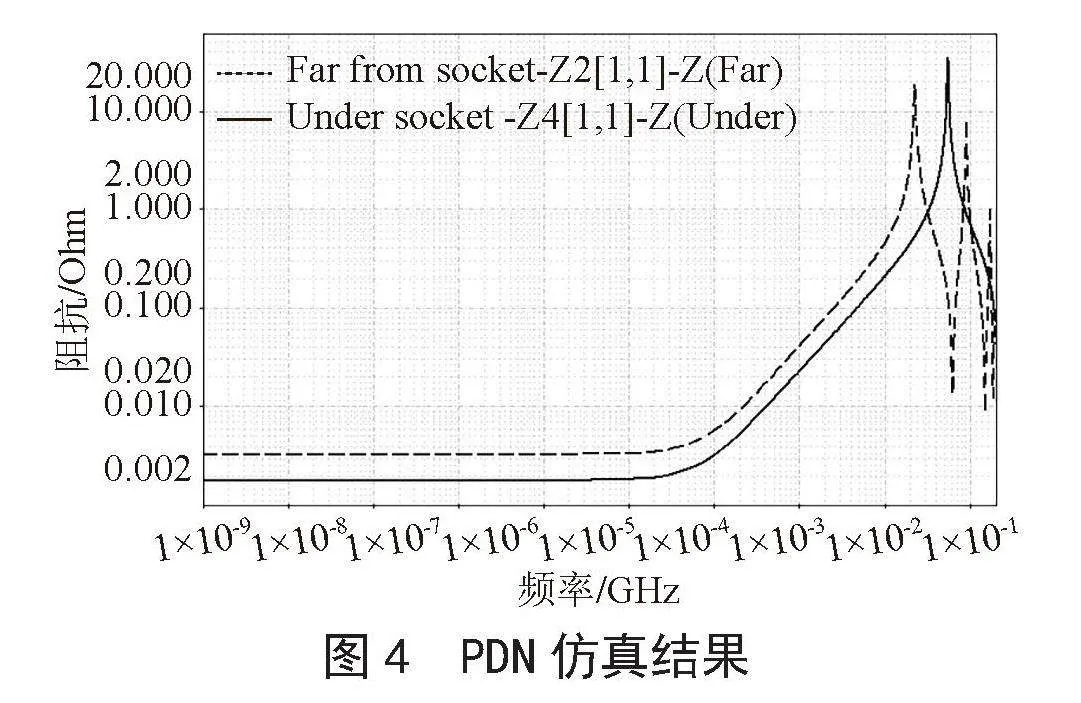

图1和图2为两种策略的IR DROP仿真结果,图中上部分信息为电源到芯片的供电信息,输出电压为0.8 V,仿真电流为20 A。

通过仿真结果可以直观的看出,远距离传输的情况下,电源路径压降37.5 mV,地平面压降4.2 mV,总压降41.7 mV,总压降占比到了标准输出电压(0.8 V)

的5.2%;损耗为738.4 mW,占到电源总输出功率

(20 A×0.8 V=16 W)的4.615%。近距离传输时,电源路径压降降至7.0 mV,地平面压降1.8 mV,总压降降至8.8 mV,总压降占比仅为标准输出电压(0.8 V)的1.1%;损耗降至127.5 mW,仅占电源总输出功率(20 A×0.8 V=16 W)的0.797%。可见,所提策略有效改善了电源传输中电压降和损耗的问题。

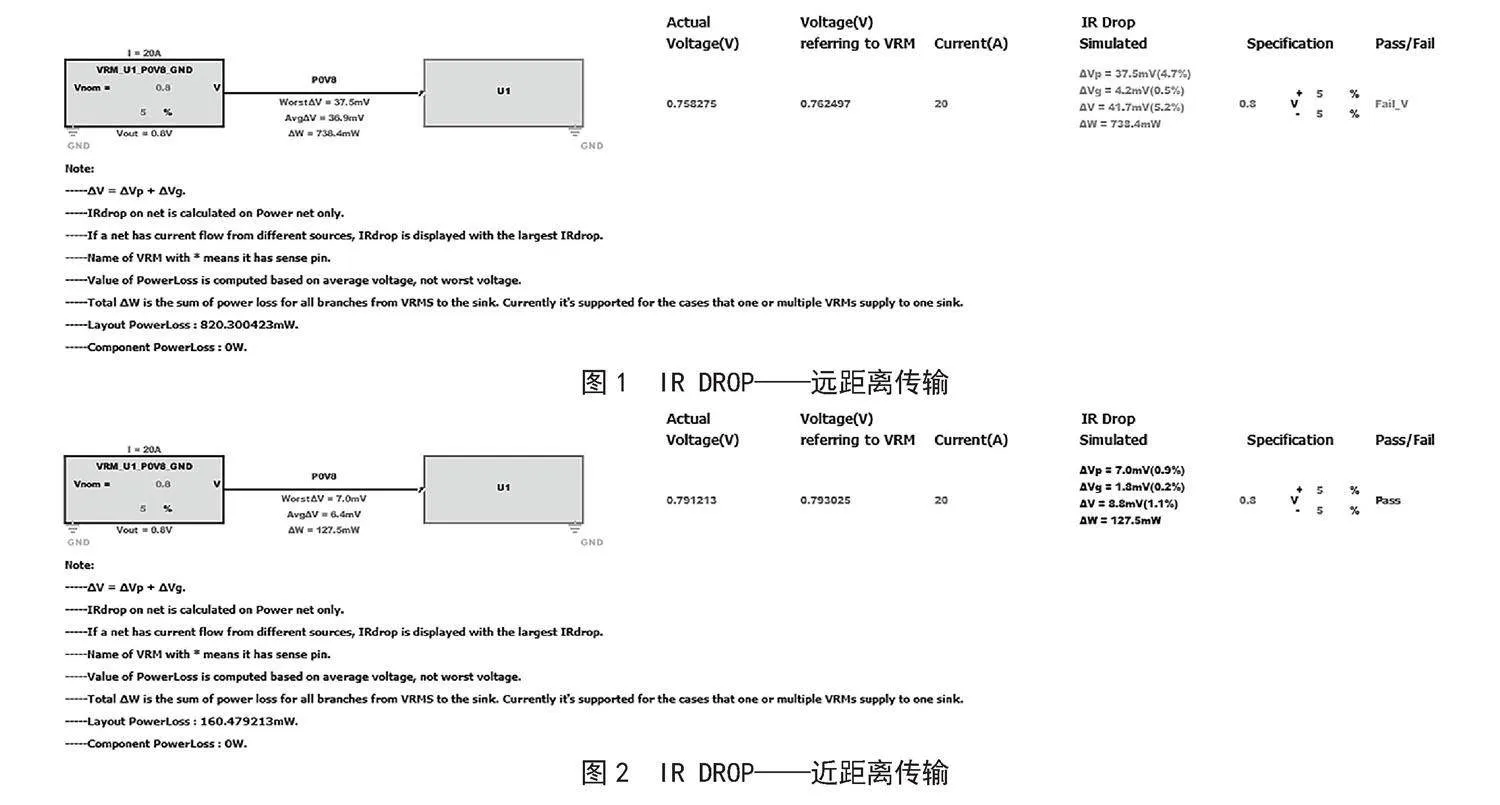

3.2.2 交流阻抗等效仿真

如图3所示,为两种策略的交流阻抗等效仿真对比,其中实线与虚线分别代表近距离传输和远距离传输。由图中曲线可知,直到0.3 GHz的频率前,近距离传输路径的电感约为0.44×10-9 nH,而远传输距离路径上的电感约为0.75×10-9 nH。在将电源使用近距离传输策略后,等效电感降低至原来的58.67%。优化策略明显改善了电感特性。

3.2.3 PDN仿真

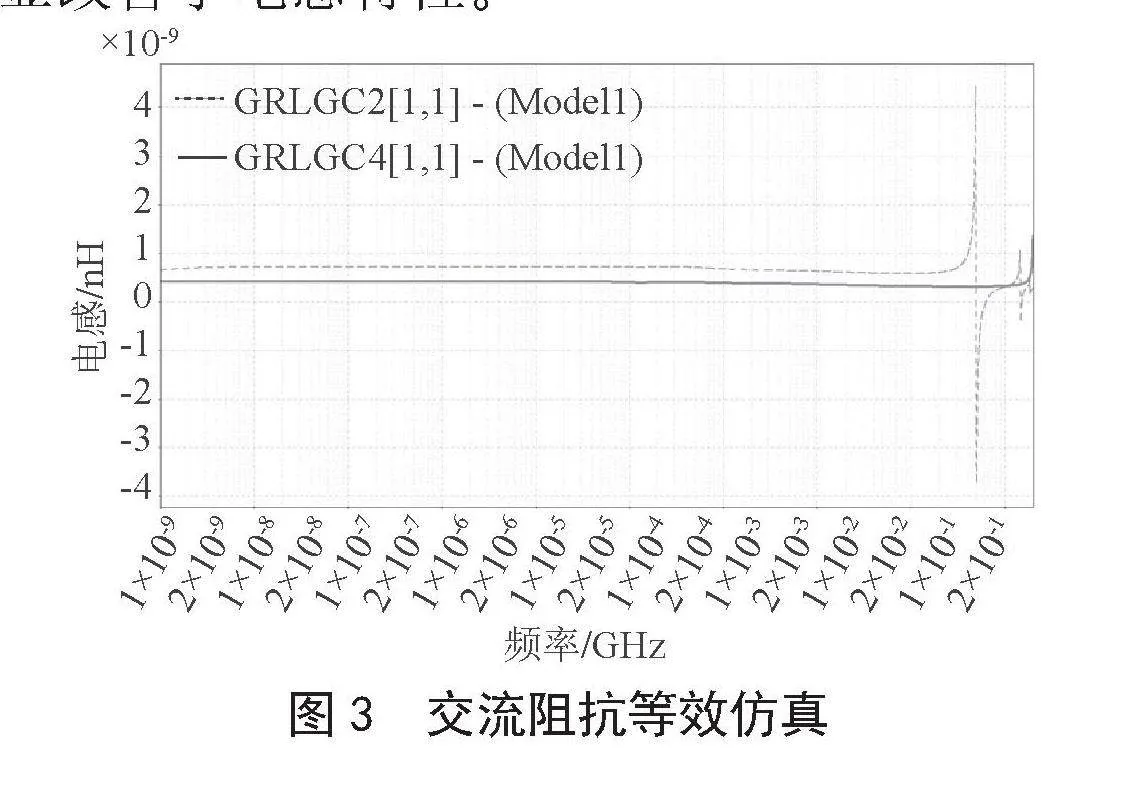

图4为所提策略与原方案的PDN仿真结果。其中实线与虚线分别为近距离传输和远距离传输的PDN结果图示。

在中低频段,远距离传输时阻抗约为0.003 3 Ω,近距离传输则可降低至约0.001 8 Ω,近距离传输与远距离传输策略相比,PDN阻抗有明显降低且降幅明显[10]。

4 结 论

基于电源传输距离的特性分析,从电源压降、电源波动、传输损耗、电源噪声干扰与电源分配网络几个方面对电源传输进行分析,总结其缺点与局限性,再针对优化方向及策略进行理论分析并仿真。结合理论分析与仿真结果来看,可得出所提针对电源传输距离的优化策略及方向是积极可行的,具有较强的实际设计指导意义,有利于服务器及各行业芯片电源的设计及优化方向选择。

电源传输距离在服务器、物联网及电动汽车等各领域都用广泛应用,新型传输技术的研发将成为研究重点,未来对PCB电源传输的研究必向更高效,更安全的方向前行。

参考文献:

[1] 吴锦才.寻找芯片应用新的牵引力 [N].中国证券报,2018-01-19.

[2] 牛森,张敏娟,银子燕.高速PCB多板互联的电源完整性分析 [J].单片机与嵌入式系统应用,2023,23(9):41-44.

[3] 张文明.一种宽输入低功耗开关电源设计 [D].成都:电子科技大学,2022.

[4] 廖清芬,王雷雄,吴军,等.电工类课程中电阻、电感及电容相关概念辨析 [J].中国电力教育,2020(11):78-79.

[5] 陈明浩,陈乾宏,任小永,等.开放式电源模块损耗及散热的分析与优化 [J].南京航空航天大学学报,2014,46(4):544-551.

[6] 刘喜,孟永哲,王岩,等.开关电源输出纹波噪声分析与控制 [C]//2022年中国家用电器技术大会论文集.宁波:[出版者不详],2023:6.

[7] 顾晓雪,顾定富.电源完整性分析及应用 [J].电子与封装,2017,17(2):21-24.

[8] 吉文.连接器用的高导电率新型合金铜 [J].机电元件,1991(4):21.

[9] 孟祥胜,车凯,栗晓锋,等.高速PCB电路电源完整性仿真分析 [J].电子技术应用,2019,45(9):50-52+59.

[10] 王建,李涛,刘瑞.处理器供电电源的设计 [J].微型机与应用,2017,36(10):33-36+39.

DOI:10.1286d6f24ec6bcee2a222190da8c017d22d19924e1781e994f9c5b3771c7adfbb9850/j.cnki.2096-4706.2024.17.003

作者简介:高思明(1984.11—),男,汉族,山东德州人,主任工程师,本科,研究方向:计算机直流电源。

收稿日期:2024-03-15

Research on the Impact of Transmission Distance on Chip Power Supply

GAO Siming

(Inspur Electronic Information Industry Co., Ltd., Ji'nan 250101, China)

Abstract: The energy supply required for the operation of a chip is delivered to its interior through a transmission path. In the transmission process, there are voltage drop, efficiency loss, and voltage dynamic response and other situations, especially in chip power supply application of high power and high current. In response to this situation, this paper studies the impact of transmission distance on chip power supply, and analyzes the research results. It reports the influence and difficulty of the transmission distance of chip power supply on power consumption, voltage and power supply design, and carries out the investigation and simulation of the design scheme of optimizing the quality of the chip power supply and improving the effective utilization rate of the power supply by shortening the transmission distance of the power supply. The effectiveness and feasibility of the proposed strategy are verified by comparing and analyzing the investigation and simulation results.

Keywords: transmission distance; power distribution network; transmission loss; power simulation