一种高精度、快速瞬态响应的无片外电容低压差稳压器

2024-09-30白创李凯

摘 要:该文基于0.18 ?滋m工艺设计一种无片外电容低压差稳压器(LDO),设计带推挽输出级的高摆率误差放大器提高输出电压精度和瞬态性能。此外,设计自适应偏置电路取样输出电流从而动态改变偏置电流,进一步提升LDO的瞬态性能。仿真结果表明,LDO压差为120 mV,在3.3~5.5 V的输入范围内输出电压为3 V,负载电流范围为0~20 mA。在不同负载电流下LDO相位裕度均达到60°以上,环路增益大于100 dB。LDO线性调整率为100.68 ?滋V/V,负载调整率为11.21 ?滋V/mA。负载电流在1 ?滋s内于100 ?滋A~20 mA间跳变时,过冲及建立时间分别为129 mV和1.4 μs,下冲及建立时间为109 mV和1.02 μs,满足高精度和快速瞬态响应的需求。

关键词:低压差稳压器;无片外电容;自适应偏置;高摆率;快速瞬态响应

中图分类号:TN432 文献标志码:A 文章编号:2095-2945(2024)28-0039-04

Abstract: In this paper, a output-Capless low-dropout regulator (LDO) is designed based on 0.18 μm BCD process. The error amplifier with push-pull output stage improves the output Voltage accuracy and the transient performance. Additionally, an adaptive bias circuit is designed to sample the output current and change the bias current to improve the transient response of the LDO. The simulation results show that the dropout voltage of LDO is 120 mV. The input range is 3.3~5.5 V, and the output voltage is 3 V. The load current range is 0~20 mA. LDO phase margin and loop gain are more than 60° and 100 dB, respectively, under different load currents. The line regulation and load regulation are 100.68 μV/V and 11.21 μV/mA. When the load current skips between 100 μA and 20 mA within 1 μs, The overshoot and settling time are 129 mV and 1.4 μs, respectively, the undershoot and settling time are 109 mV and 1.02 μs. The performance can meet the requirements of high accuracy and fast transient response.

Keywords: low-dropout regulator; output-Capless; adaptive biasing; high slew-rate; fast transient response

随着便携式电子的普及,LDO因其结构简单、规模小和低噪声等优势被广泛应用[1]。传统的LDO通常需要在片外接入大电容以抑制输出电压尖峰和提高环路稳定性[2-4]。然而,带片外电容LDO需要占用更大的PCB面积和额外引脚,不利于SoC设计。为解决此问题,无片外电容LDO的研究受到广泛关注[5-9]。

目前,无片外电容LDO的设计难点主要为稳定性、输出电压精度和瞬态响应等指标之间的折衷。为解决上述问题,往往需要同时从高环路增益、高摆率和大带宽的角度考虑。目前,有多种方法在高环路增益情况下,提高LDO瞬态响应[10-13]。文献[10]通过动态自偏置技术动态调整偏置电流加快了瞬态响应,但其在轻载下LDO变为两级结构,降低了环路增益,使得输出电压精度受负载影响较大。文献[11]通过加入尖峰电压检测模块,通过感应过冲和下冲发生,加快对功率管栅极充放电,进而改善了瞬态响应,但该结构采用的高通网络需要消耗额外的芯片面积。文献[12]中采用推挽放大器提高了瞬态性能,并通过零极点追踪技术引入动态零点对输出极点进行追踪补偿提升环路稳定性,但动态零点往往难以完全跟随输出极点变化,因此相位裕度随负载变化较大。文献[13]中通过瞬态增强型超级源随器(SSF)拓展带宽的同时加大摆率,以提高瞬态性能。但同样需要消耗更多的电容面积。除上述技术之外,直接利用MOS管本身跨导调制效应的NMOS LDO也能很大程度上优化瞬态响应[14],但往往需要加入升压电荷泵以确保能够实现低压差。

本文从提高系统环路增益和改善功率管栅极摆率的角度入手,实现了高精度和快速瞬态响应。通过带推挽输出级的两级误差放大器,同时提高了环路增益和摆率;为进一步提高瞬态响应,通过自适应偏置技术动态改变放大器偏置电流大小,减小过冲、下冲幅度和建立时间。此外,为确保环路稳定,通过前馈通路引入零点进行补偿,实现了较好的环路稳定性。

1 LDO电路分析

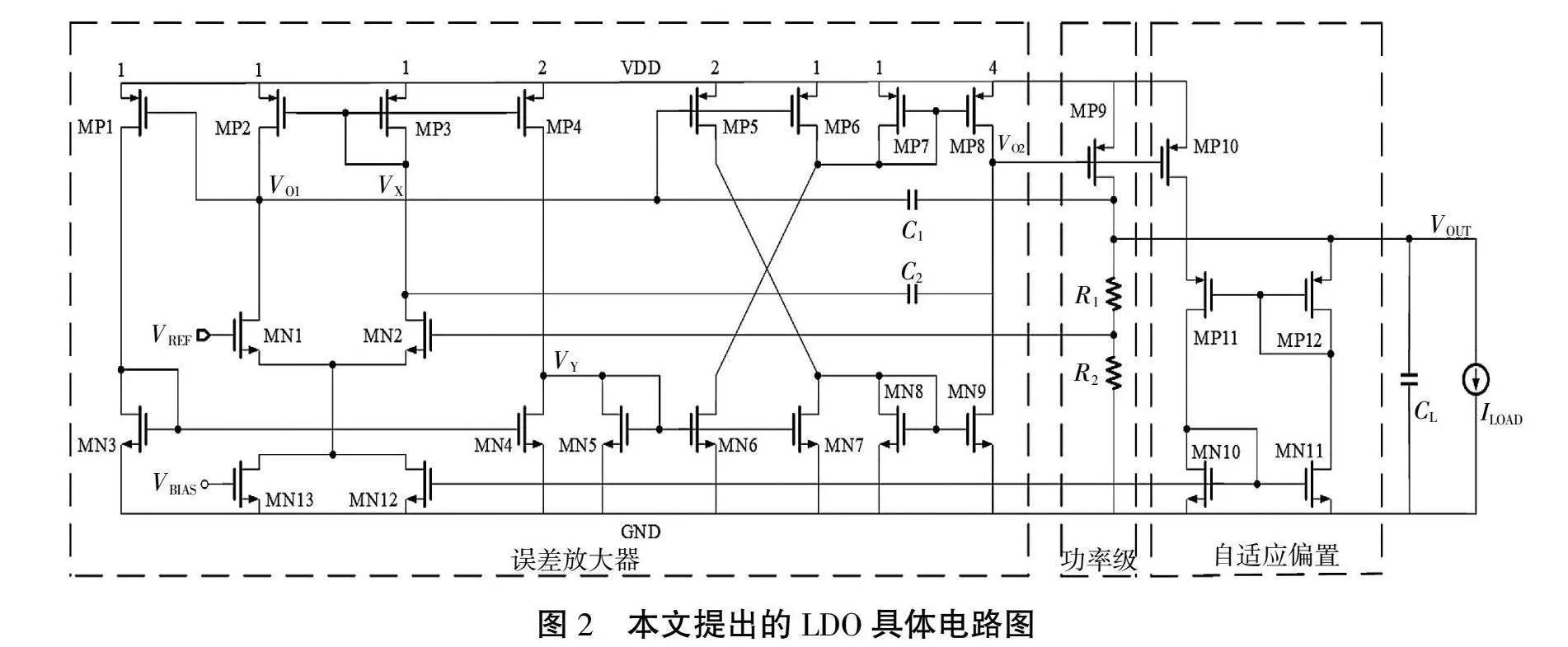

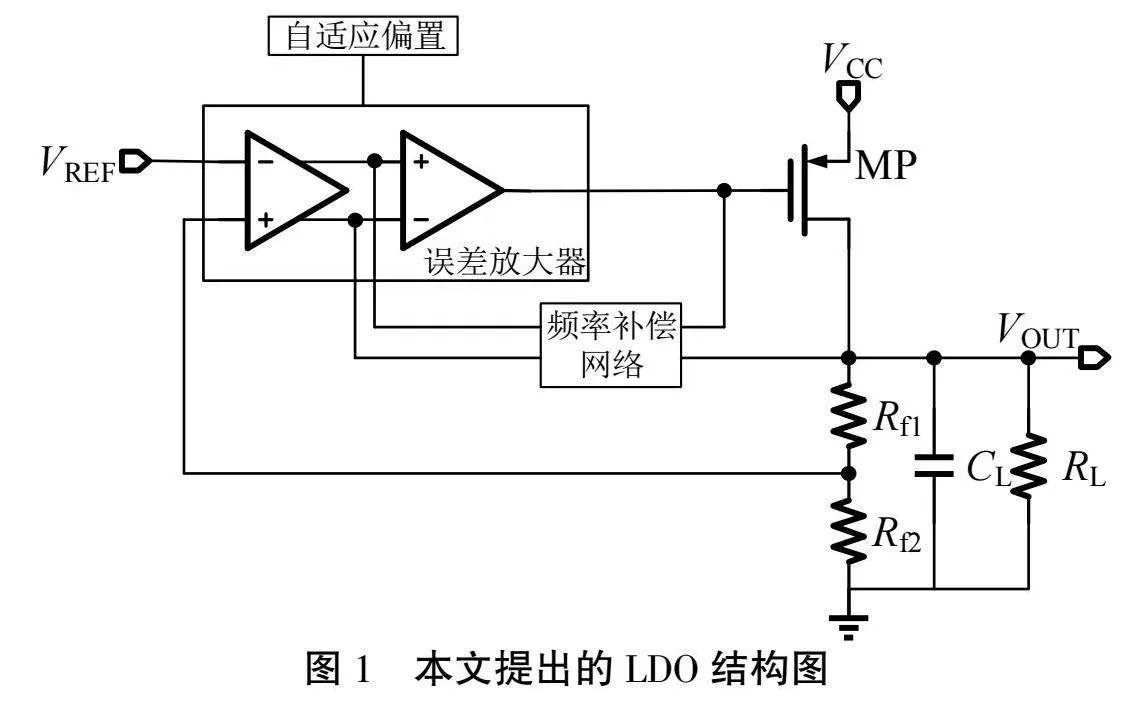

本文提出的LDO整体框图如图1所示。其中,功率管MP的尺寸较大,为提高其栅极摆率,设计误差放大器第二级为推挽结构。增加了自适应偏置模块动态改变误差放大器偏置电流,提高了环路带宽,从而加快瞬态响应。LDO为两级放大器+功率级的三级放大结构,较高的环路增益确保了输出电压VOUT的精度,降低了线性调整率和负载调整率。CL为负载电路的等效寄生电容,本文中取10 pF。下面分别对LDO的误差放大器和自适应偏置电路进行分析说明,LDO的具体电路如图2所示。

1.1 误差放大器

MP2—MP3、MN1—MN2、MN12—MN13构成NMOS管输入的差分放大器为本文误差放大器的第一级,用于提供高增益,VO1为第一级输出节点。MN13为1 A的恒定偏置,MN12为动态偏置,用于改善带宽,两者共同构成误差放大器的尾电流源。

MN3—MN9、MP1和MP4—MP8管为误差放大器的第二级,VO2为第二级输出节点。第二级为同相缓冲器,忽略MP4的前馈路径,其增益A约为gmp1gmn4/gmn3gmn5,其中gmp1、gmn3、gmn4和gmn5分别为MP1和MN3—MN5管的跨导。因此VY≈AVO1。当VO1增大(减小)时,VY同时增大(减小),致使ID,MP8增大(减小)而ID,MN9减小(增大),两者相互叠加构成了推挽输出。第二级中的MN6—MN9、MP5—MP8管为电流镜像技术构成的跨导提升电路,其镜像比例如图2所示。

1.2 自适应偏置电路

为提高LDO的瞬态性能,本文通过自适应偏置电路动态改变LDO偏置电流,从而提高带宽和摆率,加快瞬态响应。其具体电路结构如图2中MP10—MP12和MN10—MN12所示。MP9为功率管,MP10为采样管。为减小功率管寄生电容和面积,MP9和MP10均采用工艺最小沟道长度设计,因此沟道长度调制效应明显。为减小沟道长度调制效应带来的误差,通过MP11—MP12和MN10—MN11构成钳位环路,从而提高电流复制精度。

该电路具体工作原理如下。MN10—MN11和 MP10—MP11为电流镜结构,取较大的栅长以提高复制精度。通过MN10和MN11的作用,使得ID,MP11=ID,MP12。忽略MP11和MP12的沟道长度调制效应,可得VS,MP11≈VS,MP12,进而确保采样管的VDS,MP9=VDS,MP10,使得电流按比例精确复制。

在瞬态响应过程中,当负载电流ILOAD突然减小,输出电压VOUT产生过冲,由于节点电容的存在,动态偏置模块镜像电流减小需要时间,因此该过程下误差放大器偏置电流较大,对过冲有着较强的抑制效果;而当负载电流ILOAD突然增大时,VOUT产生下冲尖峰,偏置电流IDS,MN12相应增大,从而增强功率管栅极摆率。由于环路延时存在,抑制下冲幅度的效果相对较低,但大的偏置电流带来的高带宽特性仍可以显著减小下冲建立时间。

2 LDO仿真结果

本文LDO采用CSMC 180 nm BCD工艺进行仿真。输入电源电压范围为3.3~5.5 V,典型输入电压为5 V,负载电流范围为0~20 mA,输出电压稳定3 V。

2.1 LDO的直流特性仿真

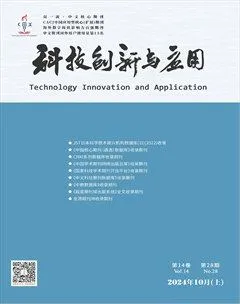

LDO在满负载20 mA下,在2~5.5 V范围内扫描输入电源电压,可测得当输入电源电压大于3.12 V后,LDO输出电压稳定值为2.999 V,即最小压差为120 mV,如图3所示。

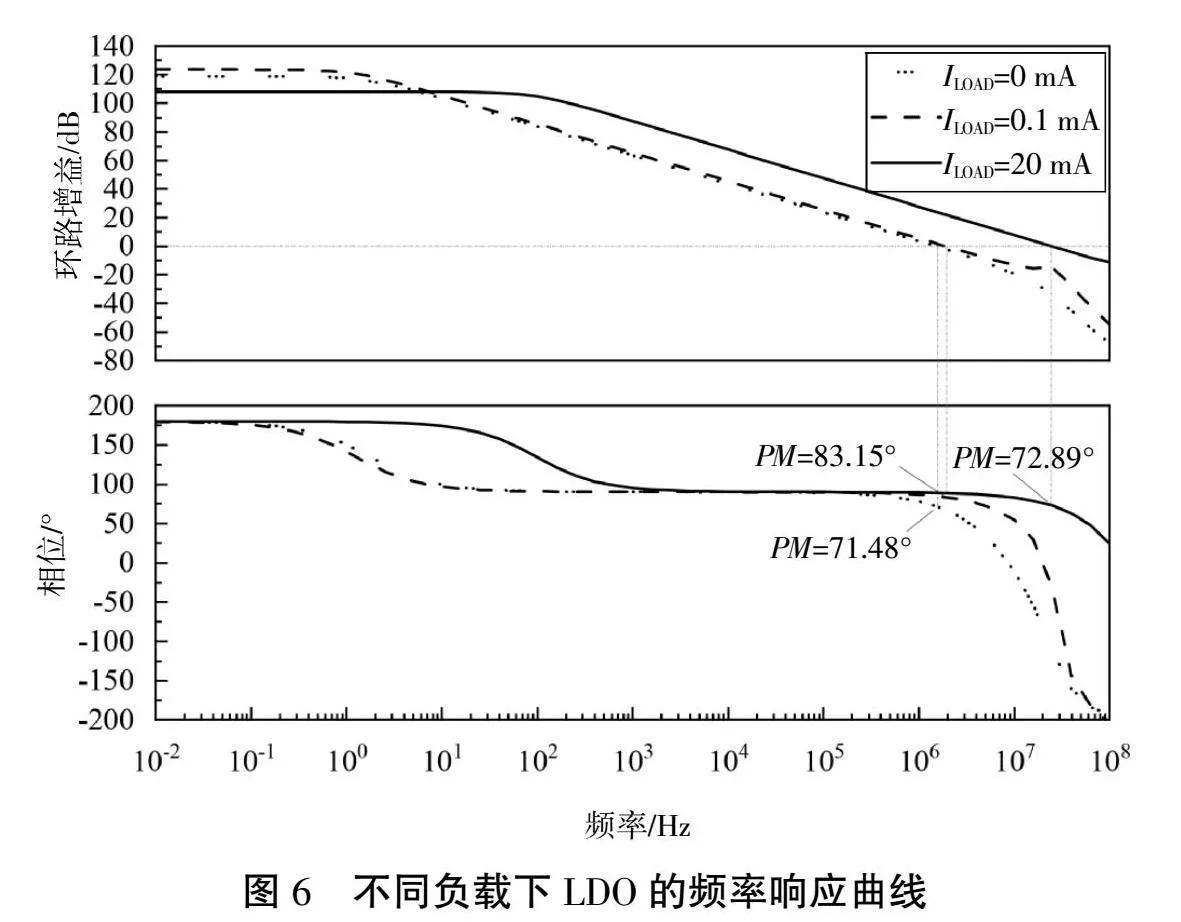

图4为输入电压为3.3~5.5 V时,不同负载电流下线性调整率的仿真结果。根据图像可知LDO的线性调整率在重载20 mA下最差,为100.68 ?滋V/V。

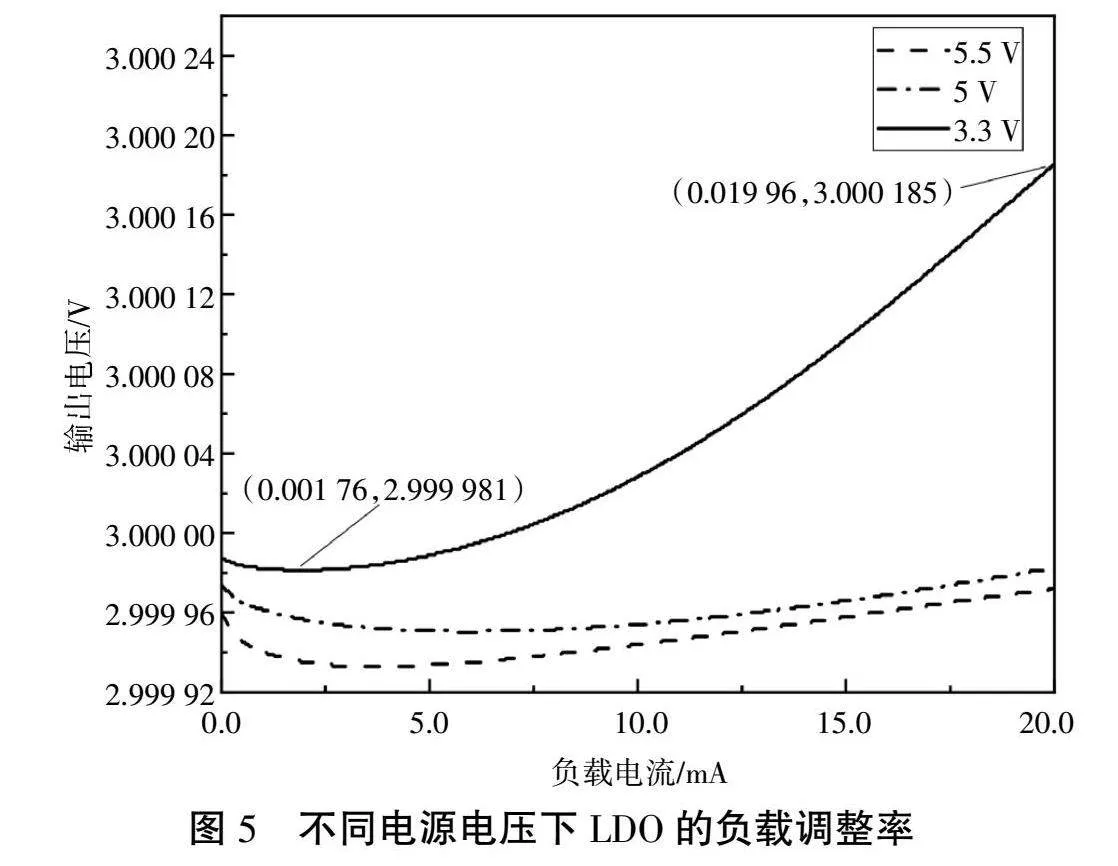

图5为负载电流为0~20 mA时,不同电源电压下负载调整率的仿真结果。LDO的负载调整率在输入电源电压3.3 V下最差,为11.21 μV/mA。

2.2 LDO的稳定性仿真

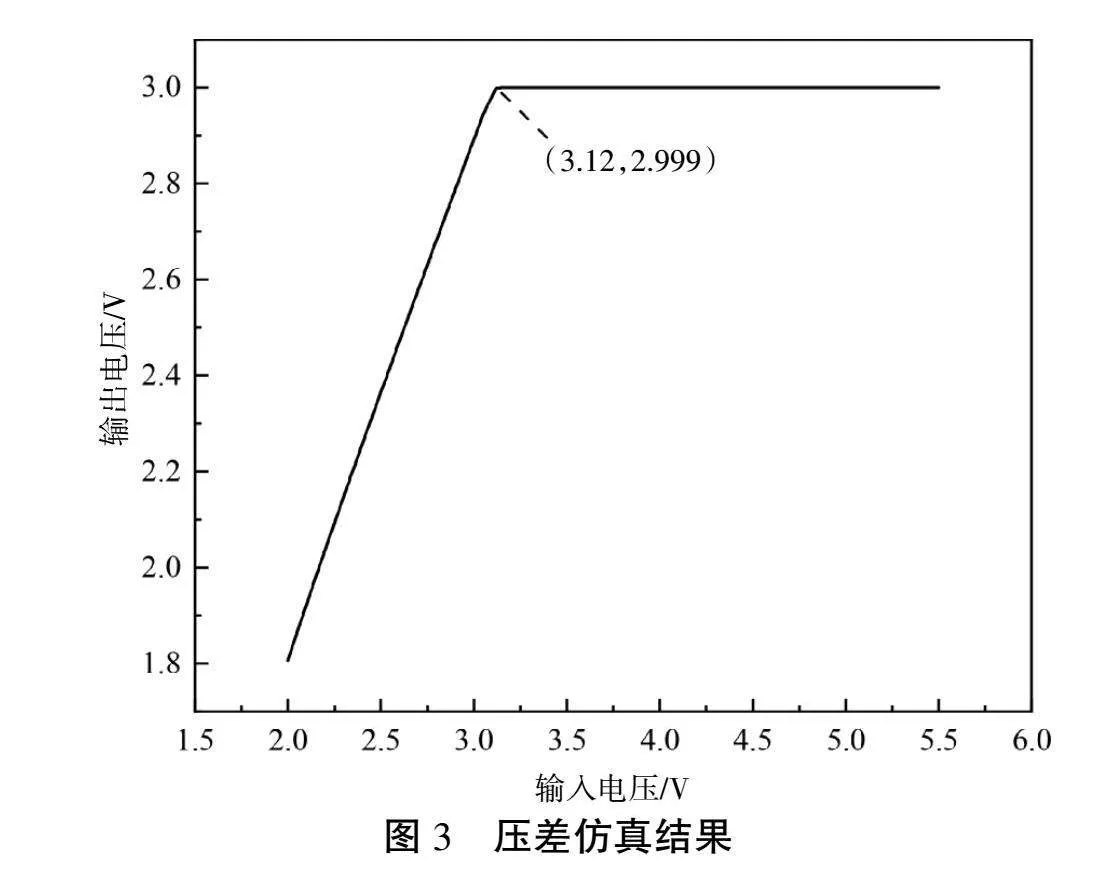

由前文分析可知,LDO的稳定性受负载影响较大,因此需要LDO在空载、轻载和重载下分别进行稳定性仿真,其频率响应曲线如图6所示。

从仿真结果可知:LDO在空载下相位裕度最低,为71.48°;在轻负载下LDO的相位裕度最高,为83.15°。结果表明此外,自适应偏置电路对环路带宽优化明显。该无片外电容LDO高的稳定性,且不同负载情况下系统的环路增益均大于100 dB。

2.3 LDO的负载瞬态响应仿真

图7所示为加入自适应偏置前后,负载电流在1 μs时间内在100 μA~20 mA之间跃变时LDO的负载瞬态响应曲线。加入自适应偏置电路后,LDO过冲及恢复时间分别为129 mV和1.4 μs,而下冲及恢复时间为109 mV和1.02 μs。通过仿真结果对比可知,自适应偏置电路分别削减了233 mV的过冲幅度和59 mV的下冲幅度,且对下冲建立时间优化明显。

3 结论

本文基于0.18 μm BCD工艺设计了一种高精度快速瞬态响应的无片外电容LDO。在精度方面,通过多级放大将环路增益提高至100 dB以上,使LDO的线性调整率和负载调整率得以改善,实现了高精度输出;在瞬态响应方面,通过引入自适应偏置电路优化瞬态响应,将过冲及恢复时间分别减小至129 mV和1.4 μs,下冲及恢复时间减小至109 mV和1.02 μs。仿真结果表明该LDO各项指标满足高精度和快速瞬态响应的需求。

参考文献:

[1] BAI R, GUO Z, YANG J, et al. A Fast Transient Low-Dropout Regulator with High-Power Supply Rejection[J]. Journal of Physics: Conference Series, 2022,2370(1): 12-18.

[2] KAO S K, CHEN J J, LIAO C H. A multipath output-capacitor-less LDO regulator[J].IEEE Access, 2022,10: 27185-27196.

[3] MING X, KUANG J J, GONG X, et al. A fast-transient capacitorless LDO with dual paths active-frequency compensation scheme[J].IEEE Transactions on Power Electronics, 2022,37(9):10332-10347.

[4] 沈洁,王倩,陈后鹏,等.一种瞬态增强的无片外电容LDO设计[J].微电子学,2022,52(3):383-387.

[5] 周玉成,廖德阳,马磊,等.一种具有瞬态增强的无片外电容型LDO[J].微电子学,2023(4):608-613.

[6] LIU N, XIE Y L, GUO J P. A fast transient FVF-based output capacitorless LDO with self- feedback biasing[J]. Microelectronics Journal,2023(134):105724.

[7] 张涛,吴小奔,刘劲.快速瞬态响应低噪声无片外电容LDO[J].电子元件与材料,2023,42(9):1143-1149.

[8] 姚方舟,张章.采用AB类源跟随器的无片外电容快速瞬态响应LDO[J].合肥工业大学学报(自然科学版),2022,45(4):475-480.

[9] 曾范洋,蒋品群,宋树祥,等.一种应用于SoC的高稳定性无片外电容LDO稳压器[J].电子元件与材料,2022,41(3):278-283.

[10] 王梓淇,黄少卿,肖培磊,等.一种动态自偏置的低功耗无片外电容LDO[J].现代电子技术,2023,46(11):175-180.

[11] JIANG Y, WANG L, WANG S, et al. A low-power, fast-transient output-capacitorless LDO with transient enhancement unit and current booster[J].Electronics, 2022,11(5):701.

[12] 杨聚鑫,王佳,郑然,等.应用于前端读出电路的片上LDO设计[J].微电子学,2023,53(2):233-240.

[13] ZHAO X, ZHANG Q, XIN Y, et al. A high-efficiency fast-transient LDO with low-impedance transient-current enhanced buffer[J].IEEE Transactions on Power Electronics, 2022,37(8):8976-8987.

[14] 咸会勇.LDO瞬态提升技术研究与芯片设计[D].南京:东南大学,2022.