基于PCIe的智能处理系统研究

2024-04-14胡益诚王树争李碧涵

胡益诚 王树争 李碧涵

摘要:随着航空领域人工智能技术研究的不断深入,面向开放式机载智能交互场景,人工智能的应用可解决诸多问题。同时,基于飞行决策的及时性、实时性要求,大带宽、高性能和高效率特性成为智能处理模块的高速数据传输总线的基本要求。鉴于此,提出了一种基于PCIe接口的智能处理系统,该系统基于CPU+FPGA的异构融合结构设计,通用处理节点基于高性能多核CPU设计,提供两个通用处理节点和两个智能处理节点,并通过对外通信接口实现外部交互。现对该智能处理系统的整体架构进行详细描述,介绍了系统中PCIe总线的工作模式及其内部信号的数据流,并从硬件角度阐述了系统核心电路的设计思路,重点分析了PCIe总线的使用及其优越性。该架构适用于高性能和高效率的智能处理系统,已成功应用于某机载智能处理模块,对相关领域应用具有一定的参考价值和借鉴意义。

关键词:智能处理;PCIe;高性能多核CPU

中图分类号:TN709 文献标志码:A 文章编号:1671-0797(2024)07-0030-03

DOI:10.19514/j.cnki.cn32-1628/tm.2024.07.008

0 引言

人工智能是集合众多方向的综合性学科,在诸多应用领域均取得了显著成果[1]。随着航空领域人工智能技术研究的不断深入,面向开放式机载智能交互场景,人工智能的应用可解决诸多问题。例如智能感知、辅助决策等,可利用人工智能算法对多源传感器捕获的海量信息进行快速处理,仅将处理后的感知结果反馈给飞行员,从而降低飞行员的任务负荷;利用人工智能算法开展航路规划、应激决策等多种智能辅助任务,帮助飞行员做出最优决策。基于飞行决策的及时性、实时性要求,大带宽、高性能和高效率特性已经成为智能处理模块的高速数据传输总线的基本要求。

PCIe是第三代高性能串行互联高速总线,它具有传输速度快、节点独享带宽、可灵活扩展等诸多优点[2],同时支持PCIe协议交换芯片多端口的特性使其在数据传输上打破了以往单一的传输方式,将多个具有PCIe接口的设备相互连接,即实现网状的拓扑结构,使得各挂载的设备可以自由通信[3]。

本文介绍了一种智能处理系统及其硬件设计,该设计以PCIe为主要通信总线,连接处理板卡、智能板卡、FC板卡,PCIe交换芯片作为通信的桥梁,能够可靠地执行各主从设备间数据互通工作,稳定高效地完成信息收发、通用处理、智能运算等工作,已在航空领域得到了验证及应用。

1 PCIe总线介绍

PCIe总线是目前主流的高速数据传输总线,采用由Intel于1997年提出的第3代I/O互联标准,是一种已得到广泛应用的成熟总线技术[4]。

PCIe由分层的体系结构组成,由下至上依次为物理层(Physical Layer,PHY)、数据链路层(Data Link Layer,DL)、事务层(Transaction Layer,TL)。PCIe总线通过数据包传送的形式实现数据收发。TLP(Transaction Layer Packet)的包头用于区分事务种类及确定当前TLP的路由信息等一系列信息[4-5]。传输过程中的信息都需以该数据包的格式进行封装,但其中只有TLP头与有效数据载荷是由用户层进行添加的,其余内容由数据链路层以及PCIe物理层额外添加至TLP上。PCIe统一的TLP传输模式保证了数据传输的稳定性和完整性[6]。

PCIe总线采用差分LVDS串行方式进行数据传输,由两对LVDS差分信号线完成一条链路的接收和发送。

PCIe通信采用点—点的传输技术,能够为系统内设备安排独立的通道,充分保障通信带宽,提高传输速率[7]。

同时,PCIe通信可以实现设备的并行工作,数据通道可以根据具体需要配置成×1、×2、×4等线宽,具备很好的灵活性[8],满足不同设备不同线宽的通信要求。

2 系统结构

智能处理模块应用于航空领域的方向可分为感知类智能算法和决策类智能算法,模块主要根据具体软硬件需求开展智能处理工作。基于上述两类应用,智能处理模塊可提供神经网络类算法的专用智能处理能力、多线程并行运行的通用处理能力、数据传输能力等基础能力,支撑两类算法的应用要求。

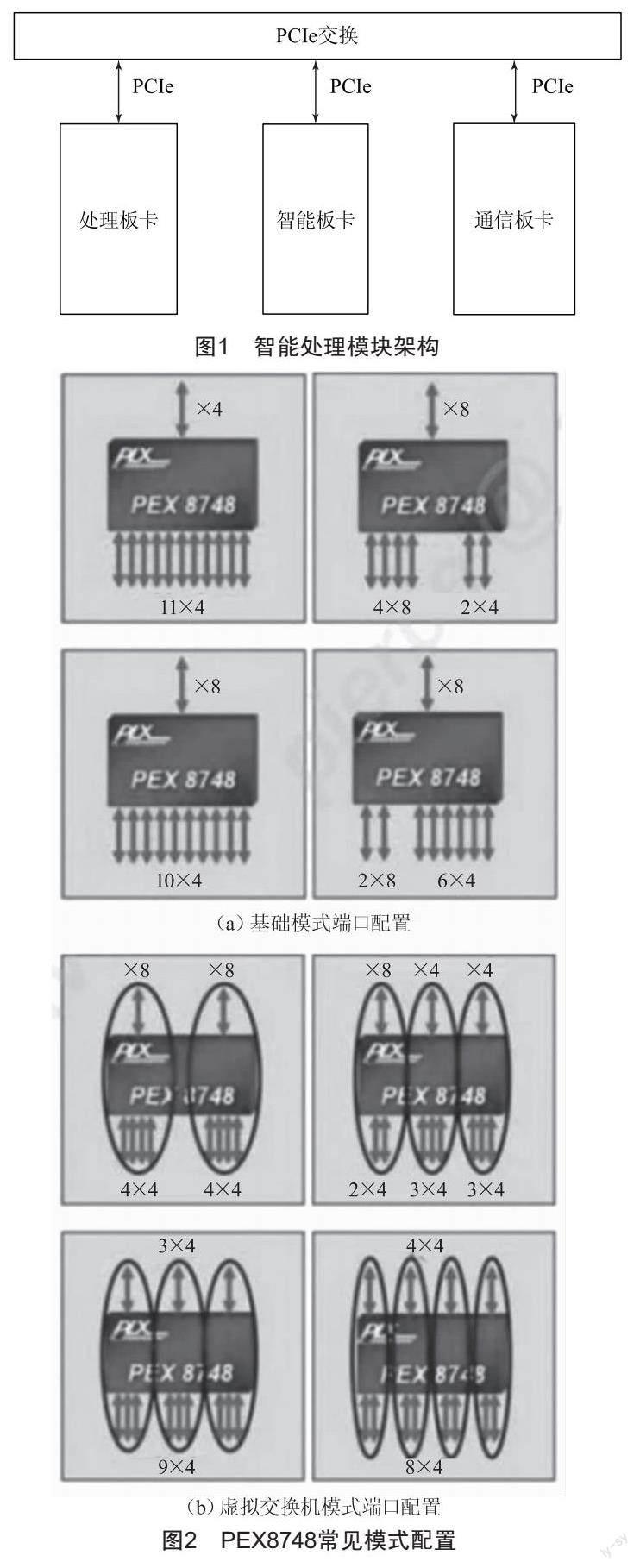

智能处理模块提供通信节点、通用计算节点和智能计算节点。通信节点由FPGA和光电器件组成,负责模块和整机中其他模块之间的通信互联;通用计算节点由多核CPU组成,完成复杂通用计算任务;智能计算节点由大规模FPGA组成,提供足够的计算能力及存储容量,能够满足智能计算处理能力要求。智能处理模块架构如图1所示。

模块内部采用PCIe网络交换结构,各关键节点均连接在PCIe交换网络上,通过PCIe交换网络进行模块间的数据通信。典型应用数据处理流程如下:数据经通信板卡处理后,由PCIe将数据发送给智能板卡的处理内核,处理内核进行响应和资源管理,并将数据转发给智能板卡的逻辑资源进行智能计算,计算结果返回给通用处理器芯片进行处理,最后结果经通信板卡发出。

3 硬件设计

智能处理模块主要由智能、处理、通信三个板卡组成。智能板卡包括两个智能处理器+FPGA,主要实现深度神经网络加速处理以及通信板卡的配置和管理;处理板卡设计两个CPU处理器,主要实现复杂通用计算任务;设计一个PCIe交换芯片,用于模块内部各节点之间高速通信;通信板卡采用FPGA实现通信逻辑,实现对外通信。

智能处理模块的内部通信主要由PCIe总线完成,通过PCIe交换电路实现专用智能节点挂接通信节点,以及智能计算节点和通用计算节点之间互联。PCIe交换功能电路可采用PEX8748芯片实现,PEX8748是一个12端口、48线PCI Express 3.0的总线交换机,单通道最高可支持8.0 GT/s的通信速率。

PEX8748可实现多种配置模式,能够根据具体需求自由设置为上下行模式及多种端口组合,如图2所示。

PEX8748会检测STRAP_TESTMODE0[0:2]来确定运行模式,其中[0,0,0]为BASE MODE,具体设置为BASE MODE,即一主多从的模式;PEX含有3个station,每个station含16lane,由STRAP_STN[0:2]_PORTCFG[0:1]进行端口数目与宽度配置。

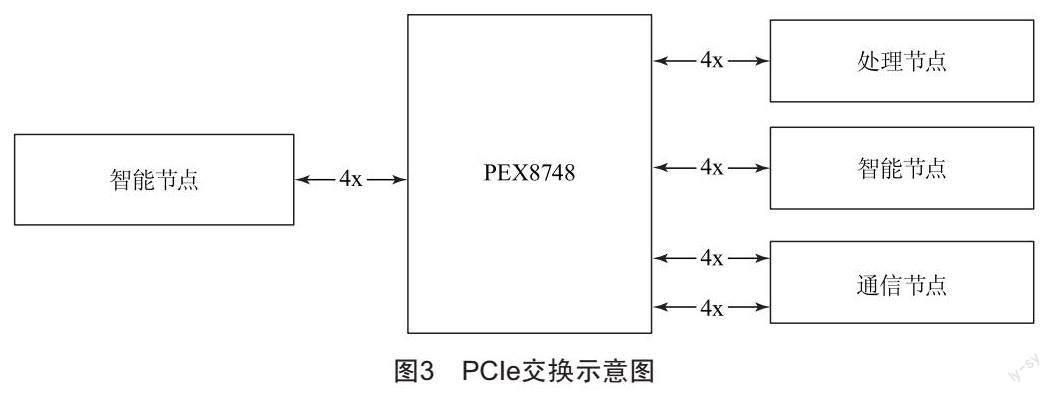

智能处理模块中PEX8748配置多个4x通道,用于连接通用处理节点、智能计算节点和通信节点,如图3所示。

其中智能计算节点接PEX8748的RC上行端口,另一个智能计算节点、通用处理节点和通信节点接PEX8748的EP下行端口。通用计算节点和智能计算节点接口线速率配置为5 Gb/s,通信节点线速率配置为2.5 Gb/s。

4 系统测试

在实际应用中,重点测试系统内部的6个PCIe节点的通信功能,对各个节点之间是否能够传输及传输的正确性进行验证。

具体测试方法为:

1)测试设备向CPU发送“PCIe配置测试”指令,随后测试设备接收各节点发送的PCIe链路状态及线宽寄存器结果,各寄存器参数读取与预期一致,说明节点配置正常。

2)CPU通过PCIe接口将数据发送至另一个CPU的BAR空间,然后从BAR空间中将数据读回,对比发送数据和读回数据是否一致,如一致则测试通过。

3)CPU针对通用计算节点及智能计算节点“PCIe接收通信测试”指令,进行PCIe的Direct IO包的读写测试,在1 s时间内连续进行读访问,测试PCIe的读访问带宽,并将带宽发送给测试设备判断读访问带宽是否合格。

4)CPU针对通用计算节点及智能计算节点“PCIe接收通信测试”指令,进行PCIe的Direct IO包的读写测试,在1 s时间内连续进行写访问,测试PCIe的写访问带宽,并将带宽发送给测试设备判断写访问带宽是否合格。

5 结束语

本文提出了一种基于PCIe接口的智能处理系统,该系统基于CPU+FPGA的异构融合结构设计,通用处理节点基于高性能多核CPU设计,提供两个通用处理节点和两个智能处理节点,并通过对外通信接口实现外部交互。系统通过PCIe交换电路完成内部数据通信,通用计算节点和智能计算节点接口线速率配置为5 Gb/s。该系统为应用于航空领域的人工智能系统,可实现飞行过程中的智能感知、辅助决策等任务。

文中对该智能处理系统的整体架构进行了详细描述,介绍了系统中PCIe总线的工作模式及其内部信号的数据流,并从硬件角度阐述了系统核心电路的设计思路,重点分析了PCIe总线的使用及其优越性。

该架构适用于高性能和高效率的智能处理系统,已成功应用于某机载智能处理模块,对相关领域应用具有一定的参考价值和借鉴意义。

[参考文献]

[1] 吕伟,钟臻怡,张伟.人工智能技术综述[J].上海电气技术,2018,11(1):62-64.

[2] 洪畅,翟栋梁,丁志辉.一种基于PCIE总线的高性能数据传输架构设计[J].现代电子技术,2023,46(21):6-10.

[3] 毕城,元永红.基于PCIe总线的多处理器数据交换技术[J].电子科技,2017,30(7):118-120.

[4] 李勝蓝,姜宏旭,符炜剑,等.基于PCIe的多路传输系统的DMA控制器设计[J].计算机应用,2017,37(3):691-694.

[5] 赵珊珊.PCIE高速数据传输系统设计[J].电脑知识与技术,2017,13(4):32-33.

[6] 王帅,李念强,许惠翔.基于Altera IP核的FPGA PCIE接口设计[J].工业控制计算机,2017,30(2):41-42.

[7] 王元强,聂云杰,朱孟江,等.一种基于FPGA的PCIe总线高速异步传输系统[J].单片机与嵌入式系统应用,2018,18(8):62-64.

[8] 邹昀辛,吴楫捷,王伟,等.基于PCIe总线多主互连系统的设计与实现[J].计算机工程与设计,2017,38(9):2314-2318.

收稿日期:2023-12-19

作者简介:胡益诚(1992—),男,浙江江山人,硕士研究生,工程师,研究方向:嵌入式硬件设计、计算机应用。

王树争(1984—),男,陕西西安人,硕士研究生,高级工程师,研究方向:嵌入式硬件电路设计、计算机系统结构等。

李碧涵(1993—),女,四川成都人,硕士研究生,工程师,研究方向:嵌入式计算机设计。