基于XC7V690T的在轨抗单粒子翻转系统设计

2024-04-01张嘉伟朱昶文江亚州

夏 俊,张嘉伟,孙 晨,朱昶文,江亚州

(1.上海卫星工程研究所,上海 201109;2.上海航天电子技术研究所,上海 201109)

0 引言

航天器在轨运行期间,会遭遇多种恶劣的空间天然辐射环境的影响,这些辐射包括宇宙射线、空间高能粒子(高能电子和质子)等[1]。由空间高能粒子导致的单粒子翻转(SEU,single-event upsets)对航天器在轨稳定、可靠的运行造成严重的威胁,发生严重错误时甚至会导致航天器软件执行错误引起姿态失控等重大故障,因此,单粒子翻转问题一直以来都是航天领域不可忽视的问题。采用宇航级等高等级元器件,可有效降低航天器电子系统受单粒子翻转影响的概率。但一方面,抗单粒子翻转高等级加固器件的价格非常昂贵,且品种有限,同时由于政治和军事原因还受到国外禁运;另一方面,航天器性能要求越来越高,功能要求越来越复杂,部分高等级器件受限于逻辑资源等无法适用。因此,越来越多的工业级大规模现场可编程门阵列(FPGA,field programmable gate array)开始逐步应用于航天领域。信号处理核心工作器件XC7V690T-2FFG1761I为工业级静态随机存取存储器(SRAM,static random-access memory)型FPGA芯片,已逐步开始应用于各类航天器中,但由于其抗辐照能力较弱,在轨运行期间存在单粒子翻转的风险。为保障航天器在轨安全运行,需专门开展针对XC7V690T的抗单粒子系统架构设计。

国内外相关研究机构对单粒子防护设计方法进行了一些研究,文献[2]和文献[3]提出常见的刷新方法主要有内部刷新和外部刷新。其中内部刷新是利用FPGA的内部配置访问接口(ICAP,Internal Configuration Access Port)对配置数据进行回读刷新,内部刷新最大的优点在于不用配置单独的外部刷新芯片,刷新效率更高。另外,外部刷新的主要方法有回读刷新和定时刷新。回读刷新是采用外部刷新芯片对配置数据进行回读与检测,外部刷新的硬件架构较为复杂且刷新效率略低。定时刷新是指按照预先设计的时间长度对配置数据进行刷新,定时刷新的效率较低。文献[4]提出了一种基于软错误缓解(SEM,Soft Error Mitigation)的抗单粒子翻转方法,该方法刷新效率较高,同时也降低了SEM核自身发生单粒子翻转的概率。文献[5]提出了一种FPGA在轨重构的方法及工程实施方案,通过实时刷新结合三模冗余(TMR,Triple Modular Redundancy)设计可以有效降低FPGA发生单粒子翻转的概率。文献[6]提出了一种通过在轨自主重构的方法,有效减少单粒子翻转的次数。

综上,针对在硬件加固设计及软件加固设计基础上,为了提高工业级SRAM型FPGA芯片XC7V690T在轨抗单粒子翻转能力及配置文件注数修改的灵活性,对某航天器通信机基于XC7V690T的抗单粒子系统架构(主要包括硬件架构、软件架构的设计与实现)以及在轨验证情况分别进行介绍。

1 单粒子翻转防护设计

航天器电子系统单粒子翻转防护设计的目标主要有以下两方面:1)要确保在发生单粒子翻转时不影响航天器的主要业务,确保航天器业务的连续性;2)要确保在发生单粒子翻转时不影响航天器的安全,确保航天器姿态、能源、测控信道等稳定可靠。为系统推进单粒子翻转防护工作,主要是要强化系统、单机、器件等全层级的单粒子翻转防护设计措施,提升航天器的单粒子翻转防护设计水平,降低单粒子翻转对航天器在轨运行的影响。下面主要对航天器目前采用的一些单粒子翻转防护设计进行系统性的介绍。

1)元器件选用:

采用宇航级等高等级元器件,可有效降低航天器电子系统受单粒子翻转影响的概率。

在单粒子翻转方面,没有经过抗SEU加固的器件,通常具有较低的线性能量传递(LET,linear energy transfer)阈值和较高的在轨翻转率,而经过了SEU加固的器件可具有较高的LET阈值和较低的在轨翻转率[7]。

2)错误检测与纠正:

错误检测与纠正(EDAC,error detection and correction)是抗单粒子翻转的有效技术之一[8-10],在航天领域已广泛应用于随机存取存储器(RAM,random-access memory)、带电可擦可编程只读存储器(EEPROM,electrically erasable programmable read-only memory)的抗单粒子翻转防护设计。对于以上常用的RAM、EEPROM等存储器,同时在不同区域发生多bit翻转的概率非常低,因此可以利用EDAC的方法来对1 bit翻转错误进行自动检测与纠正。采用EDAC的方法的主要目的是容忍单粒子翻转的发生,通过采用错误检测并予以纠错的方式避免单粒子翻转错误对系统性能造成更大的影响。可用于EDAC方法的纠错码比较多,常用的纠错码主要有汉明码、卷积码以及R-S(Reed-Solomon)码等,不同的纠错码方式各具特点,需要针对实际应用场景选择适合的编码方式。

3)冗余设计:

冗余设计也是抗单粒子翻转的有效技术之一[11],在航天领域已得到广泛应用的冗余设计主要是三模冗余设计,三模冗余设计的主要目的是通过将原有的功能模块扩展为3个一模一样的模块,通过一个三取二表决器对3个功能模块的输出结果进行表决,以解决即使其中某一模块因为单粒子翻转功能受到影响,也不影响三取二的最终结果,提高了航天器电子系统的可靠性与安全性。通过对整个功能模块进行三模冗余的设计对航天器电子系统抗单粒子翻转性能有很大的提升,但是逻辑资源会增加3倍,对资源的开销会比较大,因此在FPGA逻辑资源不是很充足的情况下要实现所有功能模块全部三模冗余在工程上是很难实现的。除了功能模块的三模冗余,其他的三模冗余方式还有关键参数三模冗余、关键寄存器三模冗余等。对关键参数和关键寄存器的三模冗余,主要环节是要准确识别出哪些关键参数及关键寄存器在航天器软件运行过程中被单粒子打翻或被非正常篡改时会触发较为严重的问题,涉及到航天任务中所使用的各系统软件的性能、可靠性和安全性等方面。对于这些影响到航天器正常运行的关键参数与寄存器,往往需要进行三模冗余的设计,而对关键参数和关键寄存器进行三模冗余设计的资源消耗要比模块级三模冗余要低得多,工程可实现性更高。

4)刷新:

刷新(Scrubbing)方法主要有内部刷新和外部刷新。其中内部刷新是利用FPGA的内部配置访问接口对配置数据进行回读刷新。外部刷新主要的方法有回读刷新和定时刷新。回读刷新是采用外部刷新芯片对配置数据进行回读与检测,该方法中,SRAM型FPGA的配置文件一般存放在于可编程只读存储器(PROM,programmable read-only memory)中,PROM中的配置文件具有一次固化即无法修改的特性,因此其抗单粒子翻转的能力非常高[12],利用独立的反熔丝FPGA按一定的频率对配置文件进行回读,并与存放于PROM中的配置文件进行实时比对,如果发现校验数据比对不成功,则自主进行程序的重新加载。该方法也是现阶段航天领域抗单粒子翻转比较主流的一种设计方法[13-19]。定时刷新则是按照预先设计的时间长度对配置数据进行定期刷新。

5)重构:

重构方法主要是指在轨运行过程中因程序中的安全性可靠性设计欠缺,通过地面遥控上注全新的配置文件,并取代原始版本的过程,通过重构的方式,可以灵活的解决在轨的一些不可预料的问题,提高软件运行的可靠性,有效降低空间单粒子对航天器电子系统的影响,目前越来越多的航天器开始采用在轨重构的方法来进行软件的升级,提升软件的健壮性[20]。

6)指令复位或重启:

目前绝大多数在轨长加电航天器电子系统均设计有指令复位或重启功能,在轨遇到单粒子翻转事件导致电子系统功能异常时,可以通过地面遥控指令进行复位或重启。针对重要的长加电产品,航天器星载计算机软件一般会设计自主异常监视功能,若出现异常可通过星载计算机自主指令复位或重启,用以解决长加电产品在轨单粒子翻转问题,提升系统自主恢复的能力。

除了以上目前主流的采用的抗单粒子翻转防护设计方法外,还有以下一些方法可用于单粒子翻转防护设计。

1)模拟器件单粒子翻转防护:

单粒子翻转不仅仅出现在逻辑器件中,对于具有双稳态器件的模拟电路,也存在发生单粒子翻转的可能,如电压比较器。在电压比较器的应用中,比较器的输入端电压差设计成尽可能大,可有效地防止电压比较器产生单粒子翻转。

2)看门狗(WDT,watchdog)复位:

看门狗复位也是目前航天器电子系统用于避免因单粒子翻转造成电子产品程序运行异常的一种常用方法。当电子产品因单粒子翻转导致程序跑飞时,无法按照预定的时间周期进行喂狗操作,看门狗芯片发出复位信号使得软件能够恢复初始状态重新执行,避免因单粒子翻转造成的软件跑飞而影响整个任务。

3)利用累加和检查存储器内容的正确性:

对固化后的星上程序进行累加和计算,将其作为自测试的判断基准,存储在特定区域内。运行过程中定期进行累加和计算,根据任务情况决定取全累加和或分段累加和,并与所存储的基准值比对,若不等,则由系统进行容错切换管理。这种常用的容错手段,也是对单粒子翻转是否引起程序异常的有效判断方法。

此外,还可以采用自诊断程序、多重编码、指令重复执行、分支流程作两次以上有效性判别、建立健康和安全模式、地面遥控注入等方式提高系统抗单粒子能力。

2 硬件架构设计

某航天器通信机采用侧向层叠结构形式,共分为4个模块,由后至前依次为电源模块、射频模块、刷新模块及信号处理模块。电源模块接收航天器平台提供的一次电源,转换输出单机内其他模块正常工作所需要的各路电源。刷新模块包含了上电程序配置、健康监控和在轨重构的功能。射频模块接收天线经双工器发送过来的上行信号,通过混频、滤波、放大等转换成中频模拟信号,送给信号处理模块。射频模块还接收信号处理模块发送过来的中频模拟信号,经正交上变频、放大、滤波后转换成下行射频信号,经双工器后再通过天线发射出去。

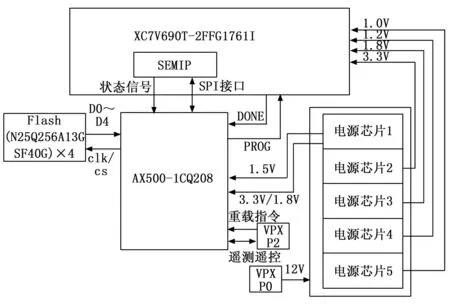

通信机信号处理及刷新模块设计框图如图1所示,采用了Xilinx公司的SRAM型FPGA XC7V690T平台,主要具备以下功能:

图1 模块设计框图

1)接收射频模块发送过来的中频模拟信号,通过模数转换芯片采集后转换成12 bit位宽的数字信号,传送给XC7V690T芯片进行信号处理;

2)将信号数据码流经XC7V690T芯片进行处理后,通过数模转换芯片进行转换形成中频模拟信号,发送给射频模块;

3)针对XC7V690T芯片的加载、刷新及重构功能。

针对该硬件架构,主要给出模块层和器件层的加固设计方案,针对XC7V690T FPGA的加固设计主要由三部分组成:电源监控电路和控制电路、XC7V690T FPGA内部调用的SEM核和充当监控和维护核心的AX500 FPGA。AX500 FPGA除了需要监控XC7V690T FPGA配置和SEM工作状态,还要负责监测和控制XC7V690T的供电情况,在识别故障后通过刷新和重上电等手段进行故障恢复。

该硬件架构由XC7V690T芯片、反熔丝FPGA AX500芯片和4片512 Mb容量的FLASH存储器组成。其中:

1)XC7V690T芯片为需进行加固设计的FPGA 器件;

2)FLASH 用来存储XC7V690T芯片的配置文件;

3)AX500芯片的主要功能为读取FLASH中的配置信息、上电加载和重载XC7V690T芯片、监控SEM IP核的状态。AX500芯片与XC7V690T芯片接口中的SPI-1为专用配置管脚,用来加载或重载FPGA。

3 软件架构设计

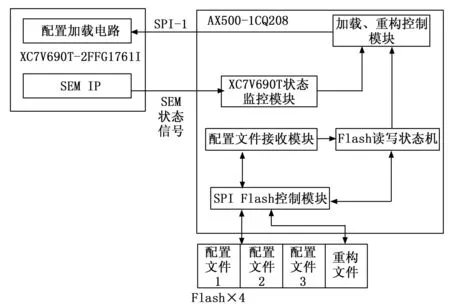

系统软件架构框图如图2所示。AX500芯片在上电时读取FLASH中的配置信息,通过SPI接口加载目标XC7V690T芯片,加载完成后,监测XC7V690T芯片的SEM IP核返回的状态信号,若检测到配置数据错误、SEM IP核自身发生错误或发生不可纠正的错误,则视需求读取FLASH中的配置信息对目标XC7V690T芯片进行重载操作。

图2 软件架构框图

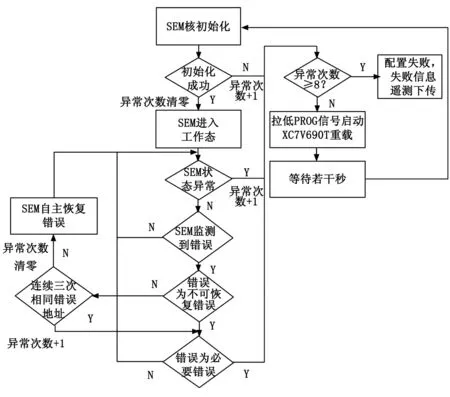

3.1 XC7V690T配置管理和监控

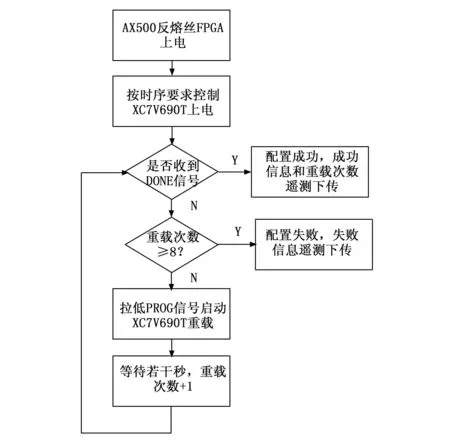

AX500反熔丝FPGA监控XC7V690T的配置状态,通过监控XC7V690T的DONE信号,若一定时间(外部须有时间跳线选择)内反熔丝FPGA未收到DONE信号,表示XC7V690T未配置成功。此时,AX500反熔丝FPGA拉低PROG信号对XC7V690T重新配置(热启动)。若热启动次数超过8次后仍未成功配置XC7V690T,表示无法进行板内重载,AX500反熔丝FPGA通过遥测链路将模块故障信息下传地面。热启动重载流程图如图3所示。

图3 热启动流程图

在热启动无法成功配置时,需要通过发送指令进行干预。该情况下,收到地面遥控指令,可以启动断电操作,通过断电重载进行恢复。若冷启动8次仍未成功配置XC7V690T,AX500反熔丝FPGA将其断电,并通过遥测链路将模块故障信息下传地面。冷启动加载流程图如图4所示。

图4 冷启动流程图

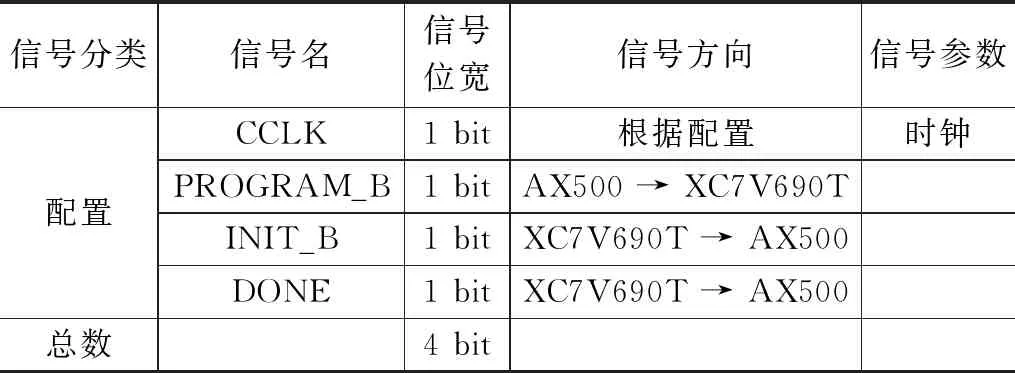

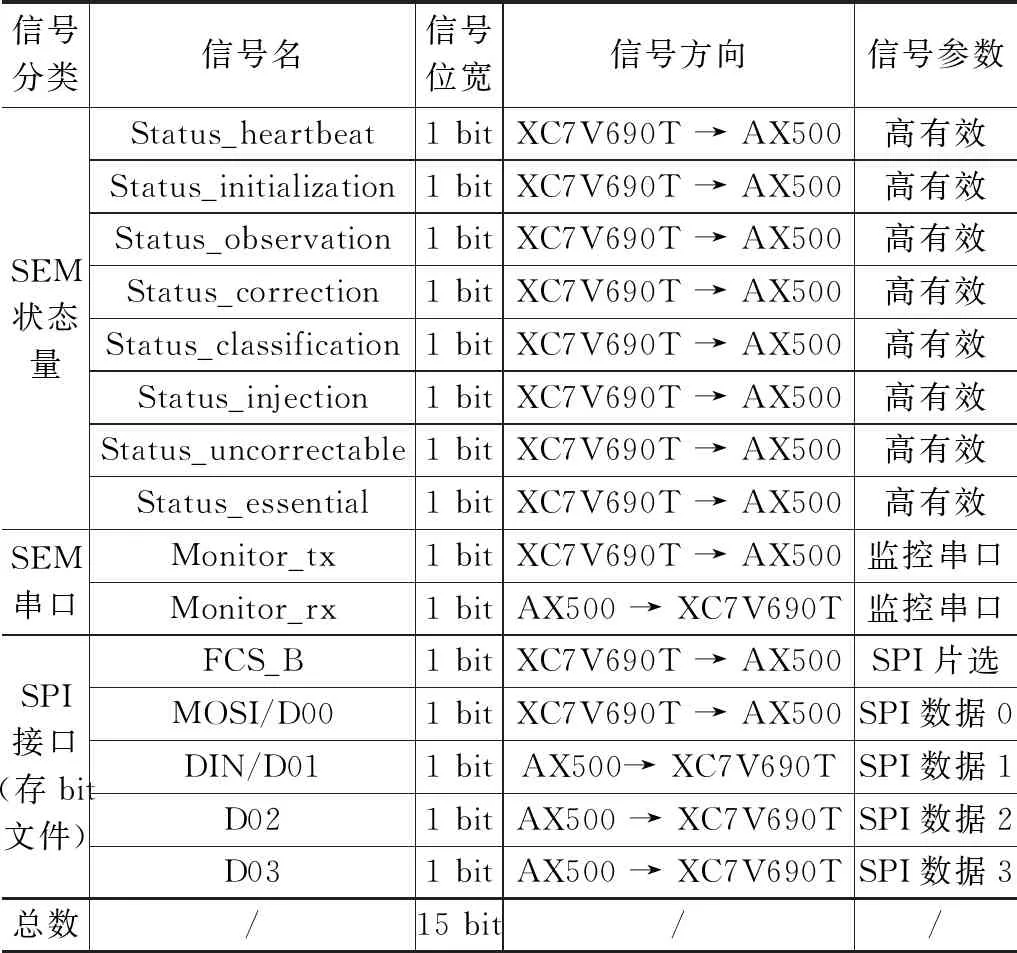

XC7V690T与AX500配置监控接口具体信号如表1所示。

表1 XC7V690T与AX500配置监控接口

3.2 XC7V690T SEM管理和监控

XC7V690T内部调用SEM IP核实现对配置RAM资源的自主监控和维护。SEM核利用片内的ICAP接口访问配置RAM资源,并通过自带的差错控制编码(ECC,error correcting code)和循环冗余校验码(CRC,cyclic redundancy check)校验资源识别发生翻转的配置RAM位,并能进行自动修复。

该功能可以配置成3种模式。

1)修复模式:以ECC算法为基础,可以纠正所有的单比特软错误;

2)增强修复模式:以ECC和CRC算法为基础,能修复任意的单比特和相邻双比特的翻转软错误;

3)替换模式:能够修复任意多个比特错误。

SEM通过片内ICAP接口访问配置RAM,而传统的回读刷新通过片外SelectMAP接口访问配置RAM,两种接口的时序效率相差不大,但是外部回读需要通过PCB走线,还要考虑反熔丝FPGA的频率限制,所以主频通常远低于FPGA内部ICAP频率,因而需要更多时间,这使得SEM的故障识别时间远低于外部的回读刷新。

同时,由于XC7V690T FPGA没有公开配置帧的结构,无法进行精确的局部刷新,而全局刷新耗时长,并且其中绝大多数的刷新操作没有实际意义,加固效率较低。SEM技术则能够通过局部刷新的手段,实现非常高效的故障恢复。

根据具体应用情况,SEM IP选择增强修复模式的纠错策略。XC7V690T与AX500 SEM监控接口具体信号如表2所示。

表2 XC7V690T与AX500 SEM监控接口

然而,SEM本身仍然有可能会因为单粒子翻转而发生故障,虽然发生这种情况的概率要远远低于FPGA本身发生单粒子翻转的概率,但仍然有必要针对这种情况设计故障恢复预案。通过反熔丝FPGA直接监控SEM的状态信息,可以判断SEM功能是否正常工作,并在发生故障时通过重载(热启动)进行恢复。

反熔丝FPGA需要启动重载操作的异常内容包括:

1)SEM核未能成功完成初始化;

2)SEM核在工作状态时发生异常;

3)SEM核监测到不可恢复并且是必要比特错误;

4)SEM核监测到连续三次相同地址的必要错误。

当出现上述情况时,反熔丝FPGA尝试对XC7V690T进行重载(热启动)恢复,并且将异常计数+1。如果累积符合8次都未能恢复该异常,则反熔丝FPGA停止重载恢复,并通过遥测链路下传相关故障信息。

XC7V690T SEM监控流程图如图5所示。

图5 XC7V690T SEM监控流程图

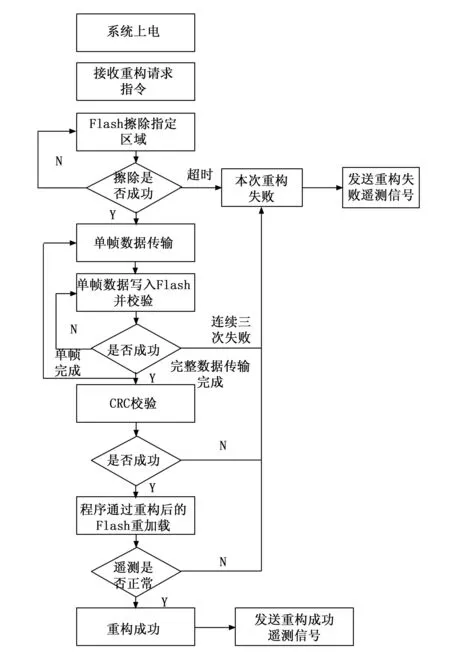

3.3 配置FLASH控制及重构

采用3片FLASH存储配置程序,用于配置文件三取二校验功能。为了进一步提升可靠性,新增1片FLASH用于在轨重构。第4片FLASH用于在轨重构(第1~3片FLASH在轨期间不可进行写操作),重构数据流通信接口为异步RS422接口。

XC7V690T输出至反熔丝FLASH的访问接口SPI,用于访问bit配置文件。而反熔丝FLASH则需要维护4片SPI型FLASH。当XC7V690T需要访问自己的配置FLASH时,反熔丝FPGA会通过SPI接口发来的请求,反熔丝FPGA解析SPI指令和地址,并根据当前的配置模式,选择对4片SPI FLASH进行操作。

在轨重构工作流程设计如下:

1)地面发送遥控指令,请求重构,并告知重构区域(FLASH内存空间内的首地址及长度)。

2)单机收到指令后对目标FLASH中的对应区域进行擦除操作,擦除完成后发送遥测数据告知擦除完成,若超过指定时间后擦除仍未完成,则判定擦除失败,FLASH中该部分区域失效。

3)单机通过异步RS422接口接收重构数据流,每接收一帧(帧长与FLASH芯片的页长度相符)数据,写入FLASH中,并根据接收到的CRC值对FLASH中的该帧数据进行校验,如校验通过,则发送校验通过信号,请求接收下一帧数据,反之,则反馈校验失败信号。数据发送方收到失败信号后重新发送该帧数据,如连续收到三次失败信号,则跳出本次重构流程。

4)当单机收到整个程序的校验指令和校验CRC值时,表示完整数据流已传输完毕,单机启动整个程序的CRC校验,校验失败则表示本次重构失败,反之,则复位FPGA芯片,通过重构后的FLASH芯片重新加载程序,如遥测参数正常,方可判定为本次重构有效,单机通过遥测接口反馈该次重构结果(成功/失败)。

重构流程示意图如图6所示。

图6 重构流程示意图

4 实验结果与分析

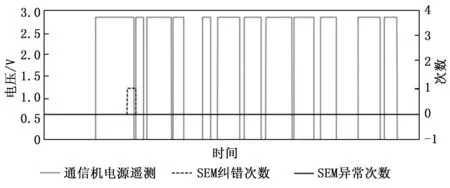

采用该系统架构在某航天器通信机上完成了在轨验证。在轨期间对该通信机进行了多次测试,如图7所示,在轨测试期间共进行了12次开关机,通信机均加载正常,三取二报错计数为零。

图7 三取二报错计数在轨测试结果

在轨测试期间,XC7V690T内部SEM IP核成功进行了一次SEM纠错,未造成SEM异常(SEM异常计数为零),如图8所示,未影响通信机的正常功能。

图8 SEM纠错次数及异常次数在轨测试结果

在轨验证结果表明,在航天器运行过程中,采用本方案多次圆满地完成了XC7V690T加载与刷新,单机在轨工作稳定正常。此外,重构措施在地面研制阶段,进行了重构验证,提供了方便的程序更换手段。

5 结束语

针对核心工业级SRAM型FPGA芯片XC7V690T抗辐照能力较弱,在轨运行期间存在单粒子翻转的风险的问题,提出了一种基于XC7V690T的在轨抗单粒子翻转系统架构。在轨验证结果表明,采用工业级SRAM型FPGA芯片XC7V690T的某航天器通信机在轨测试过程中成功进行了SEM纠错,通信机在轨工作正常,通信链路稳定,满足使用要求。表明该系统架构可以有效提升XC7V690T抗单粒子翻转能力,可以为其他SRAM型FPGA抗单粒子翻转设计提供借鉴与参考。