一种基于MIPI D-PHY物理层的高速比较器

2024-03-31张欣瑶黄尊恺封松林

张欣瑶, 黄尊恺, 汪 辉, 田 犁, 汪 宁, 封松林

(1.中国科学院上海高等研究院,上海 201210; 2.中国科学院大学 集成电路学院,北京 100049)

0 引 言

移动产业处理器接口(mobile industry processor interface,MIPI)是由MIPI联盟发起的,该协议的提出简化了设备内置组件的集成,同时标准化不同供应商产品之间的接口,提高了移动设备的兼容性[1-2]。MIPI协议的出现有效地缩短了产品上市时间和移动设备的研发成本,通过该协议MIPI实现了更高的数据传输速率和更丰富的通用功能。相较于传统的接口电路,如数字视频接口[3](digital video port,DVP)和低压差分信号[4](low-voltage differential signaling,LVDS)接口等,MIPI具有低电压摆幅、低功耗、高数据传输速率等优点,被广泛应用于智能手机和平板电脑等便捷设备中。

MIPI D-PHY物理层属于模拟电路模块,在上层调配下实现模式的切换,是实现数据底层传输的基础。其中高速接收端是决定数据传输中信号接收完整性以及传输速率的关键模块。传统的高速接收电路均采用信号由栅极进行输入的形式,且电路中有额外电流源偏置,导致差分信号的共模电压接收范围小且功耗增加。基于MIPI D-PHY传输协议,本文针对传统的高速接收端电路结构进行改善,设计一款接收速率达到2.5 Gb/s的自偏置低功耗高速比较器。相较于传统的高速比较器,本文提出的电路结构数据接收速率更高、功耗更低且共模电压接收范围更广。通过对此电路结构的小信号模型分析以及后仿真验证,结果表明高速比较器能够实现低共模电平差分信号的准确接收。

1 MIPI D-PHY简介

1.1 MIPI D-PHY的电气特征

MIPI D-PHY是针对DSI和CSI协议的高速、低功耗的源同步物理层。此协议可用于定义移动设备的处理器与摄像模组、显示模组之间的连接方式。

相较于传统的最小化差分信号传输(transition minimized differential signaling,TMDS)和低压差分信号传输(low voltage differential signaling,LVDS)等传输接口,MIPI D-PHY具有高速、低功耗的传输特点。该传输优势在于MIPI D-PHY定义的高速(high speed,HS)模式和低功耗(low power,LP)模式2种传输模式,2种模式使用不同的传输机制。

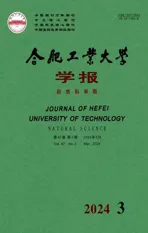

MIPI D-PHY 2种模式的电气特征如图1所示。HS模式用于传输信息量比较庞大的数据及时钟信号,使用低摆幅的差分信号进行传输,有利于抗电磁干扰和降低功耗,一个通道的数据传输速率范围在0.08~ 1.50 Gb/s;LP模式用于传输低速的控制命令信号,采用单端信号进行传输,数据率一般不大于10 Mb/s。HS模式和LP模式的相互配合实现在传输高速信号的同时节省功耗,在上层的调配下实现按需进行HS模式与LP模式的转换,达到高速率与低功耗的折衷设计。从图1可以看出,在HS模式下信号通过低电压摆幅的差分信号进行传输,信号电平在0.1~0.3 V(共模电平0.2 V,差模电平0.2 V);LP模式下为单端信号传输,数据率一般不大于10 Mb/s,信号电平[2]为0~1.2 V。

图1 D-PHY 2种模式的电气特征

1.2 MIPI D-PHY通道的工作原理

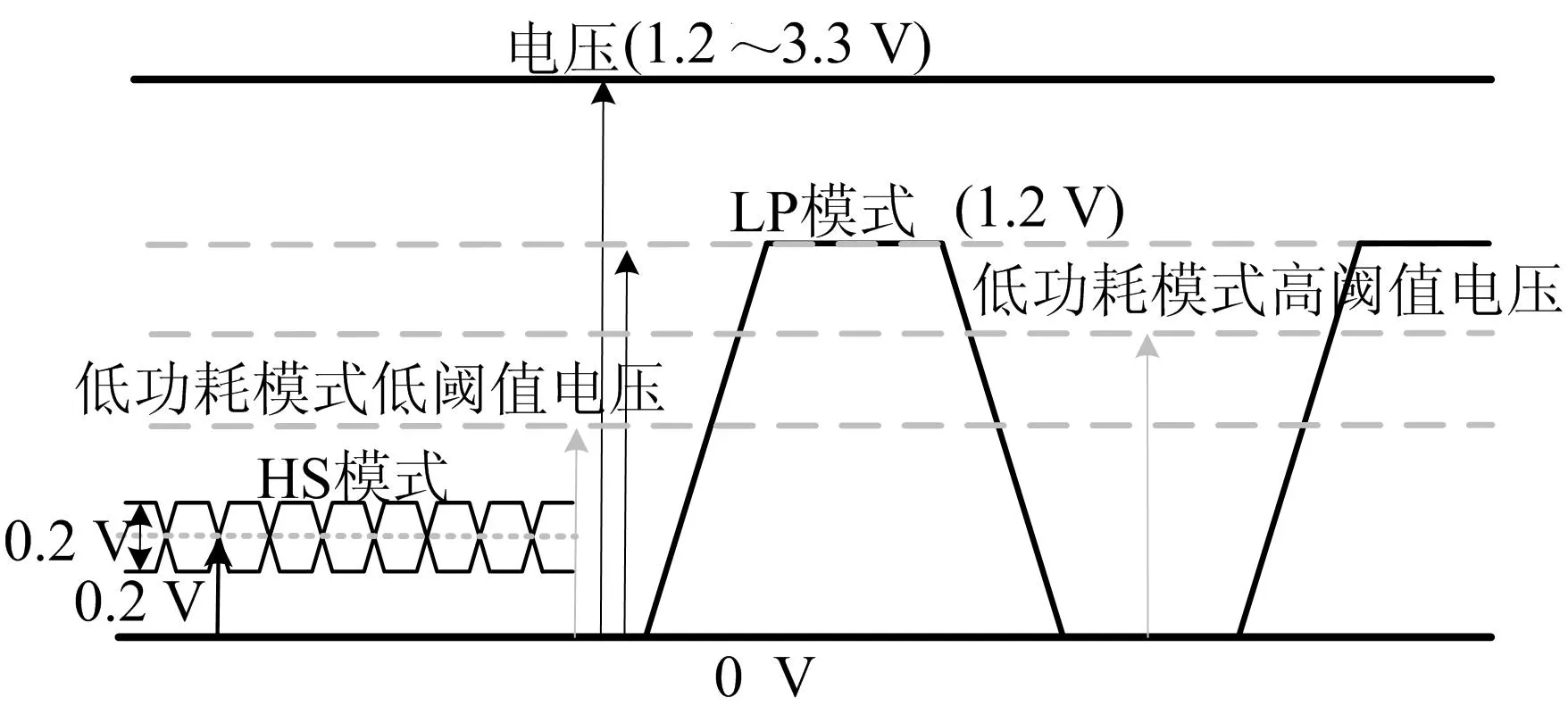

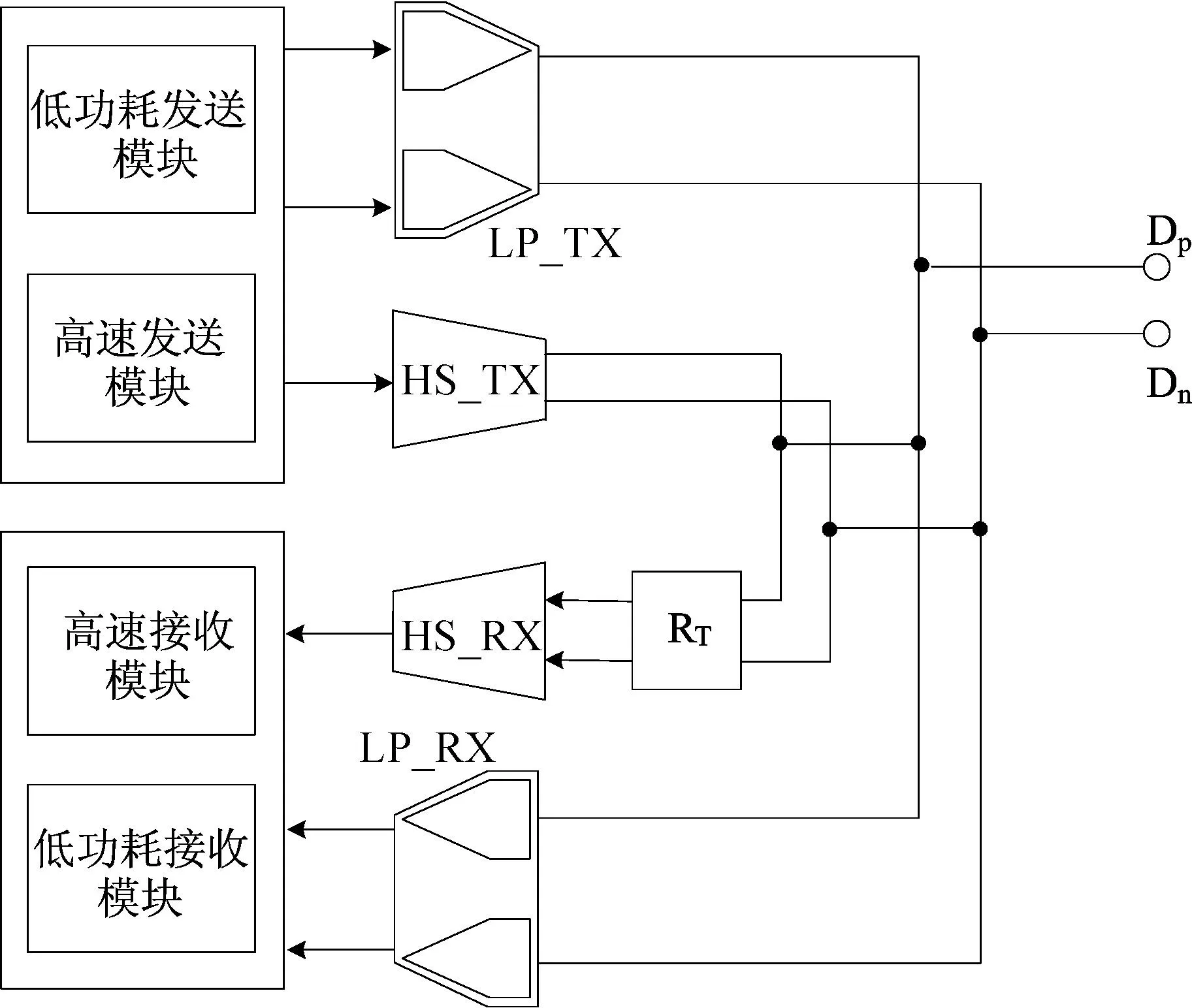

MIPI D-PHY通道包含突发模式、控制模式和逃离模式3种操作模式。D-PHY通道状态见表1所列,在高速模式时,Dp、Dn代表高速数据的2条差分信号,产生高速模式的逻辑高、低2种输出格式。当Dp为逻辑低电平、Dn为逻辑高电平时,代表输出格式为高速模式的逻辑低电平;当Dp为逻辑高电平、Dn为逻辑低电平时,代表输出格式为高速模式的逻辑高电平。相较于高速模式,低功耗模式下根据Dp、Dn不同的组合有4种输出格式。

表1 D-PHY通道状态

在控制模式下,线路默认处于停止状态,状态转换由此开始,结束后回到此状态。低功耗-01、低功耗-10分别代表高速模式请求和低功耗模式请求,当通道要进入高速模式或者逃逸模式,发送模块驱动线路为低功耗-01或低功耗-10,在发送请求序列之后便进入了相应的工作模式。发送低功耗-11便退出传送回到初始停止状态[5]。接收端需要时刻进行低功耗接收端的接收,侦测线路电平明确通道的工作模式。

2 整体结构和电路设计

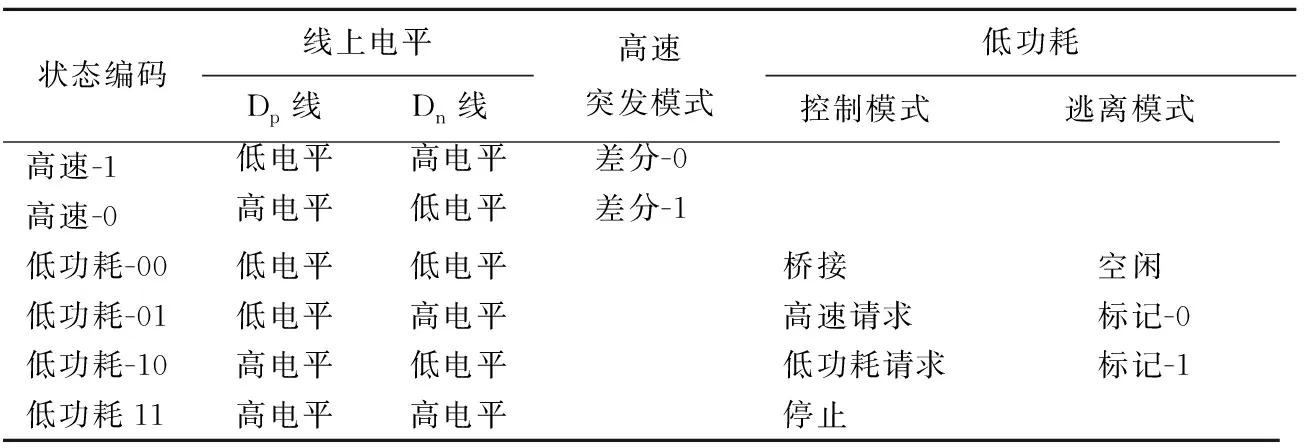

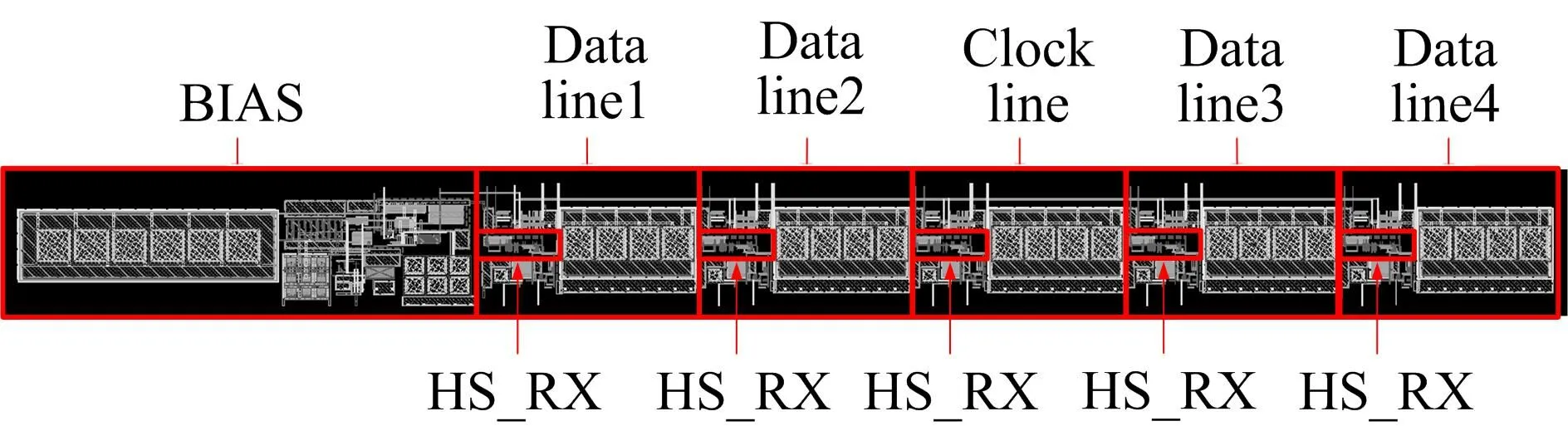

MIPI D-PHY物理层的整体结构如图2所示,图2中包含高速发送模块(HS-TX)、高速接收模块(HS-RX)、低功耗发送模块(LP-TX)和低功耗接收模块(LP-RX)4种模块[6]。HS-TX和HS-RX组成HS模式,LP-TX和LP-TX组成LP模式。每条数据通道上仅有2根数据线Dp、Dn,负责在不同物理层模块之间进行数据传输及状态的转换,且时钟通道上的D-PHY物理层与数据通道电路结构相同,整体结构使用1条时钟通道、4条数据通道。

图2 D-PHY整体功能结构

2.1 高速发送模块

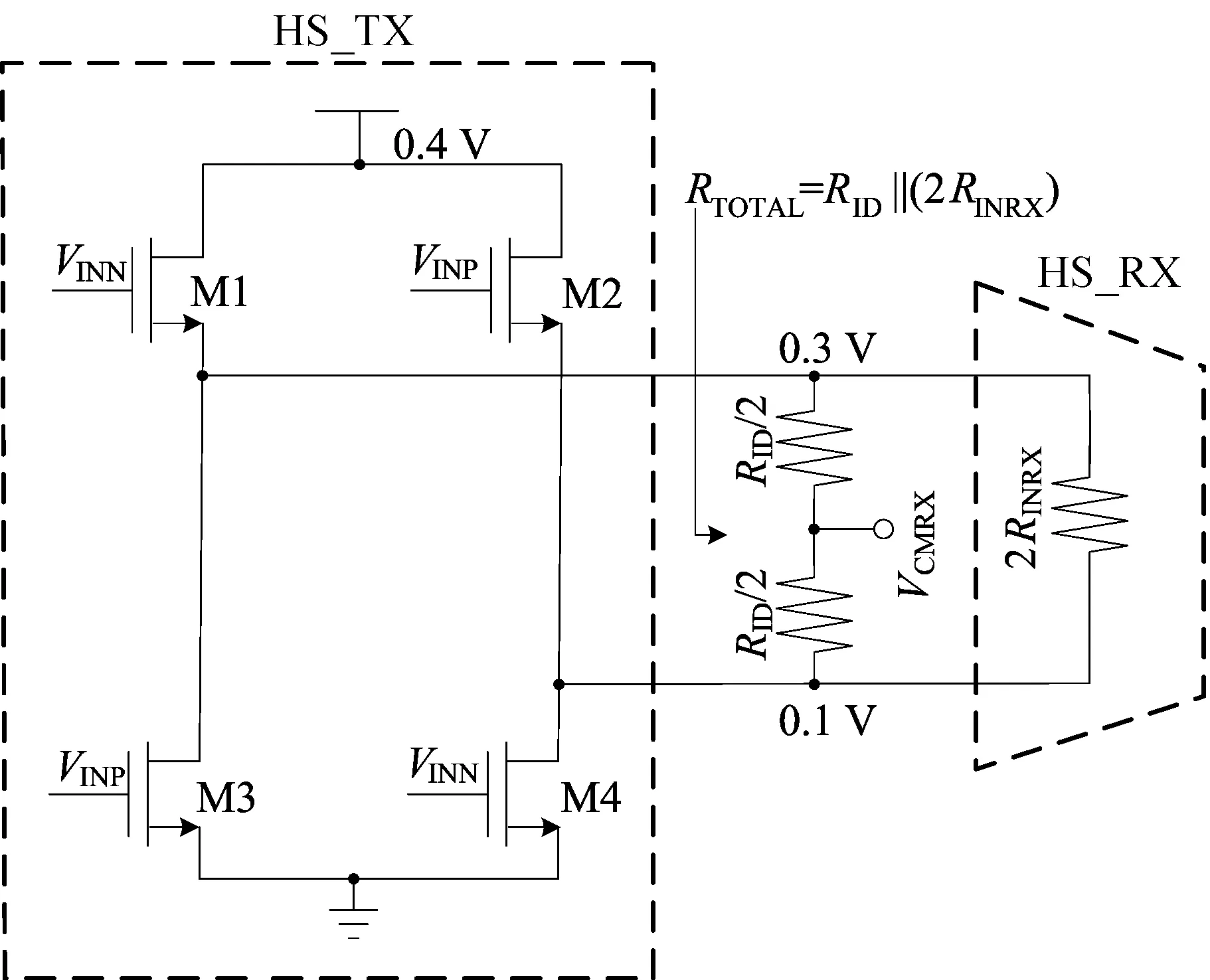

高速发送模块将数字端输入的单端信号转换成0.1~0.3 V的差分信号并进行发送,此模块由单端转差分电路以及开关管组成。高速模式的整体结构如图3所示,VINN、VINP是单端转差分模块输出0~VDD摆幅的差分信号,此信号输入到由M1、M2、M3、M4组成的开关管中。M1、M2、M3、M4由0.4 V电源电压供电,在正常工作过程中工作在线性区,等效为50 Ω的电阻。HS-RX接收电阻RID为100 Ω,在0.4 V的电源电压下由于电阻分压作用实现0.1~0.3 V的差分信号输出。

图3 高速模式整体结构

由图3可知,高速接收端的等效输入电阻对数据通路上差分信号电平也有一定的影响。图3中:2RINRX为HS-RX端等效输入电阻;RID为HS-RX的接收电阻,值为100 Ω。设ROD_H、ROD_L分别为M1、M2和M3、M4的等效电阻;VDD_IO为HS-TX端0.4 V电源电压,因此HS-RX接收到的差分电压可以表示为:

(1)

其中,RTOTAL为总等效输入电阻,即

RTOTAL=RID//(2RINRX)

(2)

在实际设计中,HS-RX端输入电阻RINRX应该远远大于终端电阻RID,减少由于高速接收端的有限输入电阻引起的总电阻变化。

2.2 高速接收模块

高速接收端是整个电路设计的核心,它是决定单通道接收最大数据率以及信号接收质量的关键模块。高速接收端将通道链路上的高速时钟/数据信号准确接收转换成单端信号,并输入到后续的数字电路中,因此对其增益、带宽、功耗以及共模信号电平接收范围都有较高要求,在设计过程中需要折衷考虑[7-9]。

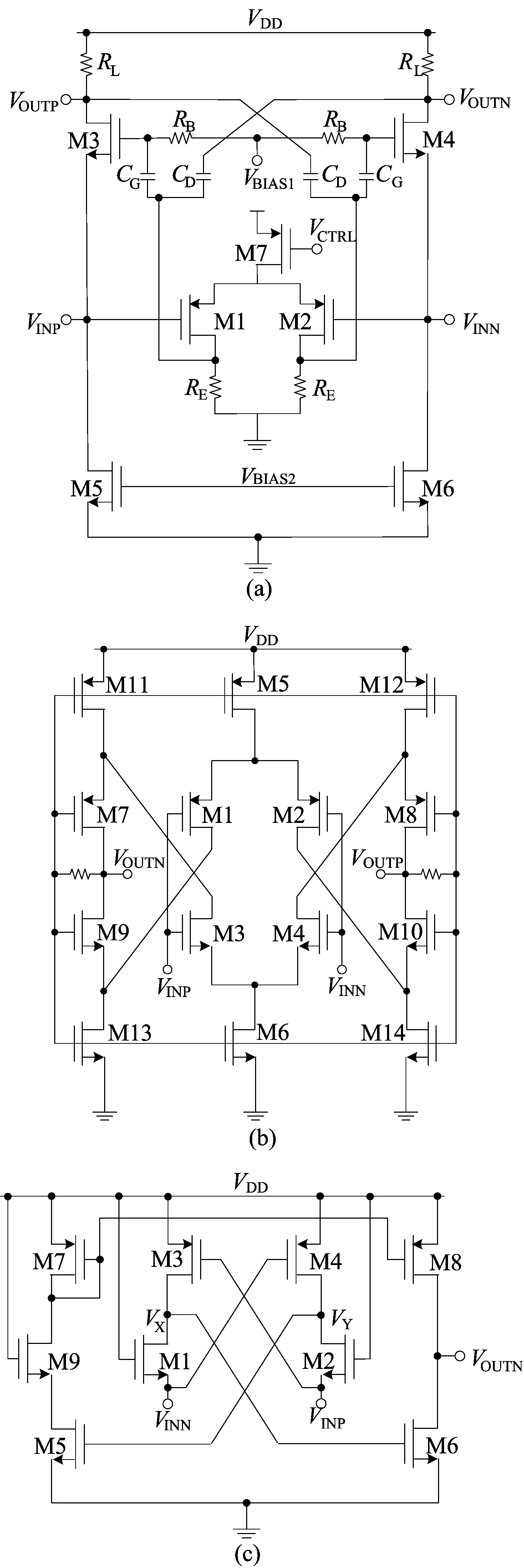

现有的几种高速接收端结构如图4所示。

图4 几种高速比较器结构

图4a是一种嵌入了连续时间线性均衡器(continuous-time linear equalizer, CTLE)的共栅极电平移位器 (common-gate level shifter, CGLS)[10],CTLE的加入使电路的电压增益以及带宽有一定的提升,通过M3、M4源端输入可以容纳200 mV以下更低的共模接收电压。图4b是一种超宽共模接收范围的差分放大器(very-wide-common mode differential amplifier,VCDA)[11], 轨对轨的输入形式具有广泛的共模接收范围,同时可以抑制共模输入电压ΔVCMRX以及差分输入ΔVOD的波动。但是这2种结构都需要加入额外的电路进行偏置,引起功耗的增加。为了进一步降低功耗,一种自偏置可扩展的低压差分信号接收端被提出来[12](图4c)。第1级运放由M1、M2的共栅极放大结构以及M3、M4的共源极结构组成。相较于前2种结构,信号由NMOS的源端进行输入,不受阈值电压Vth的影响,因此接收到的差分信号的共模电压更低,同时没有额外的偏置电路,进一步减小了功耗。但是由于共栅极M1、M2栅端电压由电源提供偏置电压,为维持M1、M2饱和区的状态电源电压不能太高,图4中使用1.2 V电源电压限制VX、VY点电压的提升,进而限制信号的转换速率。

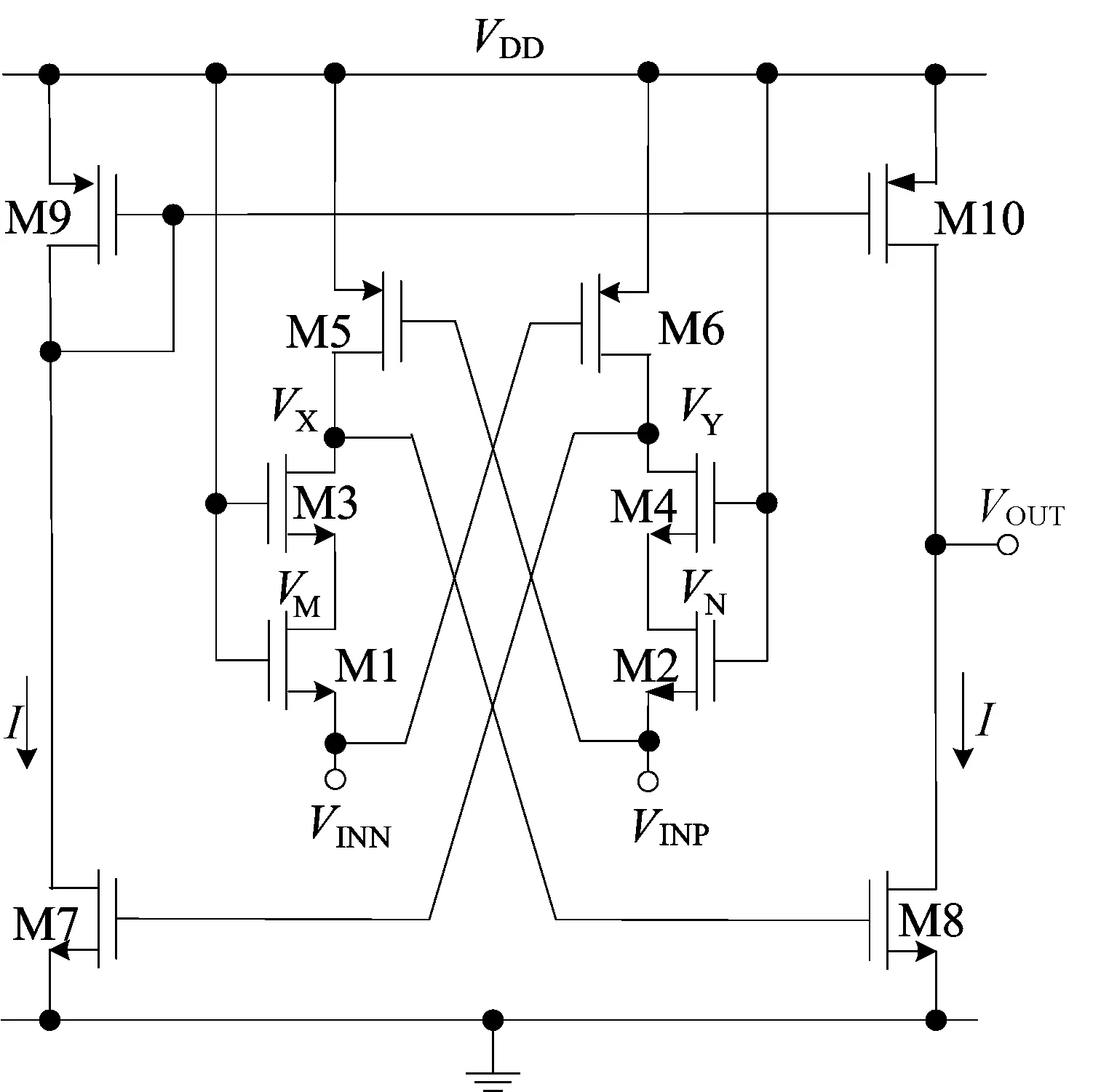

本文提出的一种接收速率达到2.5 Gb/s的高速接收电路如图5所示。第1级放大结构由M1、M2、M3、M4、M5、M6组成,其中:M3、M4作为共栅极放大器;M5、M6作为共源极放大器;均工作在饱和区;M1、M2工作在线性区。第2级放大结构由M7、M8、M9、M10组成,是一种电流源作负载的差分转单端信号放大结构。

图5 本文提出的高速比较器

采用1.8 V电压源供电,由于M3、M4共栅极的偏置电压由1.8 V电源提供,为维持M3、M4工作在饱和区状态,提升VX、VY点电压,本文采用分压MOS管M1、M2串联在M3、M4的源端。由于M1、M2的栅极开启电压为单端转差分模块输出的高电平电压,其值很高,且漏极电压VM、VN很低,因此在工作过程中M1、M2始终处于线性区,即等效于2个线性电阻的作用。M1、M2的主要作用如下:① 工作在线性区等效于线性电阻的作用,通过电阻分压的形式消耗一部分压降,使VM、VN以及VX、VY的电压提升,保证M3、M4工作在饱和区;②VX、VY点电压的提升导致输入到M7、M8栅极电压升高,根据饱和区电流公式流经M7、M8的电流增大,即M7、M8、M9、M10组成的第2级运放中电流增大,因此提升了数据的转换速率;③ 因为信号是由M1、M2的源极进行输入,所以需要考虑输入电阻的影响,M1、M2等效于电阻串联在电路中,因此会提升整个电路的输入电阻。

2.2.1 增益

在高速接收端工作过程中,M3、M4作为共栅极放大,M5、M6作为共源极放大,M1、M2等效为线性电阻。设M1的等效电阻为ro1,则VX、VY点的输出电阻ROUT为:

ROUT=gm3ro3ro1//ro5

(3)

因此第1级电压增益Av1为:

Av1=-(gm3+gm5)(gm3ro3ro1//ro5)

(4)

第2级电压增益Av2为:

Av2=-gm8(ro8//ro10)

(5)

其中,gm、ro分别为MOS管的跨导及内阻。总电压增益为:

Av=Av1Av2

(6)

2.2.2 输入电阻

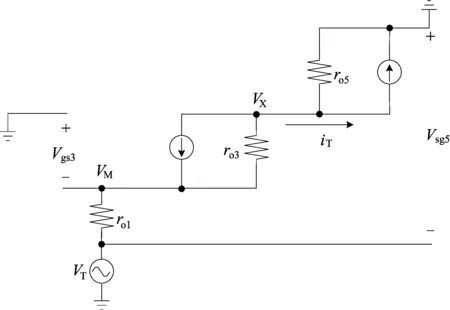

该结构由输入晶体管的源端进行信号输入,由于其输入电阻有限,总电阻是终端电阻与高速接收端输入电阻的并联结果。对输入电阻的小信号等效模型进行分析,如图6所示。

图6 半边电路的小信号模型

输入电阻可以由VT/IT表达式计算得出,即

Vsg5=-VT

(7)

Vgs3=iTro1-VT

(8)

iT=gm5Vsg5+VX/ro5

(9)

iT=-gm3Vgs3+(VT-iTro1-VX)/ro3

(10)

由此可以推算出输入电阻为:

(11)

经过上述计算,此结构的差分接收端的等效输入电阻可以达到几十千欧姆以上。

3 版图设计及仿真结果

电源模块和MIPI D-PHY整体版图如图7所示。图7包括电源模块、4个数据通道以及1个时钟通道。每个通道均包含高速发送端、高速接收端、低功耗发送端和低功耗接收端。总面积为1 500 μm×113 μm,其中高速接收端模块面积为54 μm×18 μm。

图7 电源模块及MIPI D-PHY的版图

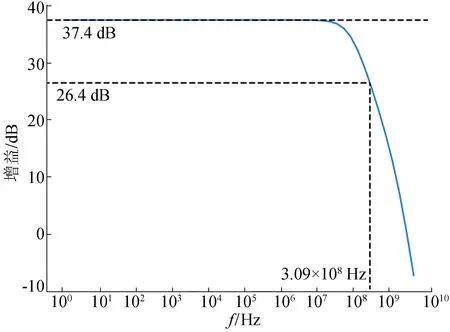

本文采用SMIC 0.18 μm的CMOS工艺设计、1.8 V电压供电。在完成高速接收端的版图后,对其进行参数提取及后仿真,本文设计的高速比较器增益带宽的仿真结果如图8所示。

图8 高速比较器增益带宽仿真结果

该比较器的低频增益为37.4 dB,-3 dB带宽为309 MHz,当数据率为2 Gb/s,即输入信号频率为1 GHz时,该比较器增益仍然可以达到15.5 dB。仿真结果表明,此结构的高速比较器满足增益带宽的设计要求。

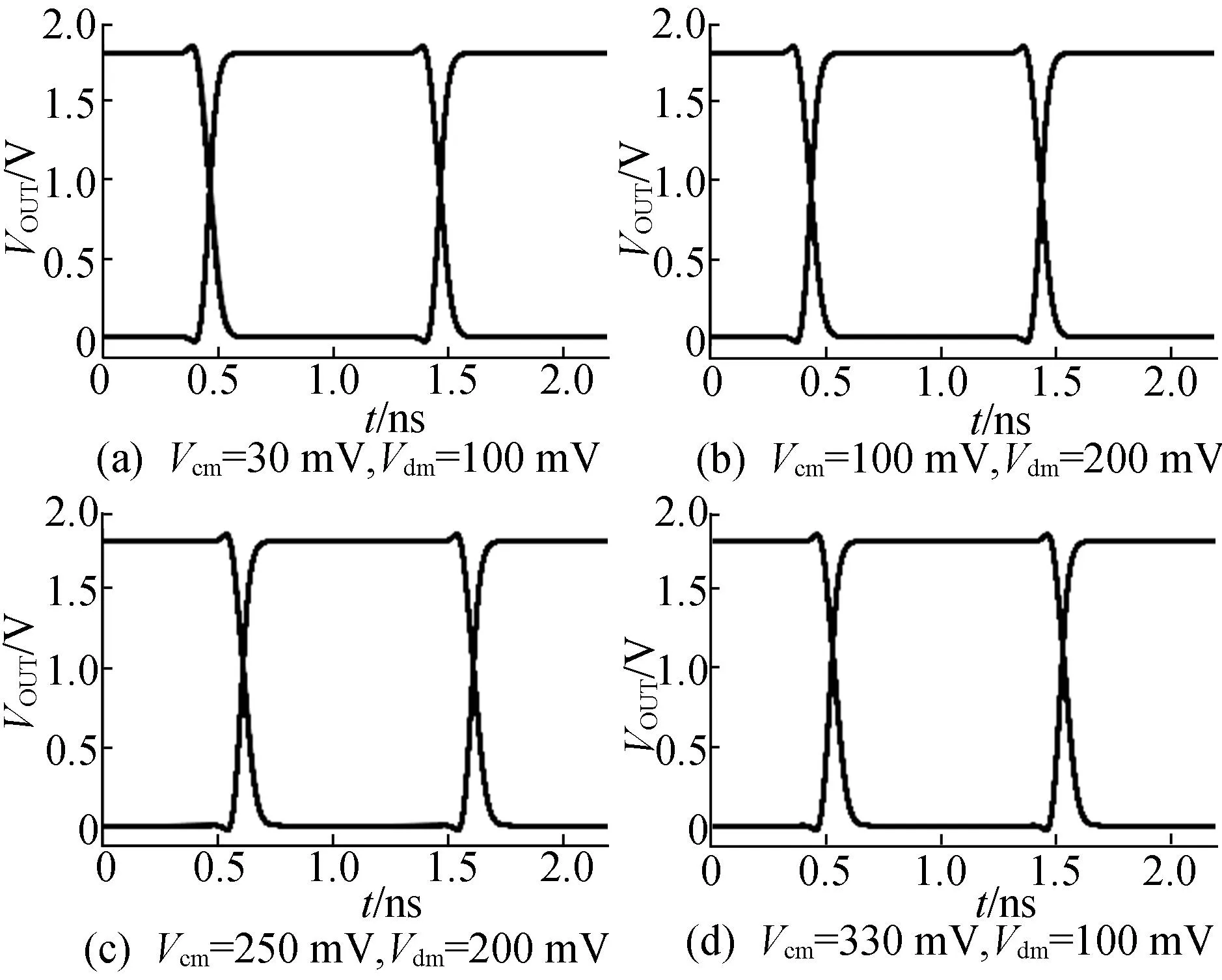

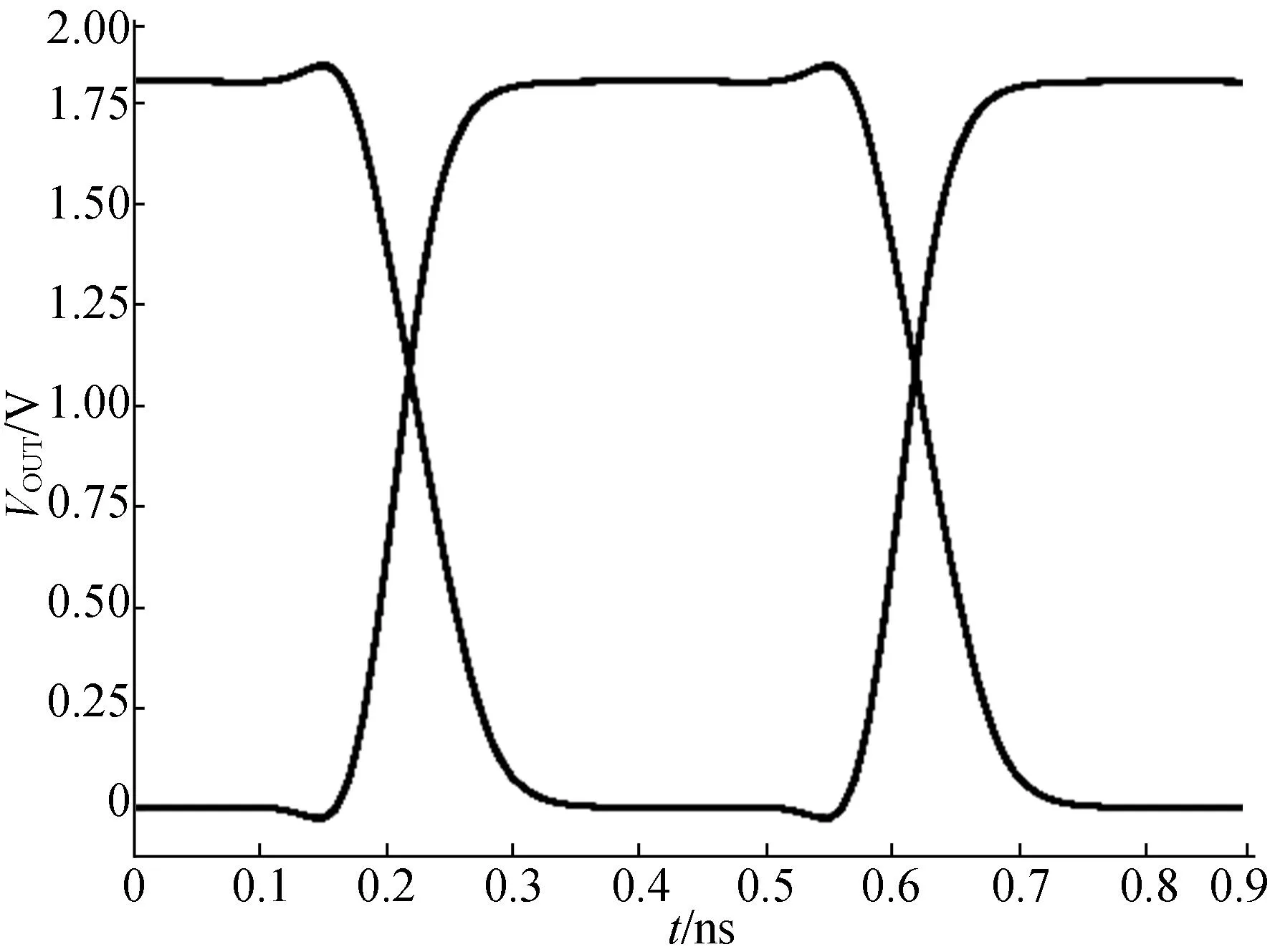

在1.0、2.5 Gb/s信号速率和不同的共模电压Vcm、差分电压Vdm下,高速接收端的后仿真眼图如图9、图10所示。

图9 10 Gb/s信号速率下高速接收端的后仿真眼图

图10 2.5 Gb/s信号速率、Vcm=200 mV、Vdm=200 mV下高速接收端的后仿真眼图

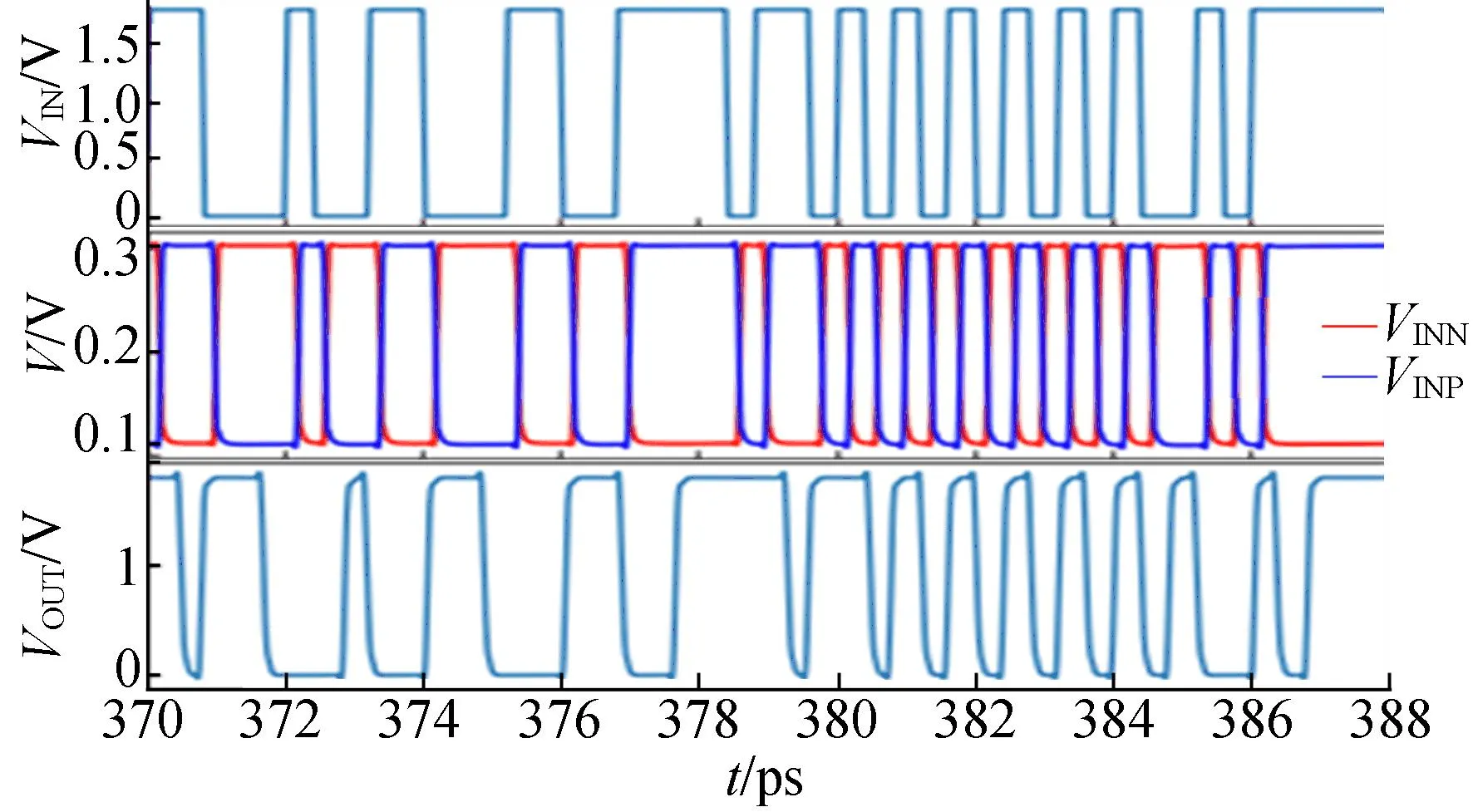

HS模式整体仿真结果如图11所示。图11中:第1行是输入到高速发送模块的信号,数据率为2.5 Gb/s;第2行是经过高速发送模块,输入到传输线上传输的差分信号,仿真结果显示其摆幅为117.7~300.0 mV;第3行是高速接收端输出的信号。本文提出的高速比较器输出信号眼图仿真如图12所示。

图11 HS模式整体仿真结果

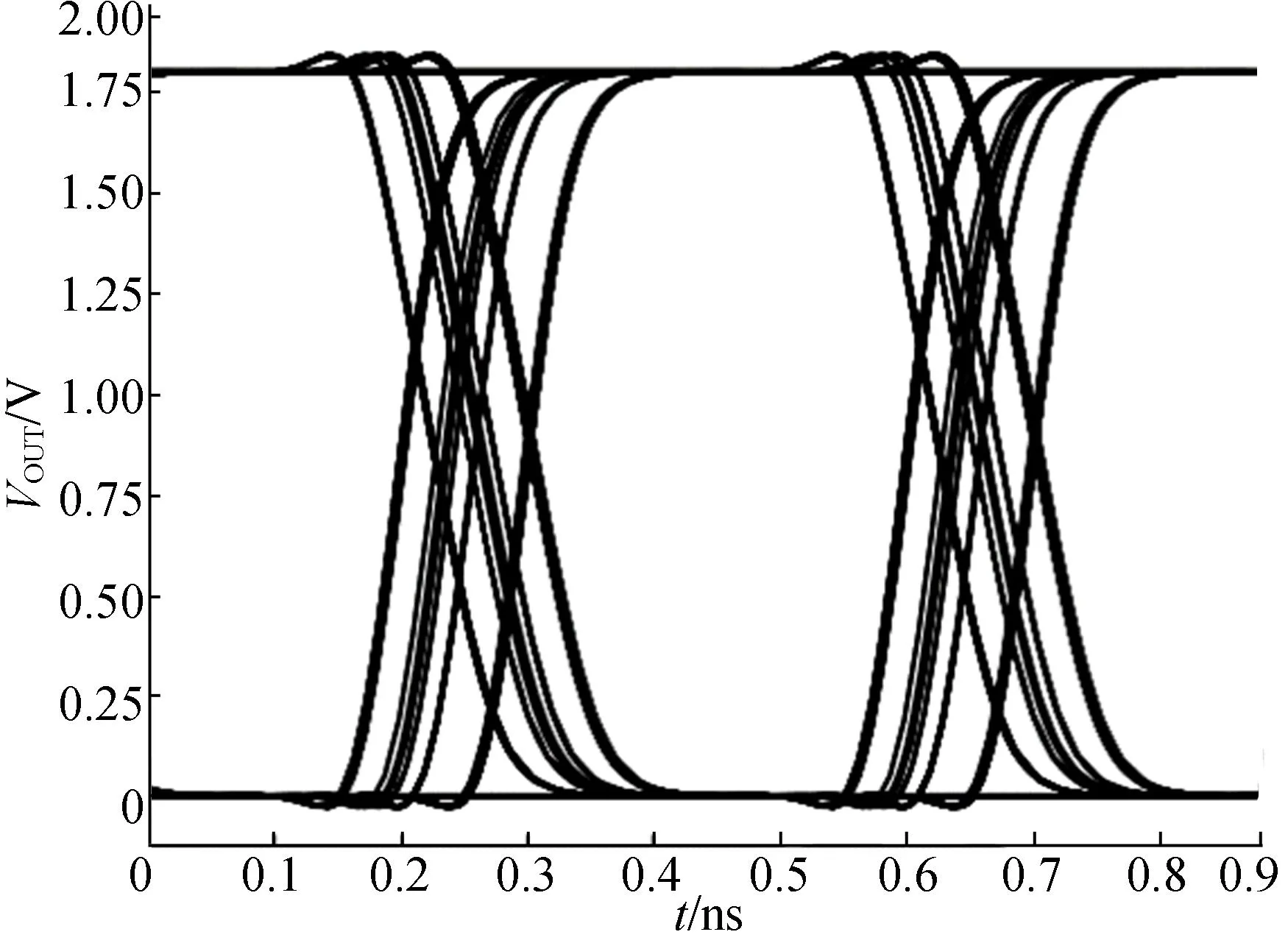

图12 本文提出的高速比较器输出信号眼图

从图12可以看出,在SMIC 0.18 μm的CMOS工艺、1.8 V电源电压下,此结构的高速比较器的接收速率可达2.5 Gb/s;传输线上差分信号的差模电压值为182.3 mV(协议规定在140~270 mV范围内),可见本文提出的高速比较器的有限输入电阻对接收到的差分信号线电平影响较小。在不同工艺角和温度条件下进行仿真,结果显示均满足设计要求。

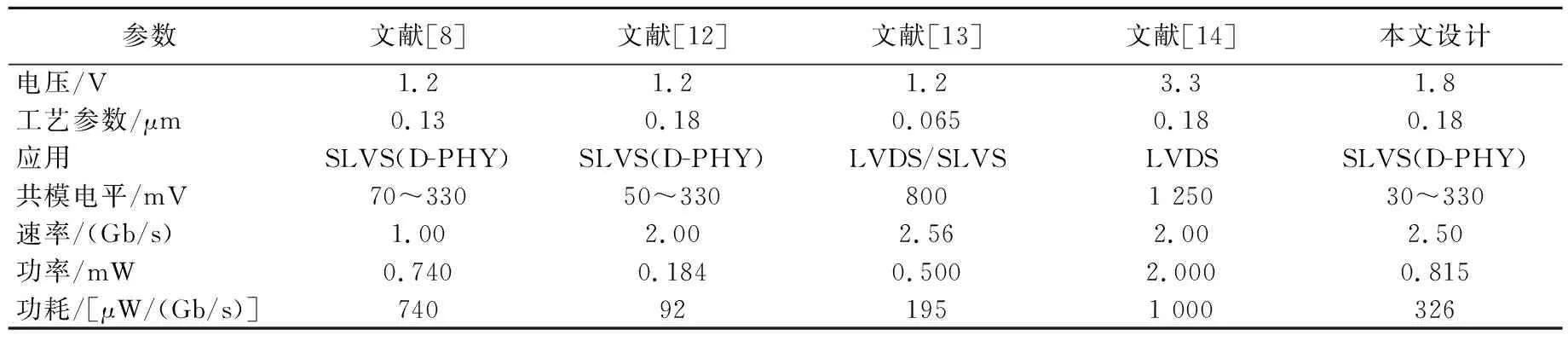

将本文提出的高速比较器与参考文献的进行对比,结果见表2所列。相较于传统高速比较器结构,本文提出的结构具有信号的共模电压接收范围更广、接收速率更高且功耗更低等优势。

表2 本文设计与参考文献的高速比较器对比

4 结 论

本文提出一种适用于MIPI接口电路高速接收模块的高速比较器,并对此电路结构进行理论分析与仿真设计。首先介绍MIPI D-PHY 物理层的整体电路功能结构以及高速、低功耗模式的电气特征;其次总结现有的几种高速比较器结构,并分析各个结构的优缺点;最后提出一种自偏置高速低功耗的高速比较器,分别对增益、输入电阻进行小信号模型分析,并完成了版图设计和后仿真。

本文基于SMIC 0.18 μm CMOS工艺对提出的高速比较器进行电路和版图设计,完成后仿真验证。仿真结果表明:在1.8 V的供电电压下,在不同仿真工艺及温度条件下传输速率均可达到2.5 Gb/s,共模电平接收范围可达30~330 mV,功耗为326 μW/(Gb/s)。与传统的结构相比,在提升传输速率的同时进一步减小了功耗,并提升了共模电压的接收范围。