基于JTAG 接口的多通道测试系统设计

2024-03-20杨井胜

杨井胜

(中国电子科技集团公司第三十八研究所,安徽 合肥 230031)

0 引言

随着雷达技术的发展和软件无线电技术的规模化应用,接收数字化越来越向前端推移。随着射频高速采样、千兆数字上下变频等技术的实现,数字化测试已成为电子装备性能评估的重要基础技术之一。为了实现数字接收电路的自动采集与运算,通常采用增加硬件接口电路,对数字IQ 数据进行预处理,经网口传输到计算机系统内分析;或通过以嵌入式计算机为核心的数据采集系统来实现;由于外部电路的增加,不便于外场携带和测试,不可避免地增加了测试系统的开发难度和信号传输处理的损失,可能还会导致数据同步解调异常和信噪比的恶化等[1],给被测试通路的测试带来一些不确定性。本文采用直接采样的方式,利用电路自身的JTAG链路,硬件接口简单,最大限度地保证了数字IQ 信号原始特征,避免因电路增加带来的采样与分析的复杂性,通过嵌入式MATLAB 算法的采集和传输,实现Lab-VIEW 的数字化分析与运算,测试结果显示更加直观,保证了系统验证的高效性和准确性[2]。

1 设计实现

1.1 系统总体设计

系统从3 个方面进行设计,一是接收电路的内部逻辑固件设计,二是嵌入式MATLAB 程序设计,三是Lab-VIEW 自动采集控制系统的设计。具体功能实现框图如图1 所示。

图1 逻辑功能框图

系统通过SignalTap 数据交互功能,完成FPGA 内部数据的格式化输出[3];通过嵌入式MATLAB 算法,完成数字信号的极坐标数据格式封装和处理[4],随后传送到LabVIEW 测试系统模块,通过相应运算、处理和分析,实现各项性能指标的结果显示和输出,完成实时的在线自动测试[5]。

1.2 逻辑固件的设计实现

数字接收机输出是量化、采集和滤波处理后的IQ 数据,性能指标的符合性验证,全部基于正交(Qn)和同相(In)数据的采集、解析和运算后的结果[6]。

SignalTap 与外部逻辑分析仪功能类似,能够捕获或显示编程芯片系统设计中实时信号的状态,采样深度高达128 kB,最多支持1 024 个通道,支持多级触发输入输出。

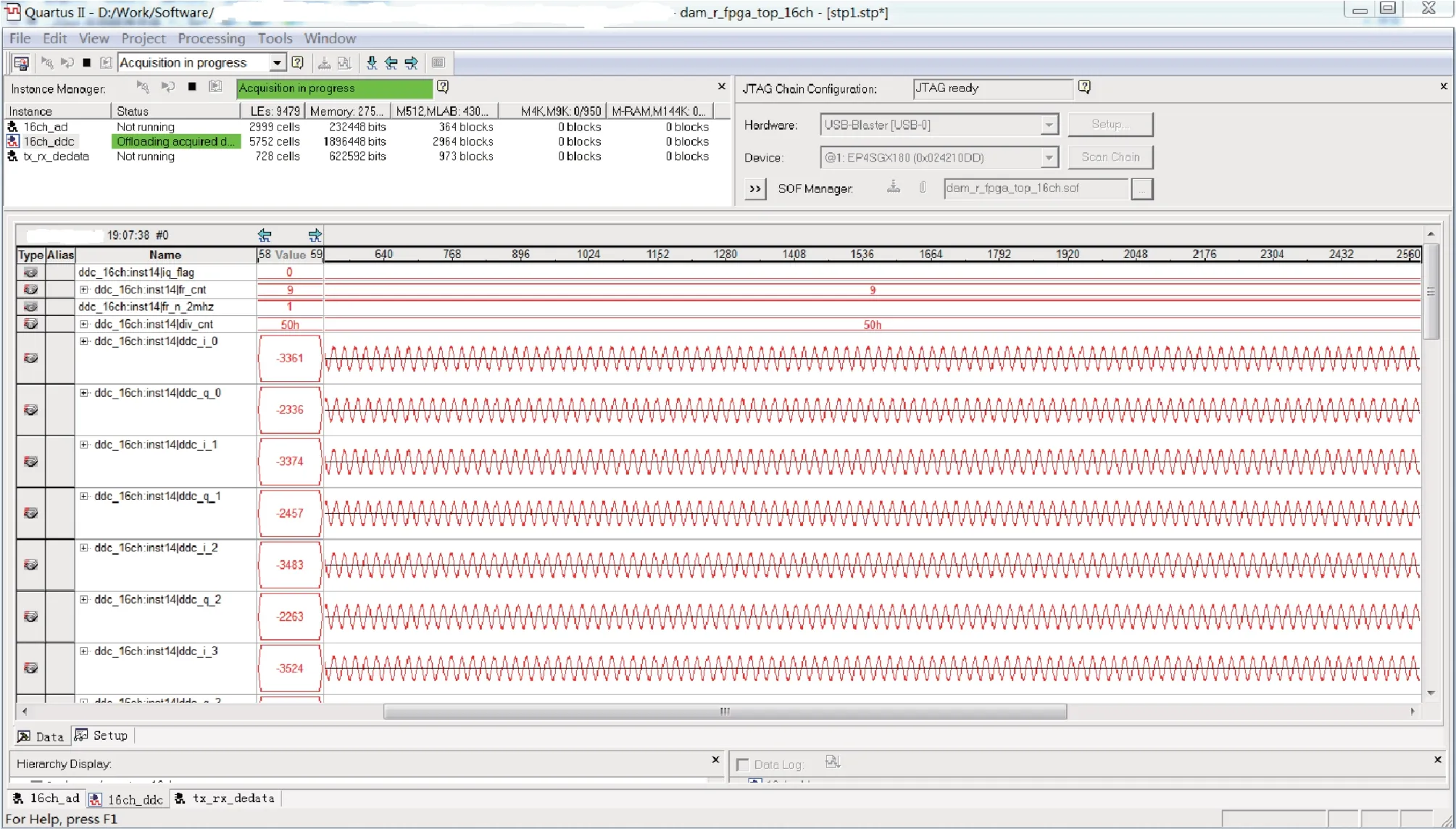

电路的逻辑固件设计,需要通过端口进行选择性定义,将AD 采样处理后的IQ 数字数据,利用Quartus 软件的SignalTap 功能,实现逻辑电路内部测试点(数据位)的嵌入式逻辑分析,SignalTap 利用 JTAG 边界扫描的方法读取FPGA 内部节点的值,然后送达到Buffer(缓冲器),再由JTAG 链路把数据送到Quartus 下的SignalTap模块。数据可以输出.stp 格式的文件,数据即为FPGA内定义输出的数据[7],如图2 所示,可以规范灵活地定义输出数据,图中IQ 数据从第5 行开始,MATLAB 节点控制模块,依据约定的协议格式进行格式化读取和解析。

图2 逻辑固件采样示意图

内部逻辑固件设计时,需要将被测试数据进行合理的模块封装,尽量减少资源占有量,保证被检测数据的完整性。SignalTap 设置的数据节点,除了所有输出IQ数据的节点外,还需要包含时钟、触发和同步节点,主要用于数据的同步触发和实时监测。关键定义如下。

一是设置采样时钟,采样时钟决定显示信号波形的分辨率以及后续解调的时钟频率。根据AD 电路设计需要,多数情况下采用射频直接带通采样,涉及数据的传输率,系统对等效基带谱进行整数倍抽取,在对各种调制信号进行解调时,保持与实际传输数据率一致,需要全部与SignalTap 模块设置相应的时钟进行关联[8]。

二是保证后续测试系统的实时显示,设置缓冲区存储模式为连续存储模式。为了保证后续测试的需要,需要将采样深度设置尽量足够大。考虑所能显示的被测信号波形的时间长度为Tx,具体显示参考如下:

其中,N为缓存中存储的采样点数,至少保证1 024 点以上[9],既保证数据的准确度,又能减少计算量;Ts为采样时钟的周期。

三是设置同步触发的条件,正常采用时钟上沿作为触发条件,特别注意设计前后的数据格式,采样与MATLAB 内数据定义格式完整统一。

1.3 MATLAB 程序的设计实现

为实现硬件系统的数据与后续LabVIEW 测试系统的交互分析,数据需要通过“桥梁”实现数据的传送,最终实现测试数据分解和运算[10]。

MATLAB 程序设计的核心是完成对.stp 数据进行嵌入式读取,并进行格式化的封装和输出,完成LabVIEW与硬件逻辑电路之间的数据转接和交换,为后续Lab-VIEW 的数据处理分析提供输入输出的接口。

根据后端数据的需求,对SignalTab 数据节点的数据进行逐一读取,读取的方法是将对应名称和对应行数进行循环调入,采集分析的时钟频率要与发送端定义统一,参数要与Quartus 内的SignalTap 设置一致,否则将无法实现后续数据分解和显示。

1.4 基于LabVIEW 的实现

基于LabVIEW 的测试系统,是对数字信号进行分析和运算的部分,下面将对LabVIEW 内关键的设计和性能指标的处理过程进行分析。

1.4.1 接口设计

通过在LabVIEW 中MATLAB 程序调用,实时采集分析来自JTAG 链的IQ 信息,具体包括:

(1)多通路的控制与采集。该部分设计与SignalTab 内的采集控制点相关联,采用For 循环+选择结构,实现不同通路的测试设置。为保证测试系统的可扩展性和通用性,以及数据传输、解析和处理的一致性,将各部分需要关联的数据和变量,进行统一的定义设置,包括SignalTap 时钟、MATLAB 采集分解时钟以及Lab-VIEW 自动测试系统分析采样时钟等,通过统一关联变量来实现数据的同步。

(2)嵌入式MATLAB 节点的设计。由于测试数据内包含I 和Q 两路数据,数据通过嵌入式MATLAB 节点设计,MATLAB 程序对原始数据进行再封装,数据节点(IQ 数据)被送入 LabVIEW 的测试节点上,进入数据分析模块[10]。

(3)模块的标准化分析和处理。通过IQ 信号的标准接口和标准数据分析模块,能够兼容多型雷达采样,实现测试接口的模块化和标准化,具有较好的可移植性。

1.4.2 数字分析与处理

(1)分析处理过程

经数字下变频、正交解调、高效数字滤波CIC 滤波后,处理完成的数据转入信号处理流程。模拟信号处理前的极坐标表示的复信号z(t)如下:

其中,a(t)表示z(t)的瞬时包络,φ(t)=ω0t+θ(t)表示信号的瞬时相位,ω(t)==ω0+θ(t)表示信号的瞬时角频率,这3 个特征量包含了窄带信号的全部信息,去除载频分量后,基带信号(或称为零中频信号)可表示如下:

式中,基带信号的同相分量zBI(t) 和正交分量zBQ(t),基带信号为解析信号的复包络,含有正频分量和负频分量。通过对上述信号的分析,从而实现通道性能指标的分析。

式中,Re[.]、Im[.]分别表示实部和虚部。

信息内包含瞬时幅度、瞬时相位和瞬时频率,通过对基带信号的3 个特征参数的分解运算,实现信号分析、参数测量和识别解调[11]。

测试系统将信号从数字域转换到模拟域,需要获取信号的频谱信息,FFT 运算是获取频谱信息的重要步骤,为了防止信号分析的泄露等影响,需要增加滤波窗函数(汉宁窗、海明窗、高斯窗、三角窗)。

通过FFT 计算DFT,得到信号的离散频谱,再经过平方运算获得功率谱[12]。

系统内的IQ 数据,根据不同的性能指标要求,依据不同的测试需求,设计通用化模块化的VI 模块,内部处理的原理框图如图3 所示。

图3 测试系统内部处理框图

(2)增益分析

所谓增益分析,即通过基准线性输入功率的情况下,采集每个数字接收通路的输出幅度,是验证通路好坏的指标之一,也是确认每路输出幅度一致性的衡量因素。

通过JTAG 链路采集到的数字IQ 信号的数据,准确运算出通路幅度一致性的指标,具体处理过程为:先将量化后的数据送入嵌入式MATLAB 程序中,通过MATLAB 程序构建复数数组,IQ 复数数组传送至Lab-VIEW 中进行转换,对采样深度内的数据进行平均,根据模值运算出有效值,通过幅度有效值进行多次采集取平均,然后运算出相应的输出功率。

首先进行极坐标转换,分析处理过程如下:

式中,V是电压有效值;ZBI和ZBQ为IQ 信号的幅值;P为输出功率;R为输入阻抗,标准有效值50 Ω。

(3)信噪比分析

接收信噪比(SNR)是指接收通道的信号功率与噪声功率的比值,是接收系统工作性能指标的体现,也是保证接收机灵敏度的重要衡量因素。

信号功率和噪声功率是测试系统需要分析的重要参数,为了保证测试系统的通用性和扩展性,测试系统增加了硬件选择匹配模块,依据针对不同型号AD 硬件电路的满幅度值,选择不同的分析处理参数,并对信号滤波进行多窗口设计,进行FFT 运算后,满足不同数据格式的匹配测试需求[13]。

信号的有效功率值(Ps)采用FFT 运算,通过窗口选取,对整个频谱采集范围内的信号主谱信号进行分析,累积加权后,得出信号的输出幅度。

输出功率值(Pn),通过窗口选取,对整个频谱采集范围内的噪声谱信号进行分析,累积加权后,得出噪声信号的输出幅度,分析结果如下:

通过信噪比运算,运算出信噪比的值。

(4)镜像抑制的分析

数据从Q 数组实部数据的组数确定,采样频率是由整体关联变量决定。通过数字信号分析,经过FFT 运算和累积加权后,分析出主谱信号功率Ps。

通过主谱频率的分析,然后累积加权出镜像频率的功率Pi。分析结果如下:

通过镜像抑制分析I,运算得出相应的指标[14]。

2 实际应用情况

2.1 实际应用范围

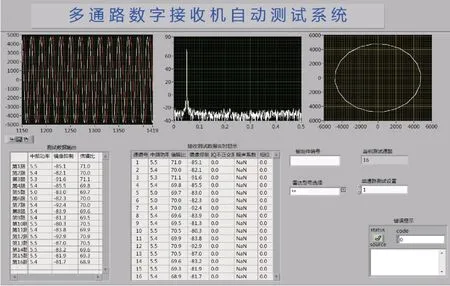

根据不同的测试需求,综合考虑实际测试的应用场景,系统具有自定义单通道测试和多通道全自动测试的功能。基于数字化接收通路的全自动采集与测试,对数字处理后的数据进行转换处理,通过图形化的显示设计,使得信号的观测更加清晰和直观,包括时域的模拟IQ 显示,频域的信号显示,正交的图形显示等。16 路数字接收通道的测试数据如图4 所示。

图4 测试系统界面

具有兼容多型号、多模式的应用场景,内部预留其他性能指标分析的接口,如噪声系数分析等,具备实现通用化测试的接口能力。

通过IQ 显示窗口,可以清晰地观测到模拟IQ 信号的情况;通过频谱显示窗口,能够清楚地反映采集频率带宽内的信号质量;通过正交图形显示窗口,能够直观地观测到IQ 信号相位的正交度和稳定性。

2.2 数据的可信度分析

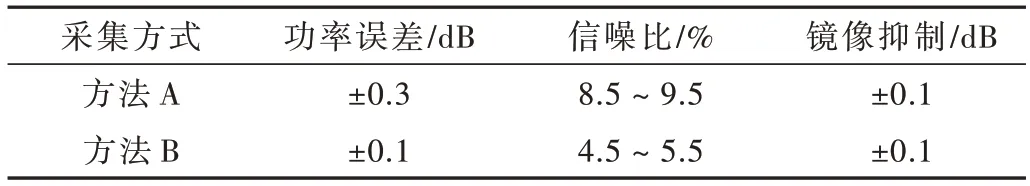

为了保证测试数据的准确性,对测量过程的误差进行了修正,涉及数字电路自身的随机误差、电缆传输等引入的系统误差等,依据同一参考信号输入与MATLAB联合采样分析,验证采样运算数据,进行相应的误差修正[15]。以下对两种不同的方法进行对比分析,其中,增加硬件采集接口(简称方法A),JTAG 链路直接采集(简称方法B),结果见表1。

表1 不同采集方式测试误差对比表

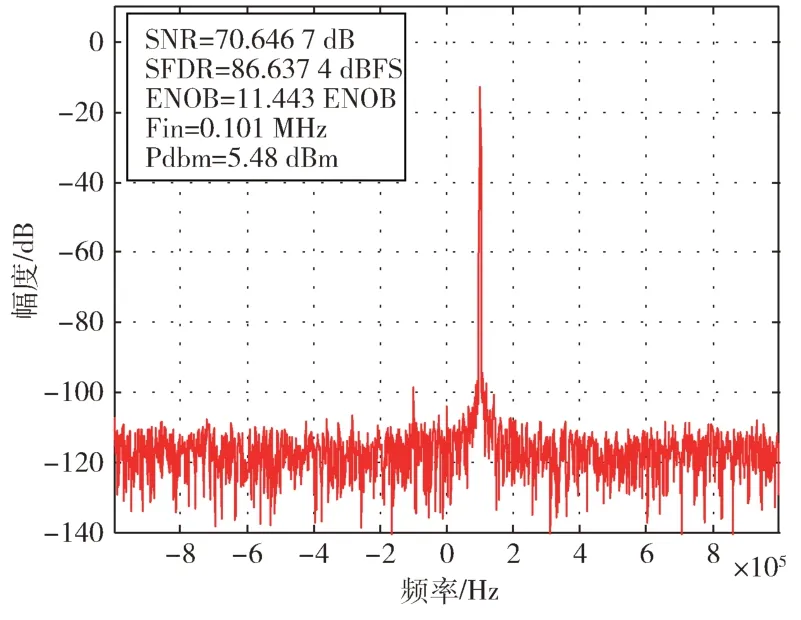

通过对比分析,以方法A 实现的功率损失范围和引入的噪声随机误差都会增加,针对多个样本的多次采集(如图5 所示),基于JTAG 方式实现的自动测试,误差情况综合分析如下:中频功率指标的随机误差范围是±0.1 dB,信噪比指标的随机误差范围是5%(噪声功率采集的随机误差特性影响±0.5 dB),镜像抑制随机误差范围±0.1 dB。

图5 MATLAB 采样分析数值(第1 路)

2.3 自动测试的优势分析

通过联合分析与自动测试运算,优势主要体现如下:

(1)测试通路的自动化切换和自定义采集,测试应用更加高效智能。

(2)测试数据的自动化记录,报表的格式化输出,使得数据处理效率明显提升。

(3)数据的动态实时显示,提供更加直观的监测窗口,为后续数据存储与分析,以及基础数据库构建提供了保证。

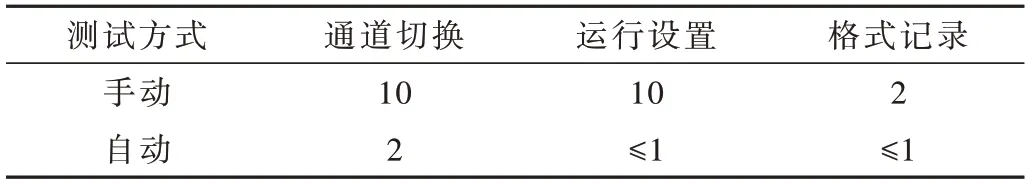

不同测试方式效率对比如表2 所示。

表2 不同测试方式测试效率对比表(s/路)

通过实际应用和外场测试验证,以16 通道数字收发组件为例,手动测试需要352 s,自动测试需要64 s,测试效率提升5 倍以上。

3 结论

本文涉及的解决方案,提出通过JTAG 链路接口采集,联合MATLAB 和LabVIEW 设 计,解决了IQ 数字 信号的便捷化采集与分析,系统创新性地提出基于模块化的数据分析,具备多型数字化接收机的兼容性扩展,通过内部不同参数的配置,完成多种型号雷达的通用化多通路的自动采集与分析,提升了外场测试的检测效率,为同类测试应用提供了较好借鉴和参考。