基于ARM 和FPGA 的数字多道分析器研制

2024-03-14武旭东麻金龙段金松李婷王玮

武旭东,麻金龙,段金松,李婷,王玮

核工业北京地质研究院,北京 100029

在核能谱探测中,常通过脉冲幅度分析技术获取能谱信息,多道脉冲幅度分析器作为实现该技术的主要工具,其性能的优劣直接决定核素分析的准确性。传统的脉冲分析器多采用模拟器件实现,脉冲信号从探头输出后,分别经过放大、高斯成形、极零相消和峰值保持等处理过程。大量模拟器件的使用,使得电路变得复杂,更容易受到各种因素的影响,使得系统的稳定性变差。

随着核能谱测量学在各个领域越来越多的应用,对多道脉冲幅度分析器的各项性能指标(如:速度、精度、稳定性和功耗等)提出了更高的要求,模拟多道越来难以适应时代的需求[1-3]。与此同时,模数转换器(Analog-to-Digital Converter,简称ADC)和数字信号处理技术出现了很大进步,这为多道脉冲幅度分析器从模拟转向数字提供了硬件基础。本文以ADC 和现场可编程门阵列(Filed Programmable Gate Arrays,简称FPGA)作为核脉冲信号处理核心,设计了一款以ARM 微控制器[2]为主控制单元,使用串行外设接口(Serial Peripheral Interface,简称SPI)、高速并行接口和串行总线(Universal Serial Bus,简称USB)接口作为多道与上位机通信的桥梁,实现集核信号采集、数据传输为一体的高速数字多道分析器。

1 系统整体设计方案

数字多道分析器整体设计方案如图1 所示,γ探测器将采集到的核脉冲模拟信号送至信号调理电路,经调理转换的差分信号送入ADC 进行模数转换。得到的数字核脉冲序列送至FPGA 中,经数字滤波、幅度提取、堆积判别和基线修正[4]等一系列处理之后,按照提取的幅值大小在事前划分好的道址中相应增加计数,最终形成能谱数据。能谱数据由SPI 传输至微控制器,再由USB 接口上传至上位机软件。

图1 系统总体设计框图Fig.1 Overall system design block diagram

2 硬件电路设计

2.1 高速ADC 硬件设计

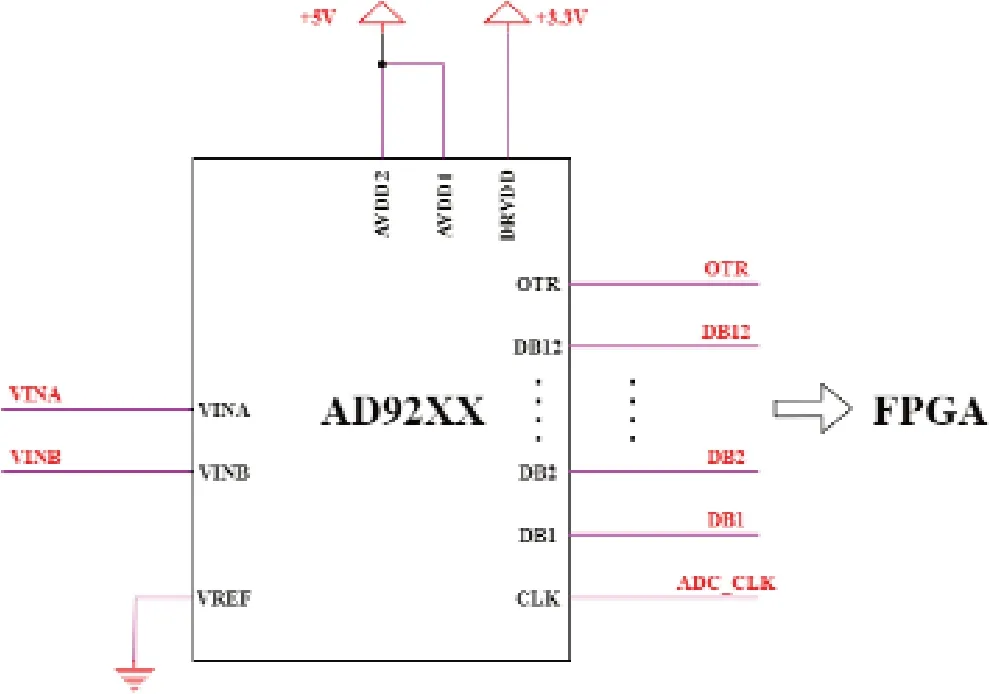

设计考虑到转换精度、速度和功耗等因素,选用Analog Device 公司的AD92xx 系列12 位、40MSPS芯片为高速模数转换芯片,采用+5V供电,内置一个高性能采样保持放大器和基准电压源,支持差分输入和单端输入。为了提高抗干扰性能,抑制共模噪声,设计输入信号采用差分输入方式[5]。ADC 电路原理如图2 所示。

图2 ADC 电路设计原理图Fig. 2 ADC circuit design schematic

图2 中数字输出电源DRVDD 采用+3.3V 供电,目的是实现与FPGA 的电平匹配。模拟输入信号经差分运放电路后由VINA 和VINB 输入,经模数转换后通过DB1 至DB12 数字量输出至FPGA,OTR 为数据超出量程范围标志位,用于FPGA 进行数据过滤。

设计中,ADC 的时钟信号ADC_CLK 由 FPGA提供,这样既能够实现FPGA和ADC的时钟完全同步,也能够保证ADC时钟的高速度、高稳定性。

2.2 ARM 主控单元硬件设计

设计的ARM 处理器选择STM32F4 系列控制器作为主控芯片。该芯片采用了32 位的Cortex-M4 作为核心,内置高速存储器(包含1MB FLASH 和192KB SRAM),其工作频率高达168 MHz。STM32 外围电路主要包括电源控制电路、RTC 时钟电路、蜂鸣器电路、存储器电路、SPI 通信电路和USB 通信电路[6]等,电路功能原理图如图3 所示。

图3 主控电路功能原理图Fig. 3 Schematic diagram of main control circuit functional

3 软件程序设计

3.1 FPGA 算法设计

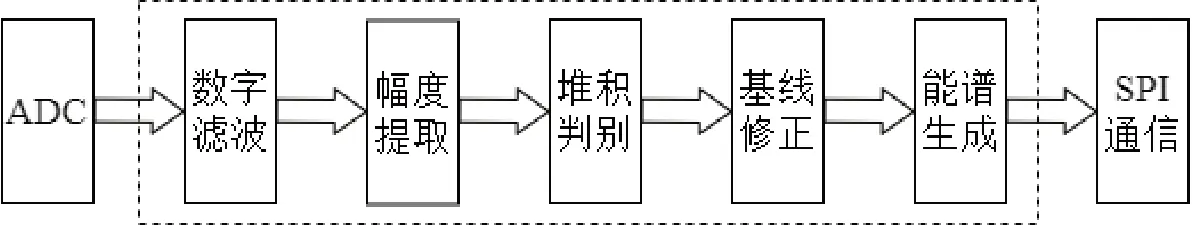

FPGA 具备高速并行运算、逻辑实现能力强和设计灵活性好等特点,并能够实时运算得到输出结果。γ脉冲信号数字处理算法是整个基于FPGA 的数字多道脉冲幅度分析器的设计核心,包括数字滤波、幅度提取、堆积判别、基线修正和能谱生成等模块[7]。启动能谱采集时,测量任务通过使能信号通知FPGA 启动信号采集。FPGA 首先将ADC 采集到的脉冲经过数字滤波处理,去除毛刺,滤掉部分基线干扰,然后进行幅度提取、堆积判别和基线修正处理,将提取到的信息生成能谱,存储到双口RAM 并发送到ARM 单片机中。FPGA 数据处理流程图如图4 所示。

图4 FPGA 数据流程图Fig.4 FPGA data flow diagram

3.1.1 数字滤波算法设计

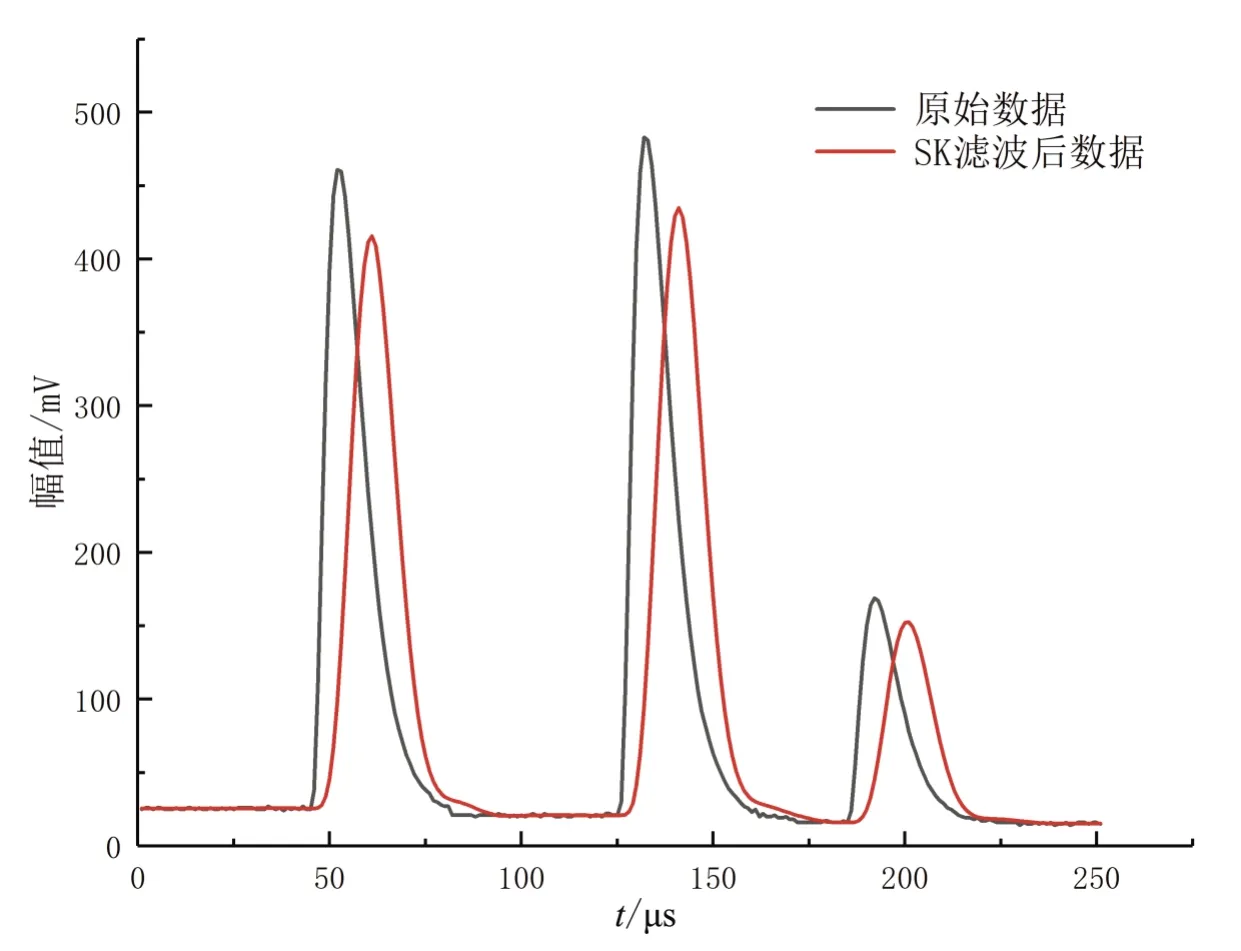

ADC 芯片在对脉冲信号进行采集的过程中,由于噪声干扰,使脉冲信号产生毛刺,所以在对数据进行提取之前要先滤波处理。本设计采用S-K 算法实现数字滤波,并将脉冲信号转换为“类高斯”信号。

根据S-K 滤波电路原理[8-9]推导出的S-K递推见公式(1)~(3)。

式(1)~(3)中:k—成形算法参数;x0—输入信号脉冲幅值;y0—第1 次迭代输出脉冲幅值;y1—第2 次迭代输出脉冲幅值;yn—第n+1 次迭代输出脉冲幅值;yn-1—第n次迭代输出脉冲幅值;yn-2—第n-1 次迭代输出脉冲幅值。

通过调整不同k值,可以优化和调节“类高斯”波形。由于k为定值,令则上述公式变换为:

利用SD 编码可将上述公式转化为移位的加减法运算,在FPGA 中通过VerilogHDL 语言编写代码实现,在节省大量FPGA 逻辑资源同时,还能保证高速采样的实时性。S-K 滤波前后的脉冲波形图如图5 所示。

图5 S-K 数字滤波前后波形对比图Fig. 5 Comparison of waveforms before and after S-K digital filtering

3.1.2 幅度提取算法设计

经过滤波成形后,脉冲信号的最大值与脉冲电压幅度的最大值是对应的。设计的幅度提取模块是通过一阶导数法来实现的。对于离散数据而言,一阶导数可通过计算一阶差分得到,见公式(5)。

式(5)中:S'i—第i点的一阶差分数据;Si+1—第i+1 点滤波成形后的脉冲数据;Si-1—第i-1 点滤波成形后的脉冲数据。

当一阶差分相邻2 个点S'i和S'i+1的数据中出现符号变化时,说明出现了脉冲信号峰值。将一阶差分数据用成形后的脉冲数据表示,则需要对Si-1、Si、Si+1和Si+24 个点的数据进行比较。离散数据的符号变化包含以下3 种情况:1)从-1 变为0;2)从0 变为1;3)从-1 变为1。通过VerilogHDL 语言编写FPGA 程序,判断是否满足以上3 种情况,即可实现脉冲幅度提取。

3.1.3 堆积判别算法设计

由于核脉冲信号的随机性,在采集过程中,在高计数率的情况下会出现脉冲堆积的现象。这种现象对能量分辨率具有较大影响。由于本设计采用数字多道技术实现,因此脉冲堆积识别的主要方法是时间差值比较法。该方法基于相邻脉冲之间的时间间隔大小,快速辨别是否发生脉冲堆积,降低脉冲堆积对能量分辨率的影响。

由于ADC 模块的采样频率为20 MHz,故相邻2 个采样点的时间间隔为50 ns。本设计判别算法如下:

经过滤波成形后的“类高斯”脉冲上升沿的时间约为0.8 µs,下降沿的时间约为1 µs,整个脉冲的时间约为2 µs,共40 个点。根据高斯函数的公式,对滤波成形后的脉冲数据进行数据拟合,得到脉冲的“半高宽”约为15 个点,即0.75 µs,见图6。试验表明,当相邻峰的距离大于2 倍的“半高宽”时,能够在不影响基线修正的条件下准确地识别峰位。若相邻峰的时间间隔小于2 倍“半高宽”,则认为发生了脉冲堆积,需要丢弃后一个脉冲计数,并根据实际时间间隔计算死时间,进行计数率修正。

图6 脉冲信号“半高宽”间隔Fig. 6 “Half width” interval of pulse signal

3.1.4 基线修正算法设计

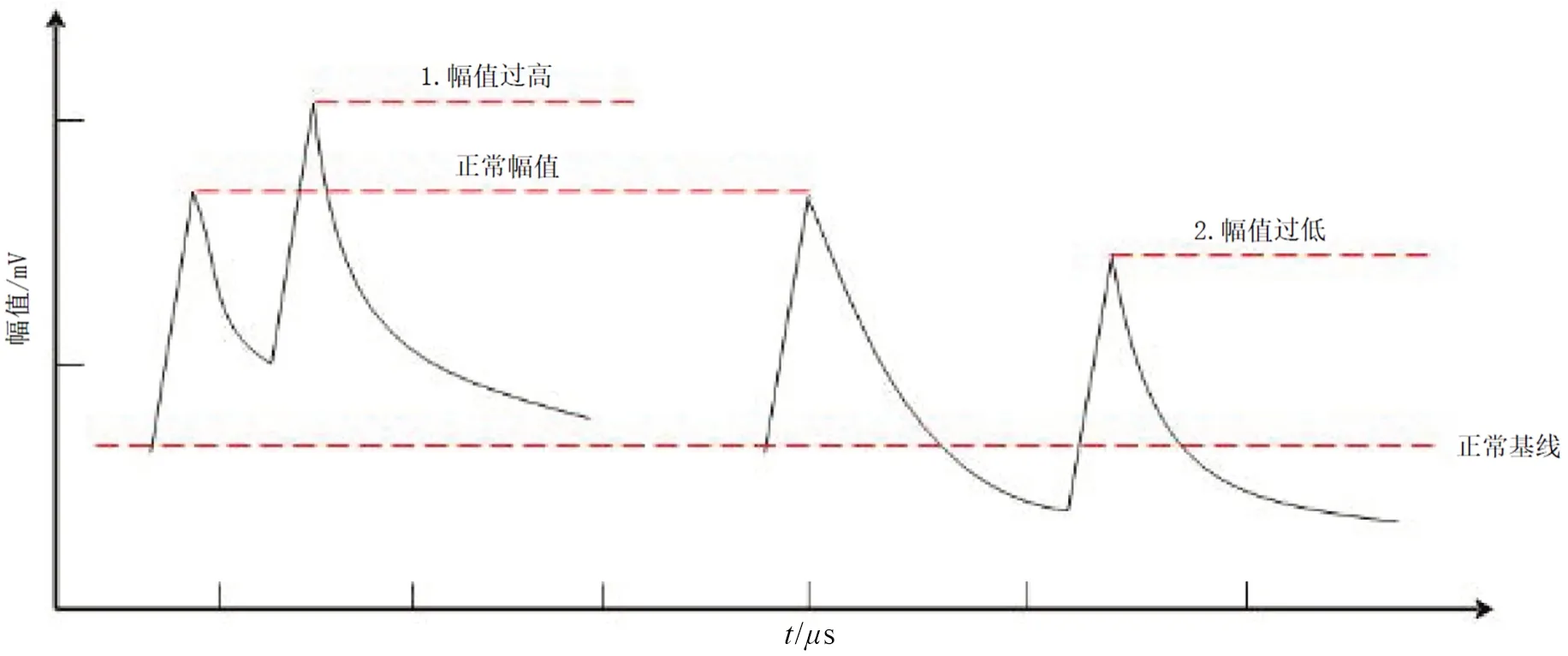

在数字化多道脉冲分析器中,由于基线偏移,从而导致脉冲幅值的提取受到影响。基线偏移的主要来源是运放电路幅度过载或脉冲堆积的存在[11],图7 为典型的基线偏移示意图。

图7 典型基线偏移示意图Fig. 7 Schematic diagram of typical baseline drift

设计采用最小平均结合固定基线的方法进行基线修正。最小平均法处理过程如下:首先取得连续N个脉冲采样值,并找到最小值Lmin,重复以上过程M次,得到M个最小值,求出M个最小值的平均值作为基线预估值[10-12],见公式(6)。

式(6)中:Laver—基线预估值,mV ;M—重复采集次数;Lmin—脉冲采样最小值,mV ;N—脉冲采样个数;i—求和变量。

为了保证每次都能够得到采样最小值,则N 的取值必须大于相邻脉冲间的宽度所对应的点个数。Laver与设计的基线阈值Lth做比较,从而得到最终基线估计值。

式(7)中:L—修正后基线,mV;Lth—下阈值,mV。

将幅度提取之后的有效峰值减去此基线估计值,从而得到真实幅度值计入能谱相应的道址。

3.2 控制程序设计

3.2.1 主控系统设计

主控单元是通过移植嵌入式实时操作系统FreeRTOS 实现的。FreeRTOS 是一个源码公开、可移植和可裁剪的轻量级嵌入式实时操作系统内核,支持抢占式和协作式多任务,调度策略灵活。本设计主控系统主要包括系统信息更新、数据采集、USB 数据通信和关机守护等任务。

3.2.2 数据通信程序设计

主控单元与FPGA 数据通信是通过SPI 实现的。考虑到全谱数据传输量较大,为减少CPU 负担,提高系统性能,本设计使用SPI+直接内存访问(Direct Memory Access,简称DMA)的方式实现能谱数据的高速传输。DMA 允许数据直接在外设和内存之间传输,而无需CPU的直接干预,这可以提高系统的整体性能,使CPU 能够专注于执行其他任务。

4 整机性能测试

在整机完成研究后,对该系统进行测试与分析,图8 为数字化多道分析器的实物图。设计使用的探测器为北京某公司的CH158 型3 英寸NaI(Tl)晶体探测器,内置前置放大器,出厂说明书中脉冲幅度分辨率为7.0 %。主要性能测试包括能量分辨率、能量线性和积分非线性。

图8 多道分析器实物图Fig.8 Hoto of multi-channel analyzer

4.1 能量分辨率测试

能量分辨率(η)是γ能谱最重要的一个性能指标,一般用特征峰半高宽与峰位的比值表示[12-13],如公式(8)所示。

式(8)中:FWHM —特征峰半高宽,道址;E—特征峰峰位,道址;η—分辨率。

测试选用37Cs 源(0.662 MeV,计数S-1>3000),在实验室环境下(20-25 ℃)进行5 次测量。每次测量时间5 min。分辨率测试结果如表1。

表1 分辨率测试结果Table 1 Resolution test results

按照公式(8)计算能量分辨率,测试平均值为6.679 1 %,优于探测器厂家给出的7 %指标。

4.2 能量线性测试

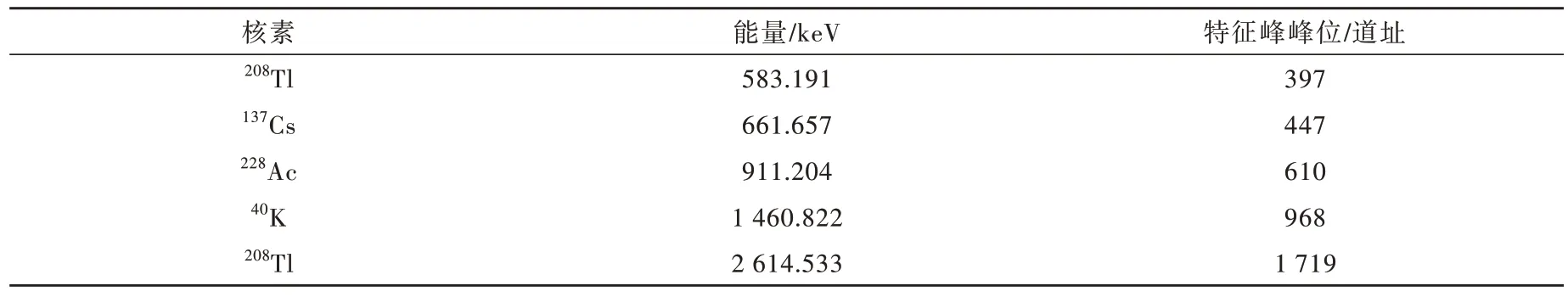

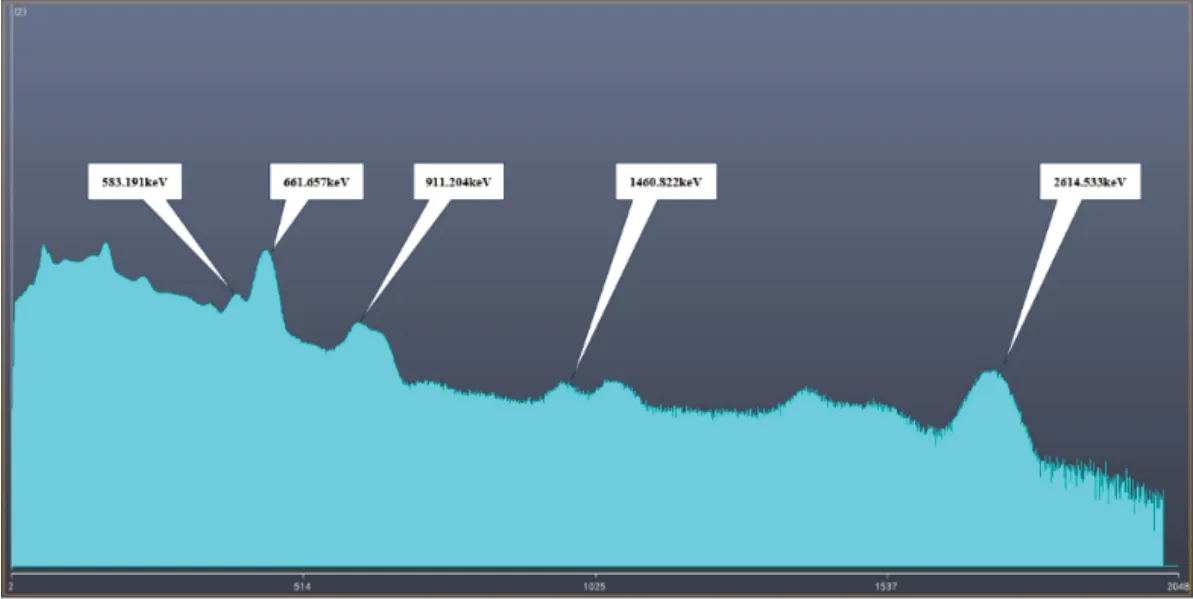

系统选用了三种不同的源来进行线性测试[14],分别为钍源232Th、铯源137Cs 和钾源40K,测出三种源的混合能谱,见图9(对数坐标),找到其对应核素(包括子体)的特征峰道址,对应关系如表2。

表2 混合源能量与道址对应关系Table 2 Relationship between energy and channel of mixed source

图9 混合源能谱图Fig. 9 Mixed source energy spectrum

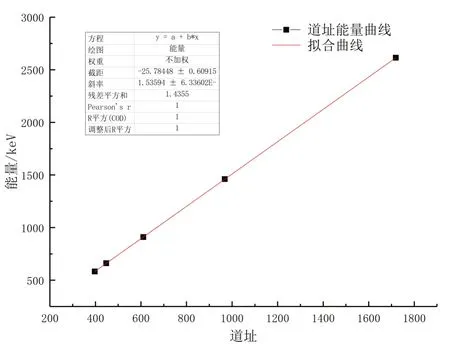

利用Matlab 进行线性拟合,得到结果如图10,拟合线性相关度R2在0.999 9 以上。结果显示能量与道址具有非常好的线性度,达到设计要求。

图10 能量线性拟合曲线Fig. 10 Linear fitting curve

4.3 积分非线性测试

积分非线性是指实际转化的道址与理想转化的道址之间的偏离程度,一般用实际幅度和理想幅度之间的最大差值与最大理想幅度的比值表示[15],见公式(9)。

式(9)中:INL—积分非线性;ΔVmax—实际输入幅度和理想输入幅度之间的最大差值,mV;Vmax—最大理想输入幅度值,mV。

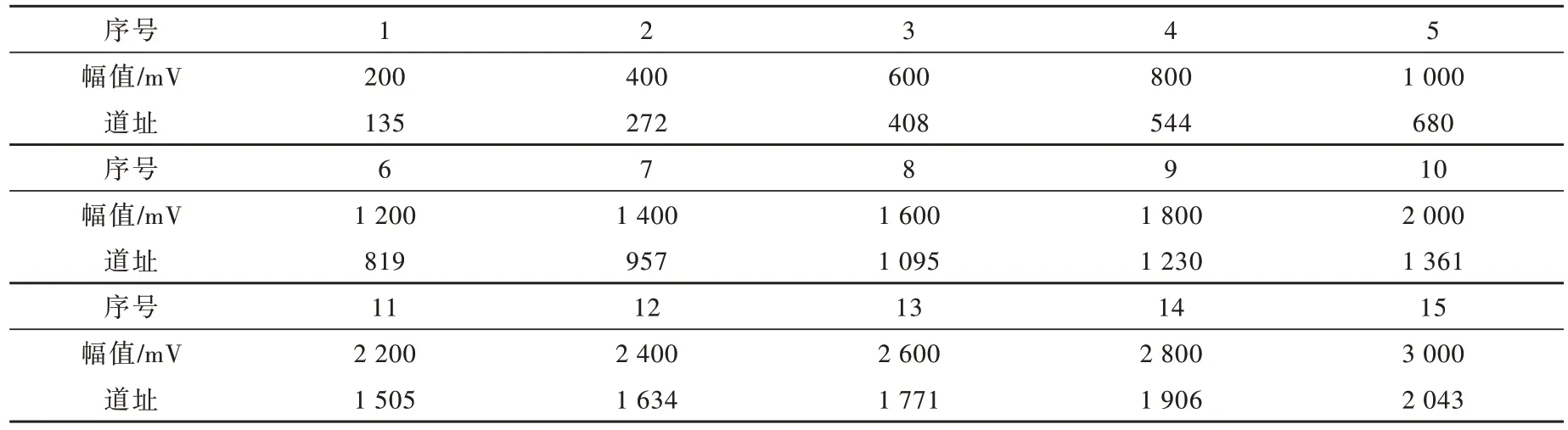

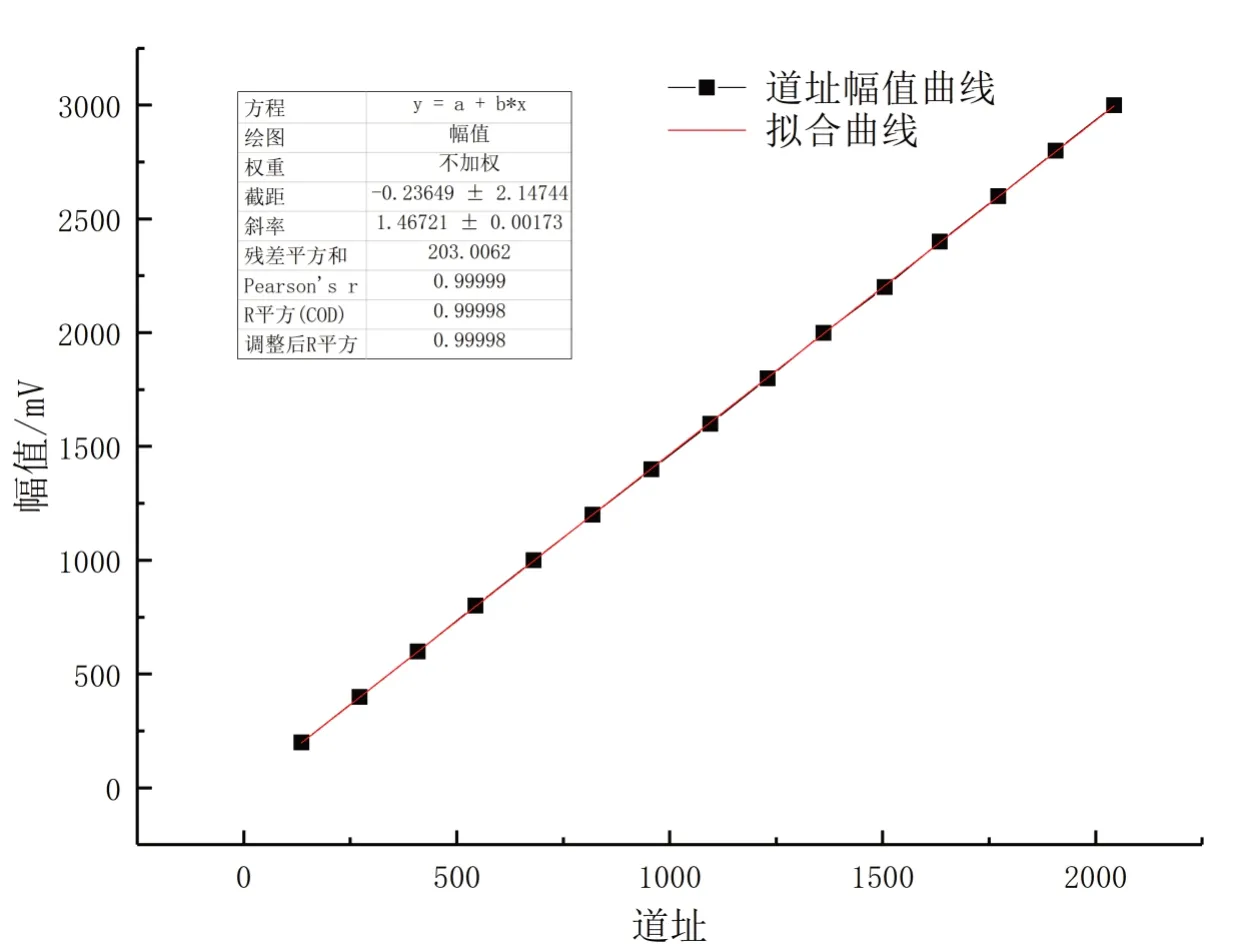

使用脉冲发生器产生一组固定频率、幅值由小到大的脉冲信号,每次改变脉冲幅值后记录相应的道址位置,通过Matlab 进行拟合,测试数据见表3,拟合结果如图11 所示。

表3 积分非线性测试数据Table 3 Integral nonlinear test data

图11 积分非线性数据拟合曲线Fig. 11 Fitting curve integral nonlinear data

通过matlab 拟合可得拟合方程见公式(10)。

式(10)中:V—脉冲幅值,mV;Ch—道址。

通过方程可得最大偏差为7.91 mV,理想最大电压输入为3 001.4 mV,计算得到其积分非线性为0.26 %。

5 结 论

1)以ARM 及FPGA 芯片为核心进行数字多道分析器设计,在FPGA 中完成了数字滤波、幅度提取、堆积判别、基线修正等关键模块开发。

2)在STM32 中使用实时操作系统FreeRTOS 实现多任务实时管理、能谱数据传输等功能。

3)仪器的能量分辨率、能量线性和积分非线性测试结果表明:该数字多道分析器满足γ能谱仪的使用要求。与传统的基于数字采集卡的多道分析器相比,大幅度降低了产品成本,具有广阔的市场前景。