一种可调延时超窄脉冲触发序列产生技术*

2024-02-17姚鼎一张敏娟

姚鼎一,景 宁,张敏娟,余 甜

(1.中北大学 信息与通信工程学院,山西 太原 030051;2.中北大学 前沿交叉科学研究院,山西 太原 030051)

0 引言

近年来,对更高数据率和更可靠通信系统的需求推动了高频信号的发展,使用传统的奈奎斯特定理对高频信号进行采样已经受到极大的限制,如5G 无线通信系统,其工作频率高达50 GHz,对其进行实时采样需要高达100 GS/s[1−2]。目前,国内对于ADC 采样率的研究最高可达20 GS/s,对于获取10 GHz 以上高频信号,只能依赖于国外高速采集模块,且高速ADC 一般仅有6~8 bit,转换位数变低,采样精细度也随之降低,而等效采样作为前沿技术,可以在信号的不同周期进行顺序采样,极大地降低了对采样率的要求,且可以实现14 bit 及以上垂直分辨率[3],提高了采样精细度。对信号进行等效采样,关键在于被测高频信号周期极短,需要一种极窄脉冲信号作为本振信号在ps 级时间内触发信号。故产生一种延时步进可调、边沿极窄的脉冲信号是进行等效采样、重构波形的关键技术。

目前,是德科技和泰克公司对精密延时触发电路的研究已经应用于86100 系列、N1000 系列、TSO820 系列产品,延时步进达到ps 级,最高模拟带宽达70 GHz 以上[4−5]。而国内关于精密延迟技术的研究并没有较为成熟的方案。天津大学陈泽洋等人利用现场可编程门阵列(FPGA)设计的延迟发生电路稳定性较好,但精细延时步进最小仅达到16 ps,由于抖动时间为450 ps、测量时间较长等问题,其可测高频信号约为10 GHz。中国科学与技术大学张文哲等人提出基于多级时间插值方法实现脉冲序列的产生,但该方法对时序要求极高,且需要较长的时间建立延迟链,系统整体运行较慢[6−7]。

在本文中,利用数字延时电路与模拟调理电路结合起来,以产生一种延时范围可变、高精细延时步进、边沿时间极短的脉冲信号。采用数字电路电压控制法进行延时范围及步进的调整,通过三极管与阶跃恢复二极管的级联电路对脉冲信号进行压缩处理,达到输出信号脉冲宽度窄、延时步进可控的效果。

1 延时超窄触发序列产生原理

取样示波器主要要通过顺序等效采样对信号进行采集。精密时基模块作为取样示波器输入前端,通过对外部输入的高频触发信号进行调理,产生延时超窄脉冲信号,控制取样器对高频被测信号进行取样。

等效时间的采样方式,在某种意义上不需要受到奈奎斯特采样定理条件限制,同样可以达到高精度的信息采集结果[8]。等效采样技术是利用时域展宽技术来实现用低速的ADC 转换器对高频信号的数据采集,它是在被测信号一个周期或若干个周期采集一个点,通过多次采样,可以保证能在一定时间内获得一个信号周期内的所有取值,从而重构目标信号,这等价于一次完整的实时采样过程[9]。

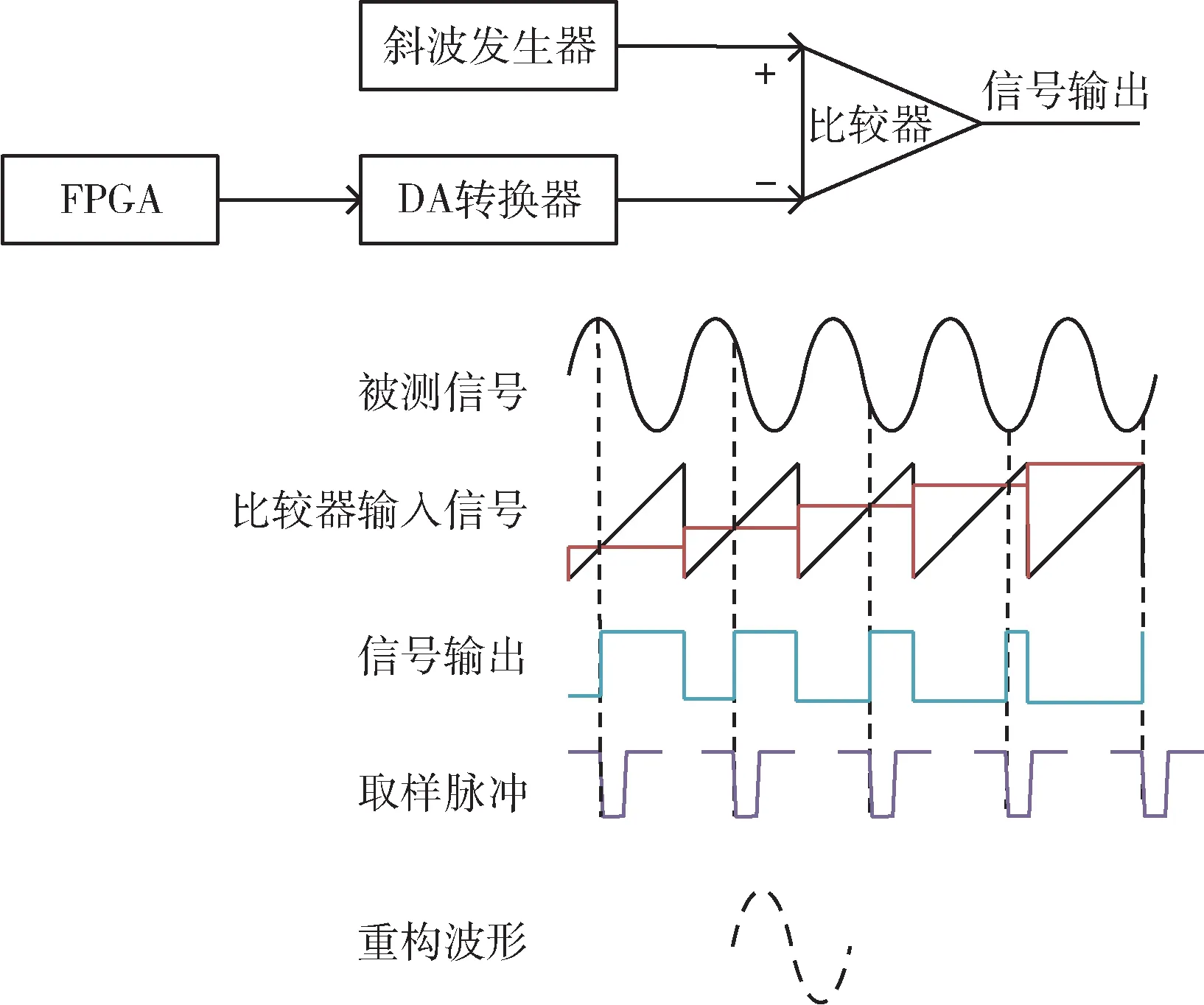

等效采样的关键是采样两点之间Δt的控制,即对延时步进的控制,本文主要通过数字电压控制方法调整延时步进,工作原理如图1 所示。

图1 数字电压控制法原理

延时模块主要由3 部分组成:线性斜波发生器、DAC转换器和比较器。当计数器产生的进位脉冲经D 触发器同步进入延时模块,通过FPGA 设定DAC 数字输入,使其电压从零阶梯状上升到设定的阈值电压,FPGA 数字输入改变,DAC 阈值电压与延时范围随之改变,在DAC 阶梯波形与斜波信号进行周期比较后,进位脉冲在比较器输出上升沿触发产生延时取样脉冲。

产生的延时脉冲信号存在幅度小、脉宽大的问题,无法驱动取样器对高频信号进行采样,需要对延时序列进行幅值放大与脉宽压缩[10]。本文主要利用阶跃恢复二极管的特性对延时序列进行处理,工作原理如图2 所示。

图2 阶跃恢复二极管工作原理

普通二极管由于单向导通特性,表现出极具特点的开关特性。当二极管两端加上反向电压,电流并不是立即趋近于零,而是先突跳至式(1),并保持一段时间不变,放电后电流趋近于零,如图2(a)所示。

其中,IF为正向导通电流,IR为反向电流,EV为二极管两端电压,RL为负载电阻。二极管的反向恢复时间由存储时间与暂态时间相加,总时间T为:

式中,T为二极管反向恢复总时间,TS为存储时间,TT为暂态时间。

阶跃恢复二极管作为一种特殊的变容器,在进入反向偏置状态时,阶跃恢复二极管内的多数载流子所用复合时间比普通二极管少很多,故阶跃恢复二极管的暂态时间极短,上下沿时间可以达到皮秒级别[11−12]。通过阶跃恢复二极管可以对脉冲边沿压缩到皮秒级。

SRD 等效电路模型如图2(b)所示。在电流i正向流通时,SRD 正偏,二极管结电容电压近似为零并开始充电;当SRD 两端施加反偏电压,SRD 上的储存电荷开始放电,这时二极管压降仍等于0。但是当储存电荷快要放电完毕时,电流会突然减小,而电感作为感性元件,将阻止电流变小,从而产生一个反向高电压,这时二极管上就有一个反向高压脉冲出现,电流减小得越快,这一感应电压脉冲幅度越大,下降沿越抖[13−15]。此后,二极管重复上述的过程,周期性地产生窄脉冲信号。

2 延迟触发序列产生电路设计

本文设计电路主要由两部分组成,即前级延时电路和后级脉冲调理电路。首先由外部输入100 MHz~12 GHz 时钟信号作为触发信号,经过分频后反馈给FPGA 测频,FPGA 经内部时钟计数测量准确得知输入信号频率,控制计数器与延时时间,产生可编程延时触发序列,由于产生的序列幅值过小,脉冲下降沿时间过长,无法驱动混频器对被测信号进行采样,需要经过三级功分放大电路对触发序列的关键指标进行调理优化,达到采集高频信号的需求。

2.1 延时电路设计

精密时基系统图如图3 所示,首先外部触发信号经过一级分频与二级分频模块,扇出两路差分同步触发信号,一级分频为可编程模块,由两片HMC862 级联组成,最大分频为64 分频,并可以将输入单端信号转为差分信号;二级分频由两片MC100EP33 级联为固定16 分频,通过固定分频反馈给FPGA,每100 ms 进行一次测频,后FPGA 控制一级可编程分频模块使同步触发信号频率降频至256 MHz~512 MHz 范围内。在确定分频比的同时,另一路同步触发信号作为时钟驱动MC10EP196 计数器工作,FPGA 通过设置计数器初始值产生50 kHz 的进位脉冲信号,经过D 触发器后进位脉冲与触发信号同步,输入给延时模块进行延时处理,延时参数Δt与上位机时基档位Td和采样点数N有关,计算公式如式(3)所示:

图3 可编程延迟触发序列产生技术系统示意图

式中,Δt为延时步进,N为采样点数,Td为时基挡位,时基挡位设置为100 fs/div~125 μs/div 多个挡位。确认延时参数Δt后,通过FPGA 将延时参数Δt转化为对应的DAC 输出的电压控制延时模块,即可对进位脉冲信号进行Δt的延迟,最终产生延时步进范围0~2.4 ns 可调,采样率最低1 ps,幅值1.5 V 左右的延时触发序列。

2.2 脉冲信号调理电路设计

为了满足混频器的工作条件,对被测信号进行采样,触发信号幅值需大于5 V,边沿时间小于200 ps,故需要对延时信号进一步的优化,提高负脉冲的幅值,压缩脉冲宽度。为此设计了脉冲信号调理电路,该电路主要由三极管和阶跃恢复二极管级联构成,利用容性与感性器件对负脉冲信号进行压缩和幅度放大,得到超窄脉冲信号,使脉冲的下降沿能达到皮秒数量级,从而满足取样器的高带宽输入要求。

双通道调理电路为多级串联电路,每个三极管的输出为一级,延时触发序列进入调理电路,首先由5 GHz宽带PNP 三极管Q1 对信号进行反向及幅值放大,Q2 和Q3 为7 GHz 宽带NPN 三极管,前者组成射极跟随电路,利用射级跟随器高输入阻抗低输出阻抗的特性,对幅值进行偏置调节,提高电路带载能力;后者对信号再次反相,进行幅值放大。D1 为阶跃恢复二极管,选用MACOM 公司的MMD820 二极管,暂态时间最小可达80 ps,与L1、R8 及C8 对信号进行压缩与放大,改善脉冲的前后沿,通过改变储能器件C8 的容值,幅值及边沿时间也随之改变,容值越小,充放电时间越短,边沿时间也就越短,但幅值也因此较小,为满足两者要求,选取5 pF电容。最终电路设计如图4 所示。

图4 级联电路仿真图

3 实验结果及数据分析

3.1 仿真验证

3.1.1 延时触发序列电路仿真

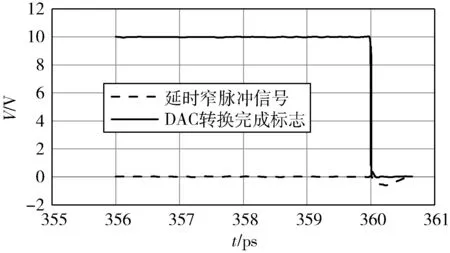

利用ADI 公司的LTspice 软件对延时触发序列电路进行仿真。通过参数设置使输入信号模拟DAC 阶梯输出,在DAC 电压转换完成后,进位脉冲进行相应的步进延时,展开图如图5 所示。

图5 延时电路仿真结果

3.1.2 脉冲信号调理电路仿真

脉冲信号调理电路同样使用LTspice 软件进行仿真。设置输入为900 mV 的脉冲信号,经过三级三极管级联电路后,脉冲信号幅值变大,电压偏置进行了调整,经过阶跃恢复二极管及外围电路后,输出窄脉冲信号,其与输入信号对比结果如图6 所示。

图6 输入输出信号对比图

最终输出信号仿真幅值为5 V 左右,脉冲边沿相较于输入信号明显变窄。通过仿真可知,脉冲调理电路可以对延时触发信号进行优化处理。

3.2 实测验证

为了验证所设计电路的功能完整性,对设计的延时触发序列产生电路与调理电路进行分别调试及联调测试。搭建硬件测试平台如图7 所示。

图7 硬件测试平台

电路板(1)为时基电路,电路板(2)为脉冲调理电路。通过射频源E8257D 产生信号,使用采样率为20 GSa/s、带宽为4 GHz 的示波器(RTO2044)对信号进行测量。

3.2.1 时基电路测试与分析

时基电路作为等效采样的关键,其脉冲延时范围、边沿时间及幅值是重要分析参数。使用射频源产生1 GHz 射频信号作为外部触发信号输入给时基电路,使用示波器来测量延时范围。设置延迟模块进行2 000 次步进延迟,每次步进延迟1 ps,总延迟范围为2 ns,取样周期为20 μs。以延时输出为同步参考,将其下降沿作为触发条件,将60 MHz 正弦波用高频线缆连接至示波器进行观察。如图8(a)所示,在示波器余晖模式下,从示波器的时域上分析,最终正弦信号相对于初始相位依次移位2 ns,满足延2 ns 动态延迟范围。将延时输出展开分析,示波器时域刻度调整到200 ps/div,通过光标对幅值与下降沿时间进行精密测量,如图8(b)所示,输出幅值为1.5 V,边沿时间为466 ps,还需进行调理优化。

图8 时基电路测试结果

3.2.2 脉冲信号调理电路测试与分析

延时电路连接至调理电路,先经过3 个级联三极管对信号幅值及边沿进行调整,一级输出对输入反相调节,幅度放大至5 V 左右,经二三级改善脉冲边沿,提高电路带负载能力。

最后通过阶跃恢复二极管及外围电路对信号进行脉宽压缩及幅值放大,脉冲的下降时间作为驱动取样器的重要指标,在达到0~200 ps 范围内,取样器才会进行信号采样工作。在本文进行的测试中,下降时间是从脉冲振幅的10%~90%计算。图9(a)显示了下降沿测试的结果,将超窄脉冲展开分析,由光标测得下降时间为109 ps,振幅为10.12 V,满足设计要求。通过对输入输出信号进行比较,如图9(b)所示,可知脉冲调理电路对延时脉冲的幅值与边沿时间进行了极大的改善。

图9 下降沿测试结果

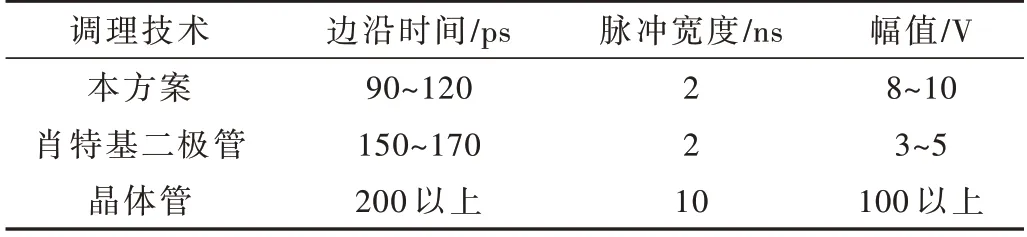

通过以上设计的仿真与测试结果可以发现,本次设计的触发序列及调理电路主要特点是采样带宽较宽,信号边沿极窄,工作幅值适中。与近几年出现的其他脉冲调理技术相比有较为优秀的综合性能指标,对比结果如表1所示,相较于其他两种调理技术,脉冲信号经本方案调理后边沿更窄,脉冲宽度即等效采样率较高,且幅值可以驱动后级取样器对高频信号进行采样。

表1 本方案与其他调理技术指标对比

4 结论

本文针对触发信号的延时范围与边沿时间等重要指标进行深入研究,设计了触发序列产生与调理电路,由此产生的脉冲信号可以输出到采样器,对高频信号进行精确采样。通过FPGA 编程,精密时基信号的延迟范围可以精确控制在0~2.4 ns 范围内,采样率可达1 ps。此外,脉冲信号通过调理后下降沿极窄,这使采样过程中的失真最小化。实验结果表明,延时触发序列信号的振幅可以达到10 V 左右,其下降沿可以控制在120 ps 之内,使触发信号的各个指标得到大幅度优化,适合用于采样器对更高频信号的等效采样。