基于谐波混频的X 波段频率源设计

2023-12-25李世浩蒋润秋莫世波

李世浩,蒋润秋,莫世波

(成都天奥测控技术有限公司,四川 成都 611731)

0 引言

随着微波技术和器件设计制造技术的不断发展,雷达设备、仪器仪表、消费电子设备已经成为生产和军事中必不可少的设备,而频率源是现代雷达、电子干扰与对抗、仪器仪表、消费电子、通信设备的核心部件,其直接决定了电子设备的整体性能。频率合成技术通常采用直接数字式(Direct Digital Synthesizer,DDS)和锁相环式(Phase Lock Loop,PLL)两种,但DDS 技术具有合成频率低的问题,PPL 技术具有频率分辨率低的问题。

为解决上述问题,文献[1]中基于高性能和小型化的滤波器以DDS 技术为主导,设计出相位噪声优于-85 dBc/Hz@1 kHz,杂散和谐波抑制优于45 dBc,频率分辨率达到1.86 Hz,跳频时间最快4 ns 的Ka 波段捷变频频率源;文献[2]中采用DDS+PLL 相结合的设计方法设计出频率为9.2 GHz~9.4 GHz、频率步进25 kHz、调制周期为2.4 ms、相位噪声为-85 dBc/Hz@100 kHz 的X 波段频率源。文献[3]提出了一种DDS+PLL 的X 波段频率源,该频率源输出频率为8.5 GHz~9.5 GHz,相位噪声为-115 dBc/Hz@100 kHz,相位锁定时间为580 ns。

为得到更低的相位噪声和更好的杂散抑制能力,同时结合实际的工程应用需求,本文介绍了一种基于谐波混频降低相位噪声和小数型PLL 调节输出频率分辨率的X 波段频率源。该频率源利用谐波混频产生的射频信号,采用压控振荡器(Voltage Controlled Oscillator,VCO)加PLL 混频的方式,降低频率源的分频倍数,使模块具有低相位噪声、良好杂散抑制、小步进、小体积、低成本的优势,能够适用于各种需要小型化、低相位噪声、低杂散X 波段频率源的应用场景。

1 方案与原理

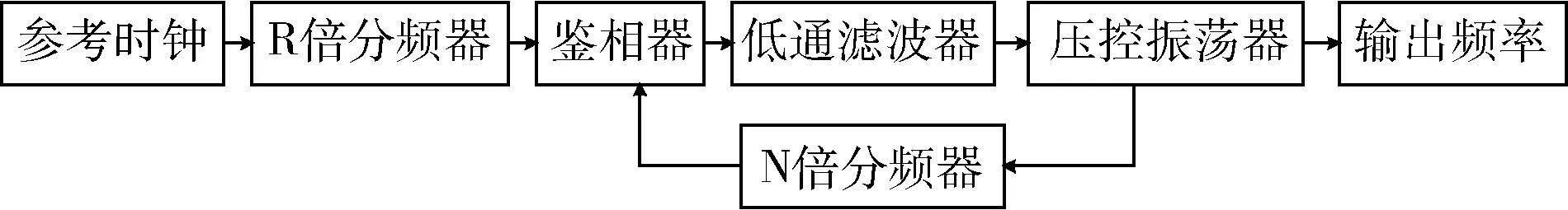

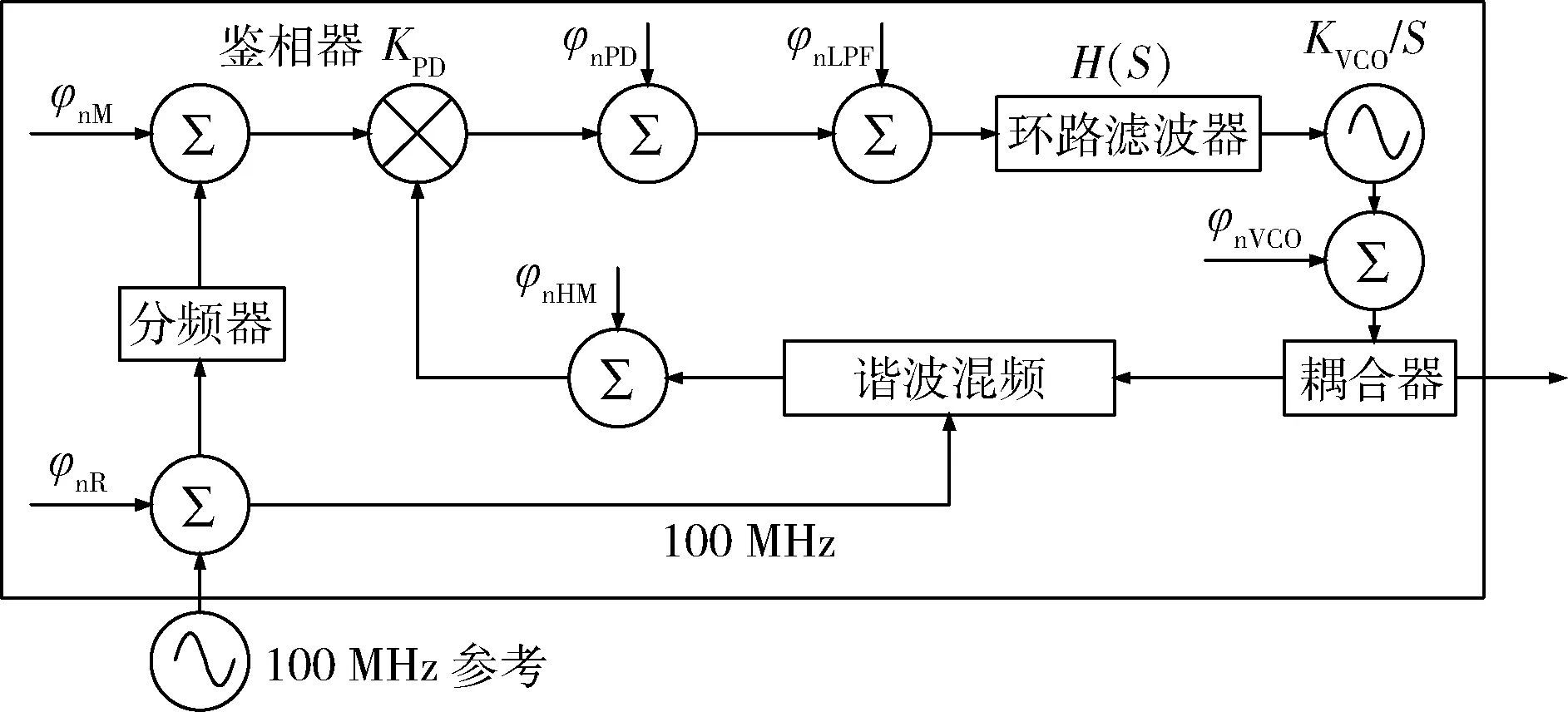

PLL 是由鉴相器、低通滤波器、参考时钟、分频器和压控振荡器组成的负反馈系统。其中输出频率由参考时钟和两个分频器决定,参考时钟和R 倍分频器决定了频率源的最小分辨率,N 倍分频器决定了锁相环的相位噪声。PLL 原理框图[4]如图1 所示。

图1 PLL 原理框图

在PLL 系统中,鉴相器对压控振荡器输出频率进行N 倍分频后与参考时钟R 倍分频后的信号进行频率和相位的对比,当两者的频率和相位不一致时,鉴相器会输出低频信号,通过低通滤波器后输出直流信号控制压控振荡器进行频率调节。当两者的频率和相位一致时,鉴相器会输出一个恒定的直流电压,此时压控振荡器的输出频率不再变化,从而达到频率锁定的状态[5]。

PLL 的输出频率主要由参考时钟和两个分频器的倍数决定,其公式如下所示:

式中,fREF/R为鉴相器的参考频率,同时也决定了PLL 的最小分辨率,N为N 倍分频器的倍数。锁相环的带内相位噪声可由下式进行估计,其估计公式如下[6]:

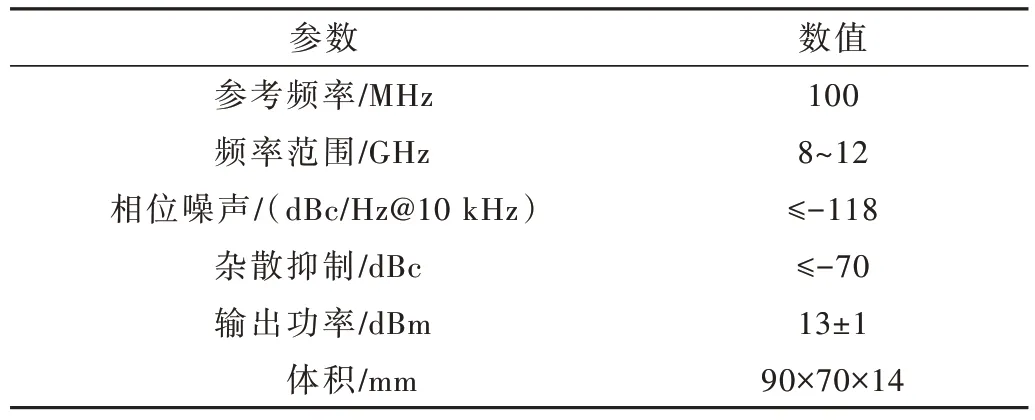

式中,NPD为鉴相器的归一化相位噪声。若N 倍分频器的分频倍数为1 时,锁相环的相位噪声将大大降低[7]。所以本文采用谐波混频环产生的低相位噪声射频信号与细步进锁相环中的VCO 进行混频用于代替PLL 系统中N 倍分频器的作用,且控制程序始终将细步进锁相环的鉴相比固定为1∶1。针对X 波段频率源的发展水平以及实际需求,该频率源的主要指标要求如表1 所示。

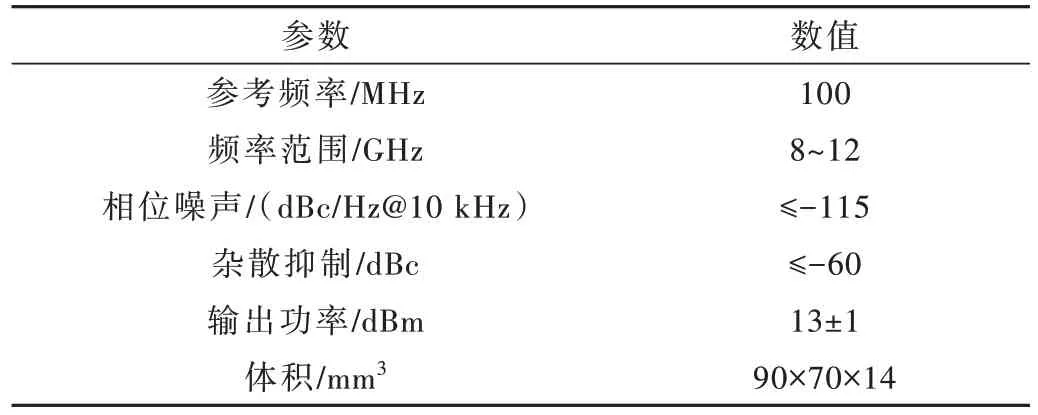

表1 X 波段频率源性能参数

该X 波段频率源基于谐波混频和细步进PLL 提出一种工作频带宽、相位噪声低、低杂散、小体积的频率源设计方案,方案框图如图2 所示。

图2 频率源方案框图

该X 波段频率源采用谐波混频环加细步进PLL 的框架结构。首先通过无源LC 3 路功率分配电路将外部参考时钟100 MHz 信号等分为3 路信号,一路作为谐波混频环中鉴相器ADF4002 的参考信号;一路作为谐波混频的激励输入信号,产生低相位噪声的谐波,作为整个环路的相位噪声基准源;一路作为HMC830LP6GE 的时钟参考信号,产生细步进锁相环的参考信号,作为模块分辨率的基准。

谐波混频环为整个频率源的核心构架,通过谐波混频环,获得100 MHz 跳频步进的X 波段的粗步进环。谐波混频环最终输出信号经耦合放大后作为粗步进PLL中混频器的射频输入。由于细步进PLL 的鉴相比始终控制为1:1,因此恶化相位噪声有限。因此,整个X 波段频率源的相位噪声由谐波混频环和时钟晶振决定。为克服传统集成VCO 的PLL 锁定时间较慢的情况,在实现过程中,谐波混频环与细步进PLL 均需建立扫表工作方式,辅助缩短PLL 锁定建立时间。

该方案中,采用HMC830LP6GE 用于提高频率源的分辨率,谐波混频环代替N 倍分频器,用于改善频率源的相位噪声,采用高精度、高稳定度、低抖动、低噪声的参考时钟,用于改善频率源的相位噪声和杂散抑制。

2 设计与实现

2.1 器件选择

(1)频率合成器

该频率源选择ADI 公司的ADF4002 作为频率合成器,该频率合成器包含一个低噪声的鉴相鉴频器,一个电荷泵,一个13 位的N 倍分频器,一个14 位的R 倍分频器,用于调节参考时钟的输入,同时具有5 MHz~400 MHz的压控振荡器频率输入带宽和20 MHz~300 MHz 参考时钟频率范围。当低通滤波器的带宽为500 kHz时,ADF4002 的相位噪声的典型值为-222 dBc/Hz@100 kHz。

(2)小数锁相环

该频率源选择Hittite 公司的HMC830LP6GE 小数型锁相环作为分辨率的控制。HMC830LP6GE 是一个低噪声、大带宽、小数型的锁相环,能够输出25 MHz~3 000 MHz的频率范围,输出0 dBm~9 dBm 的幅度范围。采用HMC830LP6GE 替代传统DDS,其目的是提高该频率源的频率分辨率与降低模块功耗。

(3)LDO 电源

本次设计中,选用Linear 公司的超低噪声LDO,型号为LT3045IDD#PBF。其具备低至0.8 μVrms 和2 nV/Hz的噪声,在1 MHz 时还具备76 dB 的超高共模抑制比。同时,具有1.8 V~20 V 的超宽输入电压范围、0.26 nV 的低压差和500 mA 的电流输出能力,外围电路简单,只需要一颗单电容,即可改善噪声和抑制比。

(4)参考时钟

(5)放大器

本次设计中,选用Skyworks 公司的InGaP HBT 增益放大器SKY65017_70LF 用于信号的幅度调理。该器件具有21 dB 的放大增益和20 dBm 的1 dB 压缩点,供电仅需+5 V,并具有小于1.4 的输入回波和输出回波损耗。

2.2 谐波混频环设计分析

考虑到谐波混频环在该频率源中的重要性,综合链路中的各种电路器件及环路滤波器等各种因数,建立其等效的噪声原理图如图3 所示。

图3 谐波混频环等效噪声原理图

谐波混频环的相位噪声,主要由参考时钟相位噪声φnR、谐波混频相位噪声φnHM、鉴相器相位噪声φnPD、环路滤波器相位噪声φnLPF、压控振荡器相位噪声φnVCO决定。而上述所有的相位噪声与参考时钟的相位噪声以及倍频次数有关。根据倍频原理以及相位噪声的计算方法,可以估计出谐波混频环相位噪声的估计值。相位噪声的计算公式如下[8]:

式中,fres为外部参考时钟的相位噪声,K为谐波混频环的倍频次数。该频率源的最高输出频率为12 GHz,所以倍频次数如下所示:

根据相位噪声的计算公式得知,谐波混频环的估计相位噪声为-123.4 dBc/Hz/10 kHz。

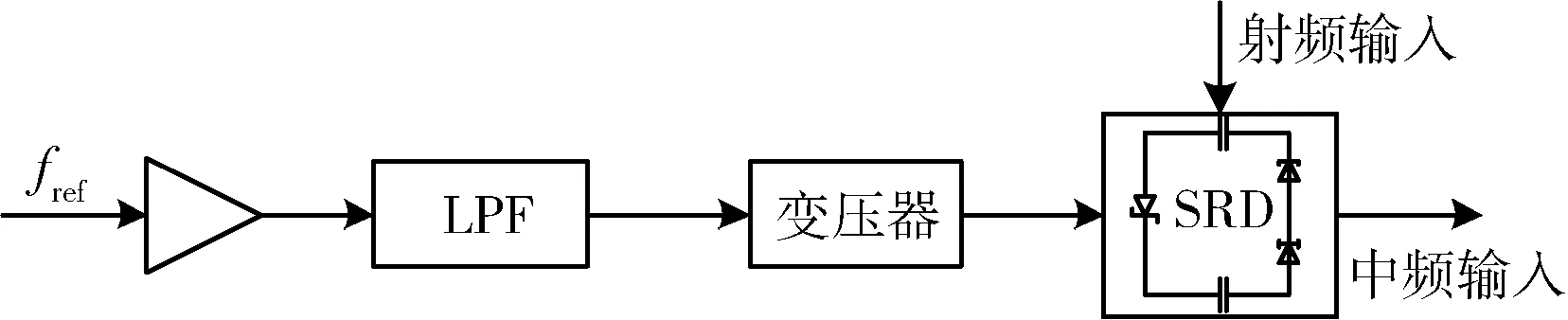

谐波混频的核心电路为取样鉴相器及外围电路,电路原理如图4 所示。

图4 谐波混频电路原理图

谐波混频以取样鉴相器(Sample Phase Discriminator,SPD)作为核心器件。SPD 包含一个阶跃恢复二极管(Step Recovery Diode,SRD),一对肖特基二极管,两颗小容值电容。谐波混频的核心原理是将幅度足够大、相位噪声低的参考信号100 MHz 通过SRD 后产生高次谐波,并且各次谐波与VCO 的振荡频率进行混频,通过低通滤波器选频滤波后,作为谐波混频环中鉴相器的射频回环信号,产生覆盖X 波段的大步进频综。

谐波电路中,驱动SRD 的电平值需大于17 dBm。因此,参考信号放大器为谐波混频的关键器件。本文选用P1dB大于20 dBm 的放大器以满足工程需求。由于SPD 的阻抗值不为50 Ω,因此选用合适比例的巴伦进行匹配阻抗[9]。电路中的低通滤波器用于防止射频信号泄漏到本振端口和中频端口[10]。

第三,对康复性地方的解析需要进一步与体验研究相结合。并非所有的康复性地方都具有健康的特质,自然环境也可能引致特定人群的压力。Conradson(2005)指出地方促进健康的机制归根结底是人类在地方的行为和感受发挥了作用,地方与健康不存在直接的联系。因此,为理解这种模糊性,在后续研究中,需要更加关注个体在流动中对环境和空间的主观体验与感受(Milligan,Gatrell& Bingley,2004),采用关系视角,探讨个体与地方的社会—自然互动所引致的生理、心理结果(Conradson,2005),从而全面认识地方与健康的关系。

根据SRD 的阶跃时间直接决定了谐波混频环的输出频率和倍频效率,所以选择合适的阶跃时间是至关重要的,SRD 的阶跃时间公式如下所示:

式中,tst为SRD 的阶跃时间,fR为谐波混频环的输出频率,该X 波段频率源所选用阶跃时间小于45 ps 的SRD,其最高频率可达22 GHz。

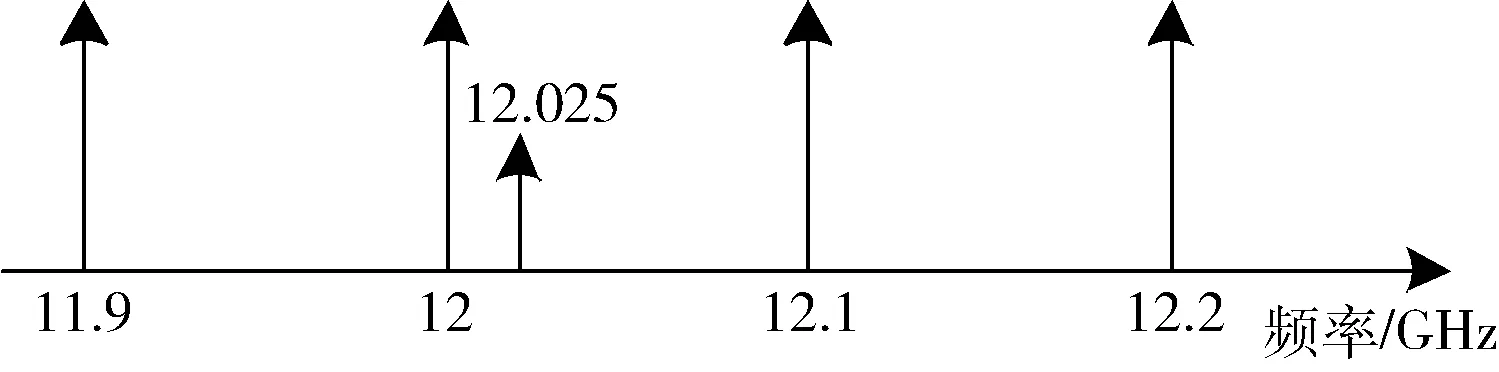

谐波混频环产生的杂散较多,但由于所需频点为远离100 MHz 谐波中的无关频点,因此,在反馈链路中,通过添加合适的低通滤波器,即可滤除其他谐波混频产生的无关频率,典型的谐波混频频率关系如图5 所示。

图5 谐波混频环频率关系图

谐波混频器会产生大量的谐波,如果采用常规PLL方式,将无法锁定至所需频点。因此,在设计中,需采用预置频率的方式,将所需频点通过内置PLL 的方式进行锁定。锁定后,存储此时的VCO 频率,再通过开关切换至谐波混频环,此时,集成锁相环中仅VCO 处于工作状态,相当于集成锁相环芯片仅提供VCO 功能。为了减小体积,集成锁相环采用的器件型号为TI 公司所生产的高性能锁相环LMX2594,其主环频率覆盖7.5 GHz~15 GHz,覆盖本文设计中的X 频段,而且内部VCO 相位噪声低,底噪低至-236 dBc/Hz,32 bit 的fractional-N 分辨率,仅需单电源3.3 V 供电即可,且具有两路输出,适用于本次设计。

3 测试结果

该X 波段频率源通过选用高度集成有VCO 的PLL与谐波混频环进行多环共同作用,代替传统离散VCO+PLL 的构架方式,链路虽然复杂,但采用集成度高的芯片,能够有效减少链路器件数量,并通过合理采用已建立成熟电路,例如射频LDO 的CBB 等电路,能够大幅降低频率源设计的难度并有效缩小模块体积,缩短设计周期。最终频率源体积为90 mm×70 mm×14 mm,模块外形图如图6 所示。

图6 X 波段频率源外形图

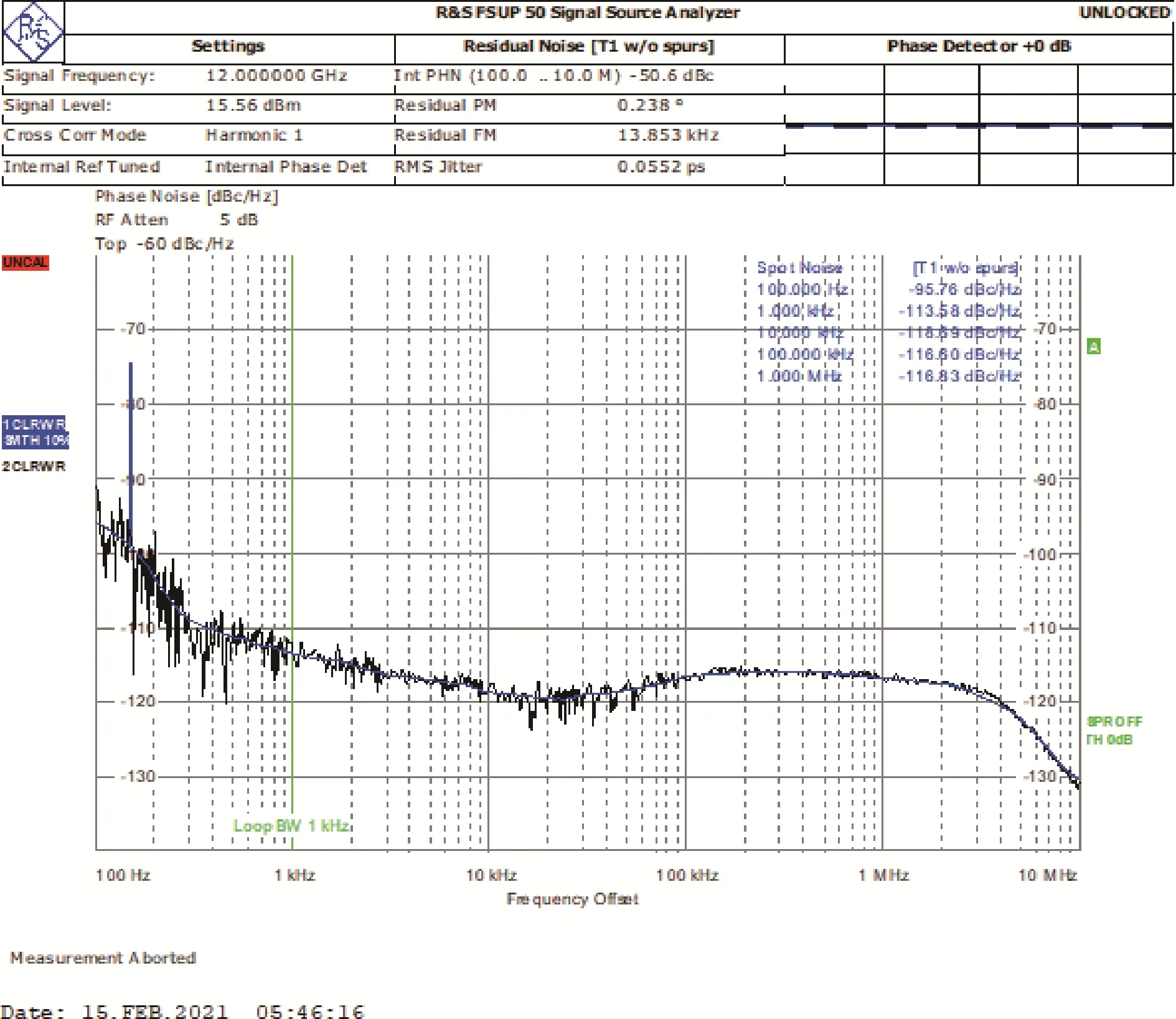

X 波段频率源指标主要包含相位噪声和杂散两项指标。在12 GHz 时,X 波段频率源相位噪声实测结果如图7 所示。

图7 相位噪声实测结果

从图7 中可以看到,X 波段频率源相位噪声达到了-113 dBc/Hz@1 kHz、-118 dBc/Hz@10 kHz,优于设计中所需的-115 dBc/Hz@10 kHz 相位噪声要求。

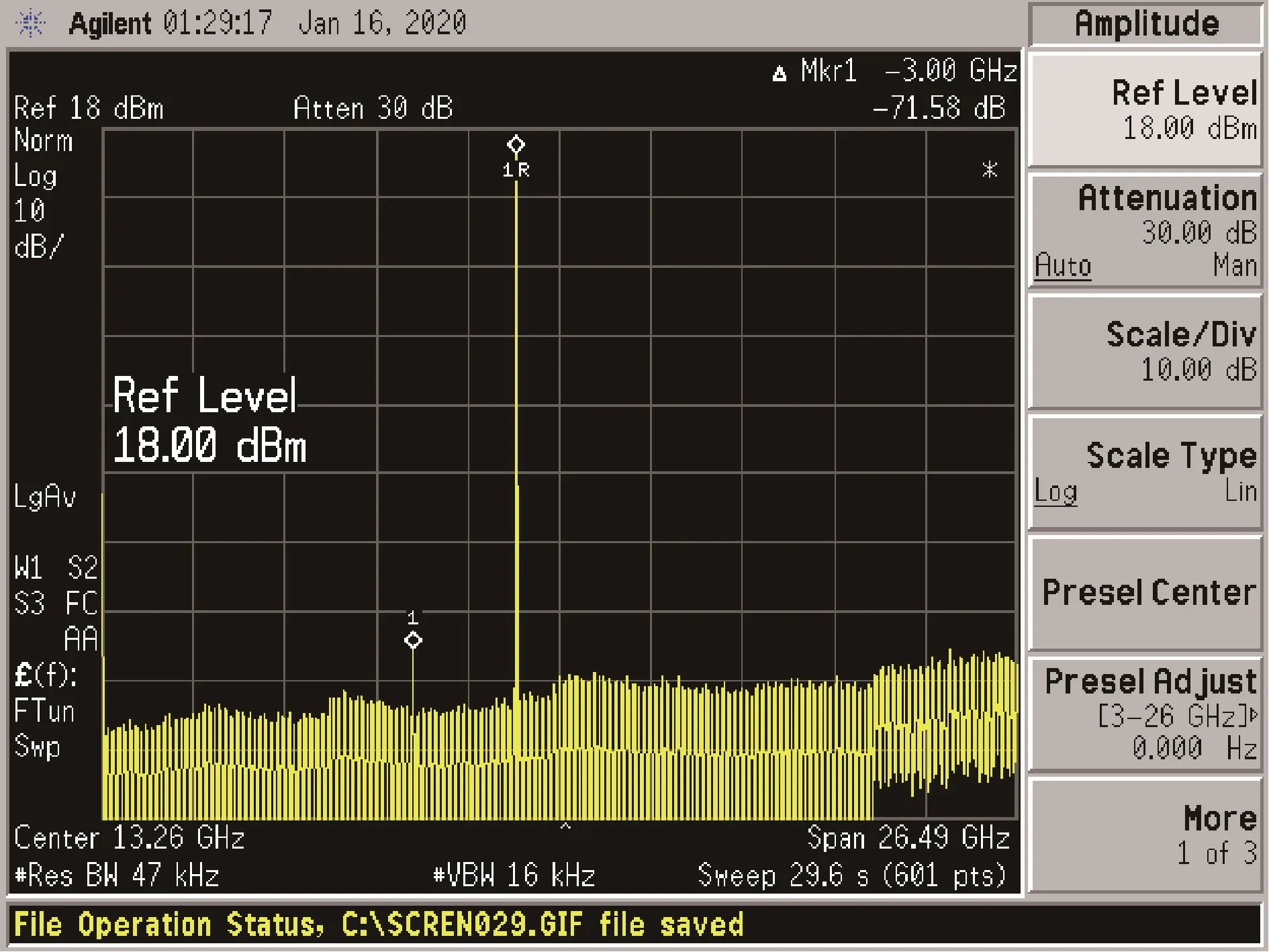

在12 GHz 时,X 波段频率源宽带杂散测试结果和窄带杂散测试结果分别如图8 和图9 所示。

图8 宽带杂散实测结果

从图7、图8 和图9 中可以得出本次设计的频综模块达到了表2 所示的技术指标。

表2 本文频率源性能达到参数

本文设计的频率源相位噪声达到-118dBc/Hz@10 kHz,远端杂散和近端杂散达到70 dBc,优于相噪目标值-115 dBc/Hz@10 kHz、杂散60 dBc 的目标值,满足了工程应用需求。

4 结论

本文研制了一种基于谐波混频锁相技术的低相噪毫米波频率源,以谐波混频环为核心环,通过谐波混频环与细步进锁相环1∶1 的鉴相比,实现了频率源的低相位噪声和低杂散。

在本文基础上,若采用DDS 等方式作为细步进环的参考频率,可使频率源在频率分辨率上更上一台阶。