SoC 芯片上I3C 控制器IP 的设计与验证*

2023-12-04阮宇鹏

阮宇鹏,刘 威,2,3,4

(1.武汉大学 物理科学与技术学院,湖北 武汉 430072;2.武汉大学 微电子学院,湖北 武汉 430072;3.湖北珞珈实验室,湖北 武汉 430072;4.武汉量子技术研究院,湖北 武汉 430072)

0 引言

I2C(Inter-Integrated Circuit)接口是一种广泛应用于集成电路领域的串行通信协议,它可以将多个设备连接到同一条总线上,特别适用于嵌入式系统和其他需要少量设备通信的应用。然而,随着行业的发展,移动无线和受移动影响的产品中传感器的数量激增,这给设计者带来了巨大的挑战,因为没有一致的物理传感器接口方法,使得传感器的接口设计变得更加复杂和多样化,从而影响了系统的性能和可靠性。设备和平台设计人员面临着来自各种数字接口的挑战,包括但不限于I2C、SPI 和UART 等[1]。例如I2C 速率低、功耗大的短板日趋明显,为了增强I2C 的性能,MIPI 将I3C (Improved Inter Integrated Circuit)接口标准作为I2C 协议的演进。MIPI联盟是一个由ARM、诺基亚、意法半导体和德州仪器等公司于2003 年发起成立的国际组织,旨在为移动应用处理器提供一个开放的标准和规范,以降低设计复杂度和成本,提高设计灵活性和效率,并为此制定了一套完整的接口标准[2-4]。

I3C 是一种双线总线:串行数据(SDA)和串行时钟(SCL),它能够在某些高数据率(HDR)情况下充当时钟引脚或数据引脚。并且I3C 总线可以支持不同类型的混合消息,例如:使用最高12.5 MHz 的SCL 时钟速度传输类似I2C 的单数据率(SDR)消息和实现更高数据率的HDR 消息,该规范还为I3C 从设备之间的点对点通信提供了条件[2]。

1 I3C 对比I2C 的优势

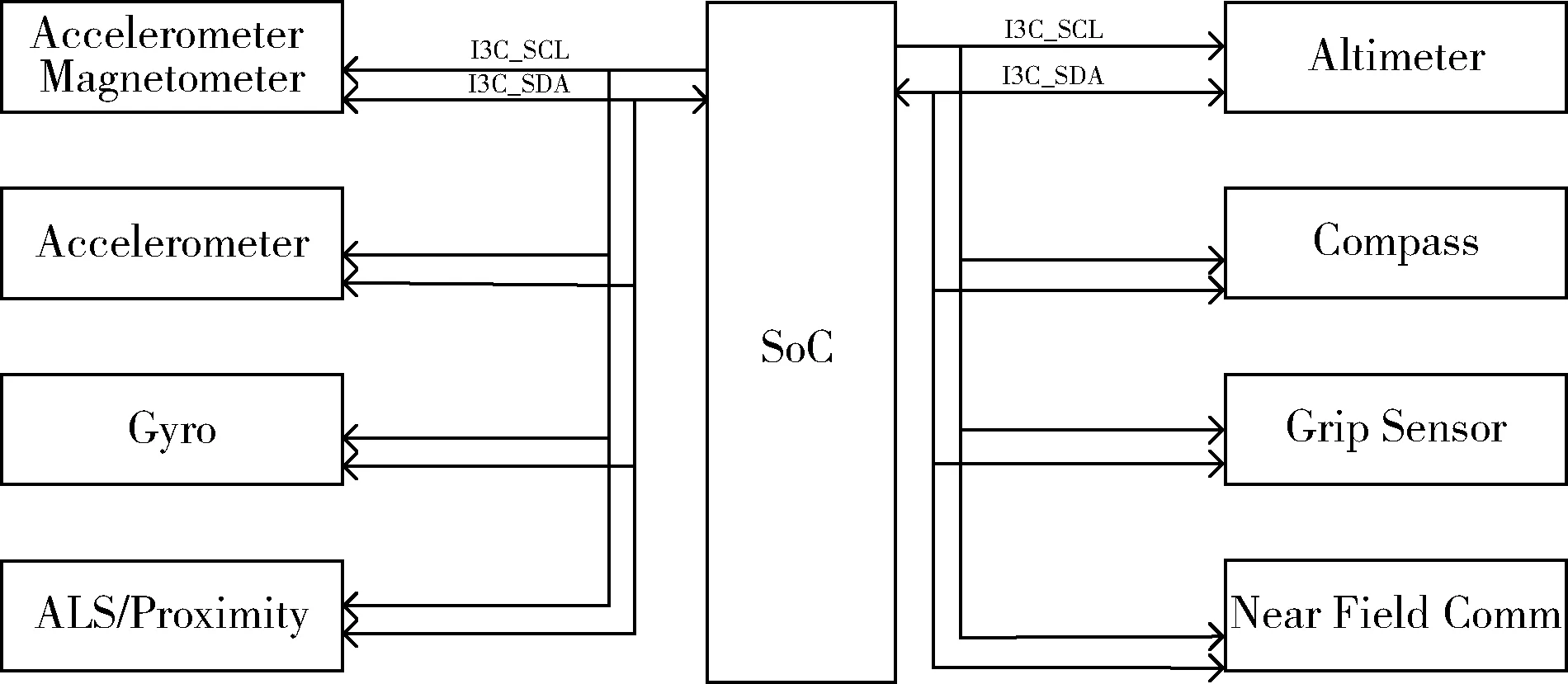

I2C 的广泛应用已经不言而喻,但它也存在两大缺陷:首先,它的速率受到限制,在标准模式下,它的速度只有400 kHz,无法满足一些高性能的应用场景;其次,它的功耗也比较大,因为SCL 和SDA 都需要接上拉电阻,而这会导致I2C 的功耗过大,无法满足当前更加严格的嵌入式系统要求。随着传感器数量的不断增加,I2C 的瓶颈也越来越明显,它需要额外的GPIO 连接到SoC 上,这就导致了中断(INT)、芯片选择以及使能脚等都需要额外的GPIO,如图1 所示,进而使得主机封装引脚和更多 PCB 层的系统成本也随之增加[5]。

图1 I2C 接口框图

MIPI I3C 在改善I2C 的缺点方面做出了巨大的贡献,它将I2C 和SPI 的关键属性整合在一起,不仅可以达到12.5 MHz 的速度,更重要的是它具有内中断功能,可以动态地址分配,只需要SDA 和SCL 两条线,而不需要额外的中断(INT)等连线,如图2 所示,实现了高速和简洁的目的,而且它还可以向下兼容I2C 设备,使得I2C 可以平稳地过渡到I3C,从而大大提高了系统的可靠性和可用性。与I2C 的开漏模式相比,I3C 的SCL 采用了推挽技术,而SDA 也大部分时间采用了这种技术,因此,它的功耗大大降低了[2]。

图2 I3C 接口框图

2 I3C 协议关键特性

I3C 协议提供了一套强大的通用命令代码(CCCs),支持全局的命令操作,不仅可以直接传输(Direct CCC)到特定的 I3C 从设备,也可以同时传输(Broadcast CCC)到所有I3C 从设备。通过这些命令字实现动态地址分配、检查当前总线状态、时间控制、IO 扩展等功能。整体功能比I2C 有着全面的提升[6]。

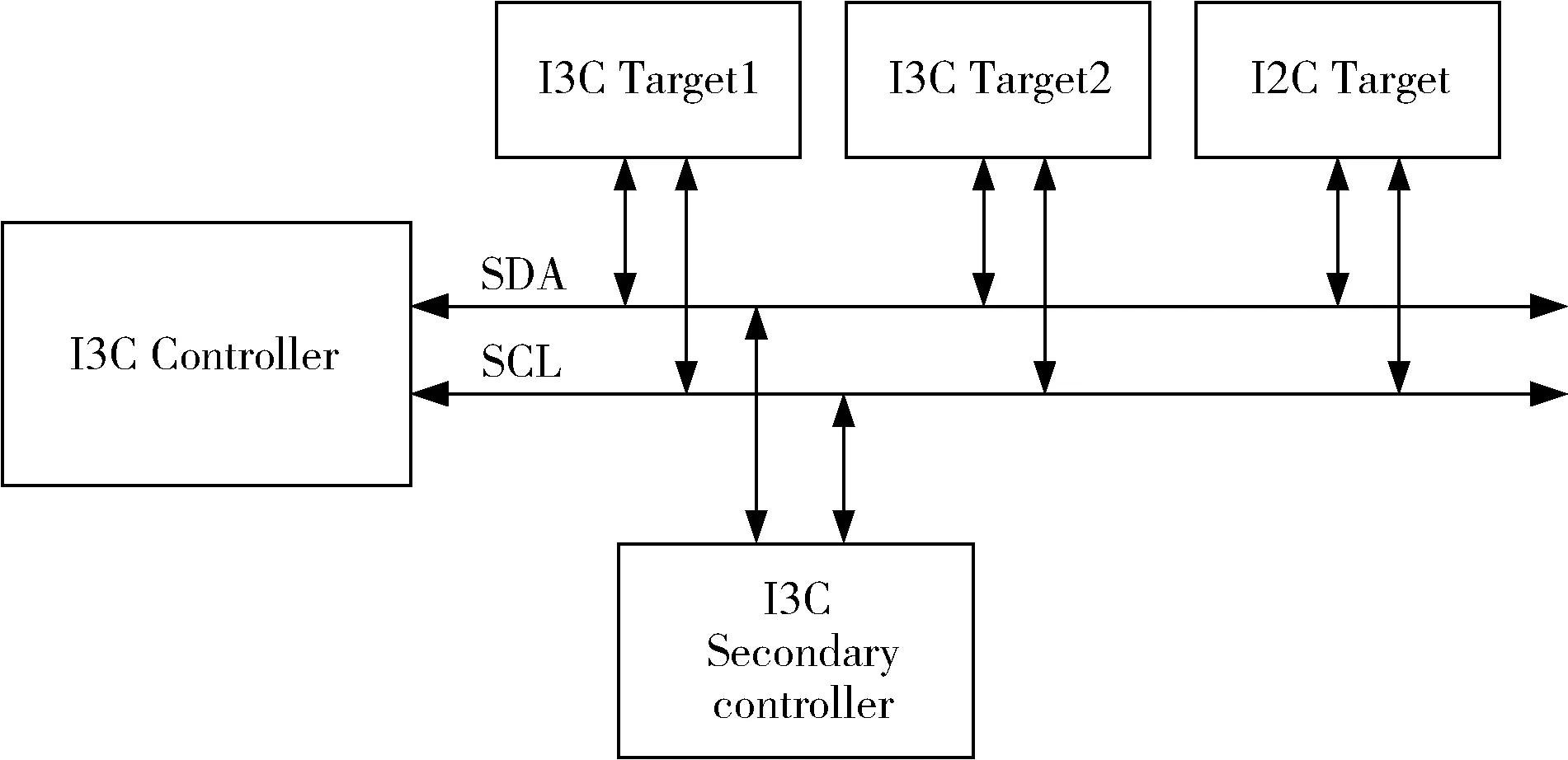

I3C 协议支持多主机配置,总线上可以同时拥有一个主机和多个次要主机,当前主机可以通过通用命令代码(CCC)将控制权传递给总线上的次要主机,使其成为当前主机,具有双重角色的I3C 设备不能同时作为主机和从机,必须配置为其中一个,当前主机角色只能配置一台设备为主机,即当前主控制器(I3C Controller),总线上可以拥有一个I3C Controller 设备,多个I3C Target设备,遗留的I2C Target 设备以及I3C Secondary Con‐troller 设备。在总线上,可以支持多种混合类型的消息,例如传统的 I2C 从设备和消息,I3C 单数据速率(SDR)模式,包括两种内置广播信息和直接信息,以及高数据速率(HDR)模式,由于SDR 是I3C 的主要模式[2],本文将重点介绍I3C 的SDR 模式及其动态地址分配过程,而不对HDR 模式进行过多的探讨,混合系统如图3 所示。

图3 I3C 总线上的混合系统

SDR(Single Data Rate)模式是I3C 的主要协议模式和默认模式,它严格遵循I2C 规范,也可以用于进入其他模式、子模式和状态,并且可以通过内置功能,如通用命令(CCC),带内中断以及通过动态地址分配从I2C 到I3C 的传输。

所有的I3C 通信都是以帧的形式发送,每帧始都包括开始位、地址头、数据和停止位。开始位之后的地址头用于总线仲裁。主设备使用地址头来寻址从设备。从设备可以将地址头仲裁用于多种目的,包括带内中断、热连接和主控制权请求功能,以满足不同的需求。地址头(HEADER)的地址为7′h7E,也是广播地址,所有I3C 从设备都应匹配地址值7′h7E。I2C 从器件不会匹配地址7′h7E,因为该值在I2C 中保留并未使用。地址头的地址与从设备的动态地址进行匹配(由 I3C 主设备分配),所有I3C 从设备只匹配广播地址和自己的动态地址[3],而未匹配的I3C 从设备则等待重复开始位或停止位,确保总线上的所有从设备都能够正确地接收到来自主设备的消息,I3C 通信的启动过程如图4所示。

图4 I3C 的通信过程

3 I3C Controller 架构设计

在详细解读MIPI I3C v1.1.1 基础文档后,采用数字IC 芯片自顶向下的设计方法,将I3C 控制器系统主要分为APB 接口模块、寄存器模块、状态机模块以及I3C 总线接口模块四大模块,如图5 所示。并使用Verilog HDL代码对各个模块进行编写并实现I3C 控制器的基本功能。本文基于协议文档,实现的功能点包括I3C 地址仲裁检测;动态地址分配,I3C Target 的SDR 通信模式,产生起始、终止以及应答信号等,支持CCC 的大部分指令,并且能够与遗留的I2C 设备通信。下面将分别介绍各个模块的设计。

图5 I3C 控制器架构设计

3.1 apb_i3c_biu 模块

APB 接口模块采用APB (Advanced Peripheral Bus)总线,是ARM 架构中的一种常用的总线标准,它可以有效地将处理器和外部设备连接起来,具有轻量级、低功耗、低复杂度等优点[7]。作为一个点对点的总线结构,每个外设都有一个独立的APB 总线接口,同时处理器也具有一个APB 总线接口。这个总线接口可以提供高效的数据传输,同时也可以实现周期控制和数据同步等功能。并且采用了分时复用的方式,可以实现多个外设同时使用总线的功能,从而提高了总线的使用效率[8]。本文所介绍的I3C 控制器采用APB 的配置方式,控制器工作时,使用APB 接口配置I3C Controller 的寄存器,决定I3C 的工作模式,并且向寄存器中写入需要传输的数据。

3.2 apb_i3c_regfile 模块

寄存器模块作为重要的组成成分之一,包含着大量的寄存器,用来寄存I3C Controller 的各种状态信息、控制信息和配置信息,对于芯片的正常运行和调试都十分重要。以下是I3C Controller 的寄存器模块实现的一些重要功能:

(1) 启动控制器开始工作;

(2) 寄存传输的数据以及配置数据传输模式,分为三种,分别是与I2C Target、I3C Target 以及CCC 配置模式;

(3) 寄存广播地址7′h7E、Target 地址以及可供分配的动态地址;

(4) 寄存接收来自Target 的数据,可通过apb 读操作读取。

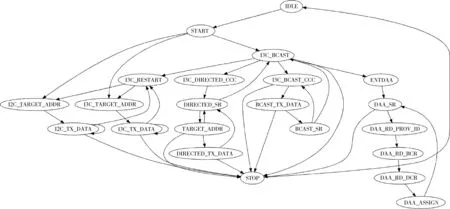

3.3 apb_i3c_mstfsm 模块

状态机模块用于控制芯片内部的状态转移和数据传输,由于I3C Controller 所能实现的功能比较多,因此包含了大量的状态转移,该模块通过标准的三段式状态机实现,可以大大简化芯片设计和调试的复杂度,提高芯片的性能和可靠性。基于MIPI I3C 协议,状态机模块设计如图6 所示,根据设计通路分类,包括了动态地址分配状态机、广播地址CCC 状态机、直接地址CCC 状态机、数据传输状态机。

图6 I3C Controller 状态机

3.4 apb_i3c_if 模块

I3C 总线接口模块、是I3C Controller 的核心模块,控制器在状态机的控制下通过该模块驱动总线时钟SCL和数据SDA 的数据传输,以奇偶校验的方式产生T-bit响应信号,实时检测总线上的开始、停止以及响应等信号,并且在该模块中进行推挽与开漏模式的切换,寄存器中的数据信息以及时钟频率控制等信息也通过状态机模块传输至总线接口模块。

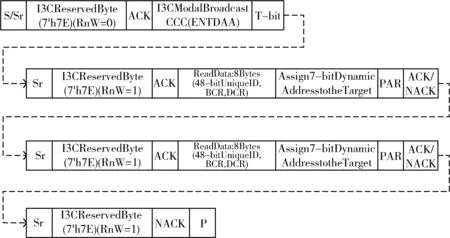

4 动态地址分配过程

I3C 控制器每次从断电状态启动时,主控制器会为总线上的各个设备分配唯一的动态地址,此过程包括了类似I2C 的地址仲裁程序,不同之处在于I3C 使用48 位临时ID 和设备的I3C 特性寄存器(即BCR 和DCR)的值进行串级。具有最低级联值的I3C 总线上的设备依次赢得每个仲裁轮次,并且主机为每个获胜设备分配唯一的动态地址。动态地址仲裁使用OD 模式,当Controller 处于可配置状态时,需要获取Taeget 的相关信息,具体过程如图7 所示。Controller 启动发送广播地址7′h7E/W后,检测总线上Target 发送的响应信号,然后发送广播命令CCC(ENTDAA)+T-bit 奇校验位,接着发送RESTART+广播地址7′h7E/R,这样总线上没有被分配动态地址的I3C 设备都对广播地址进行ACK。主机仅仅控制SCL 线,释放SDA 线成高阻态,这样允许Target通过推挽输出驱动SDA 为高电平,每个I3C 器件都会对广播地址进行响应,在SDA 上驱动传输各自的48 bit 临时ID 和特性寄存器信息,根据仲裁规则,如果设备拥有的临时ID、BCR、DCR 值最小赢得地址仲裁。Controller向赢得仲裁的Target 使用开漏方式发送7bit 的动态地址和校验位,Target 响应后则继续给未分配动态地址的设备分配动态地址,直到发送RESTART+广播地址7′h7E/R后没有其他I3C 设备ACK,则STOP 退出动态地址分配过程。

图7 动态地址分配传输过程

5 UVM 验证与板级验证

UVM(Universal Verification Methodology) 是一种用于集成电路验证的验证方法论,能够帮助检验设计功能的正确性[9],本文基于该方法构建了I3C Controller 的许多用例来测试RTL 是否符合预期的工作,其测试平台框架如图8 所示。测试平台中模拟了I3C 的Target 设备,并且通过APB 接口的方式输入测试激励来控制测试主机。图9 是通过UVM 测试的几种波形图,其中(a)和(b)是动态地址分配的过程,I3C Controller 按照时序要求发送CCC 指令,读取Target 的临时ID、BCR、DCR 信息,把动态地址写入I3C Target,从而通过动态地址进一步与I3C Target 进行通信,如图9(c)所示。

图8 I3C Controller 验证平台框架

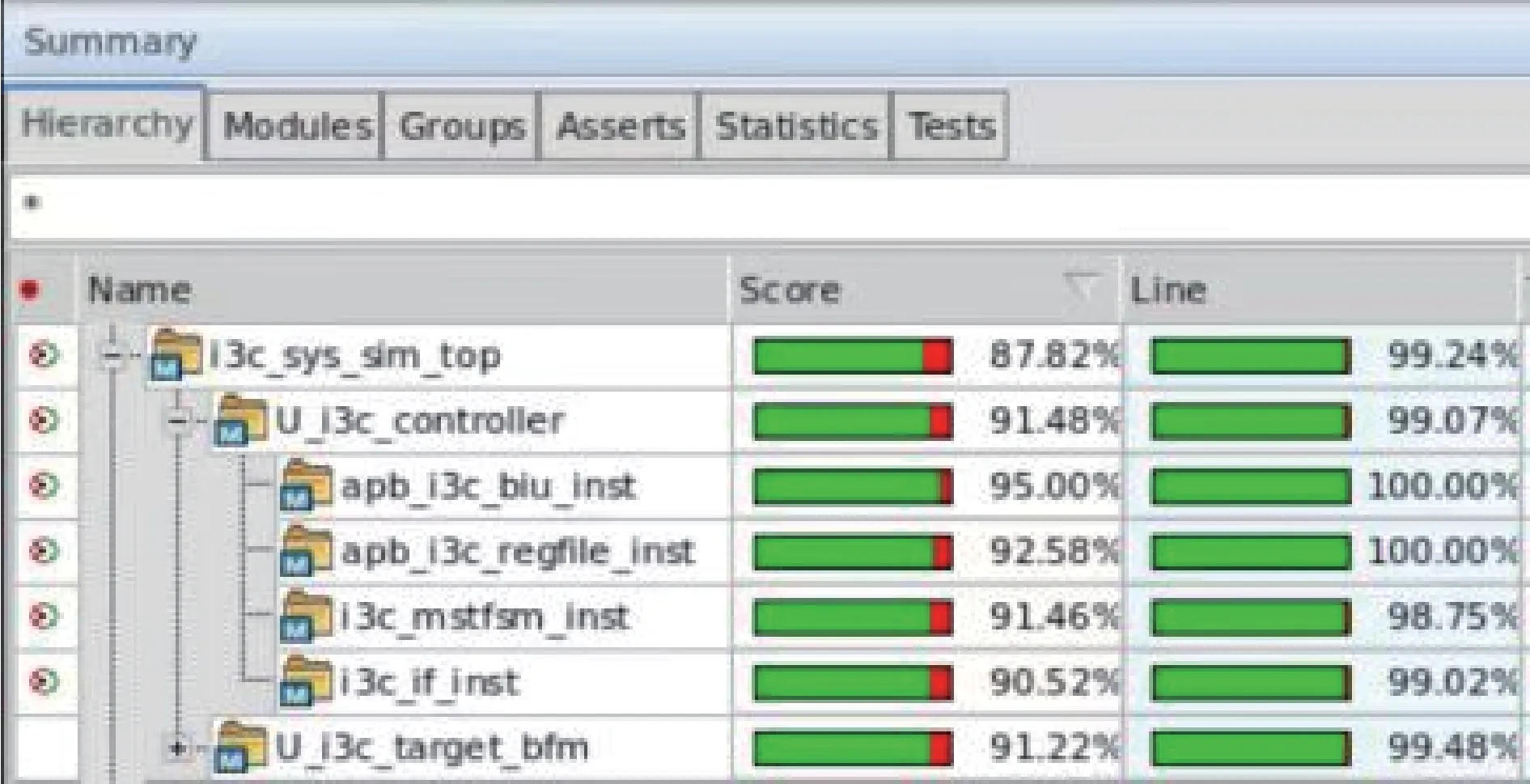

此外,通过UVM 验证,测试了I3C Controller 设计的所有通路,都满足工作需求,最终通过用例回归和覆盖率分析的结果可以看出,总的行覆盖率已经达到99.24%,如图10 所示。这不仅表明从应用场景和代码覆盖率上验证的充分性,也证明了I3C Controller 的RTL设计的正确性得以较好的保证[10]。

图10 覆盖率分析

6 结论

本文基于MIPI I3C 协议,首先介绍了I3C 协议的背景和细节以及与I2C 协议相比的优势,然后详细介绍了本文提出的可用APB 接口配置的I3C 控制器的设计,通过实现该控制器,证明了其能够有效地支持I3C 协议,并且介绍了设计验证过程,通过这些验证步骤,验证了设计的正确性和可靠性。

总之,本文提出的基于SOC 芯片的I3C 控制器,具有良好的性能、正确性和可靠性。设计的不足之处在于未能实现协议中所有的功能,未来的工作将进一步优化该控制器,使其能够更好地应用于实际场景中。由于MIPI I3C 协议是一个相对较新的协议,其制定的时间不久,相关的研究和应用尚处于起步阶段,因此本文介绍的内容对于未来的I3C 的广泛应用和学习具有一定的参考价值。