硅基量子点激光器研究进展

2023-12-04谢启杰纳全鑫骆登峰贾思琪

张 楠,谢启杰,纳全鑫,骆登峰,,贾思琪,王 恺

(1.鹏城实验室,广东 深圳 518055;2.南方科技大学 电子与电气工程系,广东 深圳 518055)

1 引言

思科年度互联网报告回顾与预测了全球互联网采用率、连接设备激增和网络性能,从2017 年到2022 年,全球消费者互联网流量增长了四倍,年复合增长率为31%,到2022 年将达到每年4.8泽字节(1 ZB=1.181×1021B),或每月396 艾字节(1 ZB=1 024 EB);预计到2023 年底,全球固定宽带的平均速度将为110 Mbps[1]。不断增长的带宽需求极大地挑战了信号处理系统,特别是在数据中心和高性能计算系统中,高速、大带宽和低功耗是至关重要的问题。面对这一飙升的全球需求,研究者们正在努力开发更高的数据速率技术来处理负载。然而,传统的硅基信息技术正逐渐饱和,对极快的处理速度和巨大的数据容量的需求呈指数级增长。如今,硅基晶体管的特征尺寸在摩尔定律的要求下已经步入了5 nm 以下,进一步缩小尺寸将带来短通道效应、高能耗、热耗散等一系列瓶颈[2]。在该背景下,硅基光子集成电路(Si-PICs)被提出用于催化强大的新技术,其光学有源和无源组件全部单片集成在一个芯片上,具有高带宽密度、高能效和低延迟等优点。

Si-PICs 能够利用成熟的互补金属氧化物半导体(CMOS)技术,并允许以低成本大规模生产,形成了在半导体工业制造体系中的独特优势。基于Si-PICs 的应用,可将其从网络数据通信扩展到传感技术,如车载激光雷达和生物传感器等;展望未来的技术,则包括集成量子技术、光学计算、基于人工智能(AI)的技术和神经网络光子学等。在过去的几十年里,Si-PICs 的关键组件取得了快速发展,包括高性能硅基调制器、光电探测器和波导。众所周知,激光器是传输数字信息流的收发器中的核心元器件,但目前的速度还不够快。然而,在过去二十年里,片上硅基激光器的不断发展展示了先进的设计特征,这些特征有助于满足全球对数据激增的需求[3]。理想的片上硅基激光光源应根据其应用情况满足上述需求。一般来说,片上硅基光源的工作条件是:(1)电泵浦连续波(CW)激光覆盖现代硅电子芯片,工作温度范围为-40~85 ℃;(2)低能耗运行,输出功率足够高,每千兆能耗低;(3)在电信和数据通信波段,如O 波段(~1 310 nm)和C 波段(~1 550 nm),与现有光纤网络无缝对接;(4)直接集成到兼容成熟CMOS 加工技术的硅基平台上进行大规模制造[4]。

虽然硅可以有效地传输、调制和探测光,但Ⅳ族半导体的间接带隙结构使其不具有良好的发光特性,硅光发射器的内量子效率仅有百万分之一。因此,硅基片上光源是光子学集成中最具有挑战性的元器件,长期以来一直是硅基PICs 的最后一个缺失的组成部分[5]。对集成激光光源的要求不仅包括光功率、阈值、泵浦源、稳定性等激光性能参数,还包括低成本、大批量生产。研究人员正试图探索不同的方法将激光集成到硅上。早期,通常采用片外Ⅲ-Ⅴ光源,采用边缘耦合或倒装芯片集成[6-7]。然而,这些方法限制了硅光子学的进一步扩展。在过去的20 年里,针对尺寸、成本和功耗方面的优势,人们开发了各种技术来获得高效的硅基激光器[8-9]。本世纪初的研究主要集中在用于增强光发射的硅材料,后来在2010 年代初转向Ge,最近转向GeSn 合金,因为直接带隙对于高效的室温激光运行至关重要[10-11]。此外,可以在有源层内掺杂稀土元素实现激光发射,这与掺稀土光纤激光器的思路类似。掺稀土硅基激光器具有低噪声、高热稳定性的优点[12]。与此同时,在硅上集成成熟Ⅲ-Ⅴ族激光光源的努力从2000 年代中期即已开始。异质集成方法包括晶圆键合和微转移印刷,经过研发,后来已被商业化[13-14]。但是,异质键合的方案受制于Ⅲ-Ⅴ族衬底的使用,限制了成本的进一步降低。利用直接异质外延生长法,在硅上集成Ⅲ-Ⅴ族半导体激光器的研究在2010 年代日益受到重视[5,7,15]。

在硅衬底上直接外延Ⅲ-Ⅴ族材料的方式适合大尺寸生长和大批量生产,是解决硅基光电集成缺少核心光源的理想方案。借助成熟且性能优异的Ⅲ-Ⅴ族半导体激光器,特别是硅片上量子点激光器,Si-PICs 的发展不仅将彻底改变光通信系统,还将彻底改变其他应用领域,如传感、成像、计量、量子计算等[16-20]。但是,受限于Ⅲ-Ⅴ族和硅材料的极性不同、晶格失配和热膨胀系数差异,在硅上直接生长Ⅲ-Ⅴ族材料会出现反相畴、穿透位错和微裂缝等材料缺陷问题,进而会对器件寿命和工作性能产生严重影响[21]。该研究方向的发展是由两个因素推动的。首先,量子点(Quantum dots,QDs)被证明对晶体缺陷更耐受,因此有望提高在硅上生长的激光器的器件可靠性[22]。其次,设计了新的生长方案——在硅上制备低穿透位错密度甚至无穿透位错的Ⅲ-Ⅴ族半导体[23-25]。同时,为了发挥量子点在硅基半导体激光器中的独特优势,在硅上集成量子点激光器,也已经开发出了三种方法:芯片晶圆键合、倒装键合和直接外延生长。上述集成方法通常都克服了其他集成方法的一些问题,但仍面临各自独特的挑战[26]。本文将综述基于以上三种方法的硅基Ⅲ-Ⅴ族半导体量子点激光器的最新研究进展,并对其未来前景和挑战进行探讨。

2 量子点材料及量子点激光器

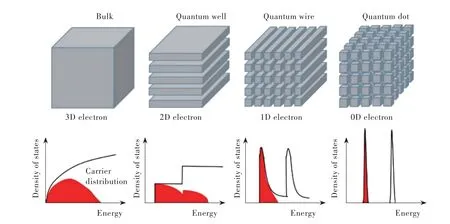

基于Esaki 和Tsu 于1970 年在美国IBM 公司提出的超晶格理论,Arakawa 和Sakaki 于1982 年在理论上首次预言了量子点激光器[27],并对量子限域作用和温度不敏感性都做了讨论;通过将量子阱激光器置于强磁场中,实验验证了阈值电流的三维约束效应。体材料半导体中的电子在三维空间中自由移动,它们的能量分布由态密度和费米-狄拉克分布函数决定。图1表示不同维度限制的材料和对应的电子态密度函数关系。如果量子点的最低两个分立量子能级的能量差大于几倍的kT(室温约26 meV),那么就不会出现增益函数的热依赖特性,因此也不存在激光发射波长的热依赖特性,从而表现出极好的温度稳定性,不会导致因激光器随工作温度升高而造成的性能退化[28]。在半导体激光器中,随着温度的升高,费米-狄拉克分布函数发生变化,导致增益谱的最大值(即峰值增益)减小。为了保持激光发射条件,需要增加载流子密度,导致阈值电流增加。如果电子被限制在三维纳米结构(即量子点)中,由于空间分离,尽管费米子的性质不同,但是所有的电子都可以被填充在相同的能级上。峰值增益不会随温度的升高而显著降低,因此量子点激光器的阈值电流对温度不敏感。另外,由于增益谱窄,阈值电流密度本身在量子点激光器中也大大降低。综上可知,在理论上量子点激光器相比于量子阱激光器,可以获得更低的阈值电流密度,还能提升半导体激光器的温度性能。

图1 用于半导体激光器的半导体纳米结构演变过程示意图Fig.1 Scheme of semiconductor nanostructures evolution process for semiconductor lasers

2.1 量子点的优点

在半导体激光器的增益区使用量子点的五个主要原因[29]:(1)较高的工作温度,(2)较低的线宽增强因子和减小的线宽,(3)降低反射灵敏度,(4)改善锁模,(5)降低对缺陷的敏感性。随着现代量子点工程技术的出现,Ⅲ-Ⅴ族半导体激光器可以通过量子点独特的量子限域效应来进一步提高其性能。纳米结构的半导体量子点被限制在德布罗意波长量级的所有三个维度上,通常为7~70 nm[30]。由于载流子动量的限制,量子点中的所有可用能态都以离散状态存在,这导致了类似于Delta 函数的态密度。因此,这种有效的载流子局部化降低了电流密度,获得了比量子阱激光器更低的阈值电流[22]。此外,量子化态密度中电子的热能分布显著降低,这使得量子化态密度与其他高维结构相比对温度不敏感。实验表明,在GaAs衬底和Si 衬底上的量子点激光器的最高工作温度分别高达220 ℃和130 ℃[31-32],远远超出了数据通信和电信应用的要求。一般情况下,数据中心的典型工作条件是80 ℃左右。最后值得一提的是,InAs 量子点的发射波长适合硅材料,避免了硅波导的带边吸收[20]。

2.2 量子点的生长

量子点的概念在1982 年首次从理论上提出后[27],直到1994 年才通过Stranski-Krastanov(S-K)生长方法报道了半导体量子点的实验验证[33]。虽然当时并不清楚激光发射实际上是否归因于量子点的增益,但该报告是朝着实现具有三维量子限制效应的高性能量子点激光器迈出的关键一步。在此之后,量子点激光也被世界上不同的研究小组相继报道。S-K 生长模式适用于晶格失配较大、但表面能与界面能不是很大的异质结材料体系。S-K 生长由逐层生长开始,以二维层状生长模式,在达到一定临界厚度时,外延生长由二维层转变为三维岛状生长以松弛应变降低能量。在三维岛状生长初期,形成的纳米量级尺寸的小岛周围是无位错的。若用禁带宽度大的材料将其“包裹”起来,小岛中的载流子则会受到三维限制,由此形成的量子点形状通常是透镜形或截断的金字塔形。在生长的单层量子点材料基础上,重复上述生长过程,可以得到量子点超晶格结构。在量子点超晶格结构中,每层量子点是垂直对准或是斜对准,依赖于量子点层间隔势垒层的厚度,以及量子点顶层应力的分布[34]。

量子点生长主要是通过外延沉积方法实现的,如分子束外延(MBE)和金属有机气相外延(MOVPE 或MOCVD)。为了实现自组装,需要大幅度改变二维层生长所建立的生长条件。首先,在外延层和衬底之间存在数个百分点的晶格不匹配是先决条件。其次,与最好的量子阱生长相比,必须显著降低生长温度。温度直接控制量子点特性:较低的温度导致更大的密度和更小的尺寸,这是由于生长表面上较短的原子扩散长度;而较高的温度可能由于较大的晶格不匹配,导致出现三维生长的缺陷层。对于量子点在半导体激光器中的应用,为了增加增益材料的填充因子,应获得尽可能大的量子点密度。与二维薄膜相比,任何量子点结构的填充因子本质上都非常小。此外,这些量子点也应该相当小,用以显示预期的量子局域化效应,这两个特征都要求较低的生长温度。总之,量子点生长温度具有一定的区间,较高和较低都会对量子点的生长质量产生消极影响。

半导体激光器结构由许多外延层组成,其中大多数都需要较高的生长温度才能获得最佳的材料性能。为了在覆盖层的生长过程中不破坏量子点,在沉积量子点后的生长温度应该保持在较低的水平,直到外延层生长过程结束。这可能与其他需求和设计规则相冲突,特别是对于高质量波导层的生长或优化外部阻挡层的掺杂。因此,必须特别注意量子点激光器外延生长过程中的温度分布。

2.3 基于GaAs 衬底的InAs 量子点

GaAs 上的InAs 量子点已经成为自组装量子点和半导体激光器的主要材料体系。由于GaAs和InAs 之间晶格失配约7.1%,可以很容易地建立S-K 生长模式。此外,通过形成三元合金In-GaAs,可以在大范围内调整失配,从而实现对应变与自组装量子点发展之间相关性的基本研究。最后,在量子点研究开始之前,这种材料体系已经是大多数MBE 设备的首选材料,而其他材料如磷化物或氮化物则存在特殊的生长条件。

在研究早期,科学家们长期认为基于零维系统材料的许多基本性质可以很容易地用量子点来研究,量子点的外延生长就像量子阱一样容易。当然,人们期望这种量子点激光器能显示出科学家多年前预测的所有优异特性。然而,这些希望并不能完全实现,特别是在研究生长温度高于低温的设备时。这主要是由于固有的量子点密度大小分布。另一个原因可能是有限的量子点电位深度,电子和空穴态的量子化能变得相当大。此外,这些量子点在压缩应变下生长,将载流子进一步转移到更高的能级。载流子的热逃逸仍然是大多数量子点激光器的主要问题之一,当器件温度升高到300 K 或更高时,载流子的热逃逸会导致非辐射损耗的大幅增加,从而导致阈值电流的大幅增加。因此,一个非常高的接近无穷远的特征温度作为基于零维材料的理想预期值,通常在低温下测量而获得[35],并不能在室温附近实现。生长温度通常是最关键的参数,对于实现窄带光致发光且具有高增益的量子点,其生长温度的最佳公差应小于5 ℃。生长过程中的最佳温度与V/Ⅲ族原子比有很强的耦合关系,因此它们必须一起优化。其他通常采用的条件是使用As4代替As2,实施生长中断[36],以及“In-flush”步骤[37],其中通过优化覆盖层的厚度以及在580 ℃进行短暂退火来消除量子点的不均匀性。在In-flush 之后,应保持较低生长温度,以尽量降低进一步的相互扩散,从而减少蓝移。该研究中的器件利用由In0.15Ga0.85As量子阱非对称地围绕InAs 量子点组成的阱中量子点的有源区,其下面是2 nm 的“预层”,顶部是5 nm 的“覆盖层”。这些功能层的生长条件对发射波长和非均匀展宽有很大的影响。

自组装量子点不仅仅是从二维和一维结构(量子阱和量子线)上的三维到零维的逻辑步骤,它们还可以被视为一种新型材料。在晶格不匹配材料的正常二维薄膜生长过程中,薄膜在衬底上以伪态应变生长且无缺陷,仅达到由内应变能定义的临界厚度[38]。然后,该层通过形成高密度缺陷而产生弛豫过程,并变得不适合大多数应用。例如,将GaAs 上Ga1-xInxAs 中的In 含量x限制在约15%以下,从而使激光器的发射波长限制在约1 100 nm 以下。通过形成自组装量子点,可以克服上述限制,将1 300 nm 及以上的电信波长区域开放给生长在GaAs 上的材料。GaAs 是技术上发展最好的半导体材料之一,因此也是化合物半导体最重要的衬底之一。InAs 量子点激光器被认为是GaAs 晶圆上最有前途的用于通信的半导体激光技术,InGaAsN 结构通过在InGaAs 量子阱中合金化少量氮来降低晶格失配引起应变。如今,量子点激光器不仅在阈值电流或输出功率方面与量子阱激光器竞争,而且还可以覆盖量子阱难以达到的发射波长区域。

2.4 量子点激光器在Si-PICs 中的应用

Si-PICs 有望成为量子激光器的主要应用领域。由于安装大规模集成(Large-scale integration,LSI)电路芯片的硅光学中间体无法避免LSI 产生的热量,因此有必要集成在高温环境下也能工作的激光光源。如前所述,使用可以在高温环境下运行的量子点激光器,加上其自身的低功耗,为这个问题提供了解决方案。在日本于2011 年启动的FIRST 项目中,首次演示了通过混合倒装芯片键合实现的集成量子点激光器阵列的硅光子中间体。硅光子中间体在25~125 ℃的宽温度范围内实现了12.5 Gbps 的无差错传输和15 Tbps/cm2的高传输带密度,无需对激光器、调制器和光电探测器进行任何温度控制[39]。由于量子点激光器对光反馈效应不敏感,从而可以在没有任何光学隔离器的情况下实现硅光子芯片[40]。在这些成就的基础上,2017 年日本成立了一家名为AIO-Core 的公司,提供集成量子点激光器的5 mm2发射/接收硅光子芯片。

3 基于晶圆键合技术的硅基量子点激光器

晶片键合是在硅衬底上形成量子点半导体激光器的最有前途的方法之一。目前,已经有多种键合技术(如金属扩散键合、直接分子键合和粘合剂键合等)应用于硅基上的各种激光光源,包括法布里-珀罗(FP)激光器、分布反馈(DFB)激光器、微盘/环激光器、可调谐激光器、多波长激光器、锁模激光器等,量子点半导体激光器也是其中之一。

3.1 金属扩散键合

金属扩散键合是在热和压力下将两个晶圆与金属层结合在一起的方法。该方法受晶圆表面结构和粗糙度的影响不大,并且可以使用中间金属作为电极,因此备受关注。在金属层中存在光反射的缺点,但同时具备金属条纹部分键合等结构性解决方案。该键合技术基于键合界面处金属的相互扩散,构筑固体金属层,有效地融合了两个初始金属表面之间的原始键合界面。已有的金属扩散键合技术中,最常见的是热压键合,即金属间扩散发生在固相和固液相互扩散键合中,两种不同相的金属相互扩散,最终形成固体金属化合物。

对于金属晶片键合,有报道采用MOCVD 或MBE 方法在GaAs 衬底上生长了InAs/GaAs 量子点激光器结构。形成的InAs 量子点的面密度为(4~6)×1010/cm2,InAs 量子点的层数为5~10 层。量子点有源层位于1.4 µm 厚的Al0.4Ga0.6As 覆盖层之间,量子点的基态中心波长为1.27~1.30µm。该研究在量子点激光器GaAs 衬底上利用中间金属AuGeNi/Au/AuGeNi,与AuGeNi 金属层在硅片上成功地实现了键合[41]。这种金属结合层利用Au-Ge 合金的低共熔点(280 ℃)提高了结合强度和界面导电性。晶圆被切成1 cm2的面积。两个晶圆在空气中接触,温度为300 ℃,单轴压力为0.1 MPa,接触时间为3 h。然后在室温下用H3PO4-H2O2(体积比3∶7)选择性蚀刻去除GaAs 衬底。用HCl 溶液去除Al0.7Ga0.3As 刻蚀停止层,然后在结构的顶部和底部分别施加电极制备FP 量子点激光器。该器件由厚度为3.45 µm 的双异质结激光结构组成,通过厚度为380 nm 的金属层结合在Si 衬底上。激光器的腔长为2.4 mm,宽为100 µm,未使用高反射(HR)涂层。

3.2 直接键合

直接键合是一种不使用中间金属和氧化物的直接键合硅晶圆和激光晶圆的方法,该方法可以通过异质界面获得电流通路,有利于Ⅲ-Ⅴ族半导体光源在Si 衬底上的集成,所有键合工艺均可在300 ℃或更低温度下进行,不会出现Si 器件杂质扩散等问题。这种硅光子光源集成工艺技术更适合CMOS 工艺。

在2012 年,Tanabe 等提出了一种直接熔合技术[42],通过异质界面能带工程来提供与掺杂浓度相关的高导电性和透明性的异质结。这种直接键合方法过程如下:(a)激光器和硅片上的光刻胶涂敷;(b)切割激光器和硅片;(c)光刻胶去除(浸泡、丙酮);(d)自然氧化物去除(湿法化学刻蚀,HF);(e)用于键合表面的臭氧灰化;(f)晶片键合;(g)GaAs 衬底去除(湿法化学刻蚀,H3PO4+H2O2);(h)去除AlGaAs 刻蚀停止层(湿法化学刻蚀,HF)。上述实验步骤中,GaAs(100)和Si(100)晶片的键合表面涂有光致抗蚀剂,以保护这些表面免受划线过程中产生的颗粒的影响。将晶片切成两块,每块面积为1 cm2,用丙酮去除光致抗蚀剂并对粘合表面进行脱脂。使用 HF 溶液去除GaAs 和Si晶片上的原生氧化物。两个管芯与对齐的(011)边缘接触,这有利于激光制造中的切割过程。再将GaAs/Si 样品在300 ℃的空气环境中以0.1 MPa的单轴压力退火3 h。使用直流偏置源测量键合GaAs/Si 界面的I-V特性,并在键合GaAs/Si 样品的外表面施加AuGeNi/Au 欧姆接触,获得在GaAs/Si界面处一层厚度约为2 nm 的非晶层。在300 ℃下形成了无金属和无氧化物的GaAs/Si 欧姆异质结,温度低到足以抑制活性材料的退化。此外,该研究分别采用p-GaAs/p-Si 和p-GaAs/n-Si 键合的方法,在硅衬底上制作了阈值电流密度很低的1.3µm InAs/GaAs 量子点激光器和AlGaAs/Si 双结太阳能电池。

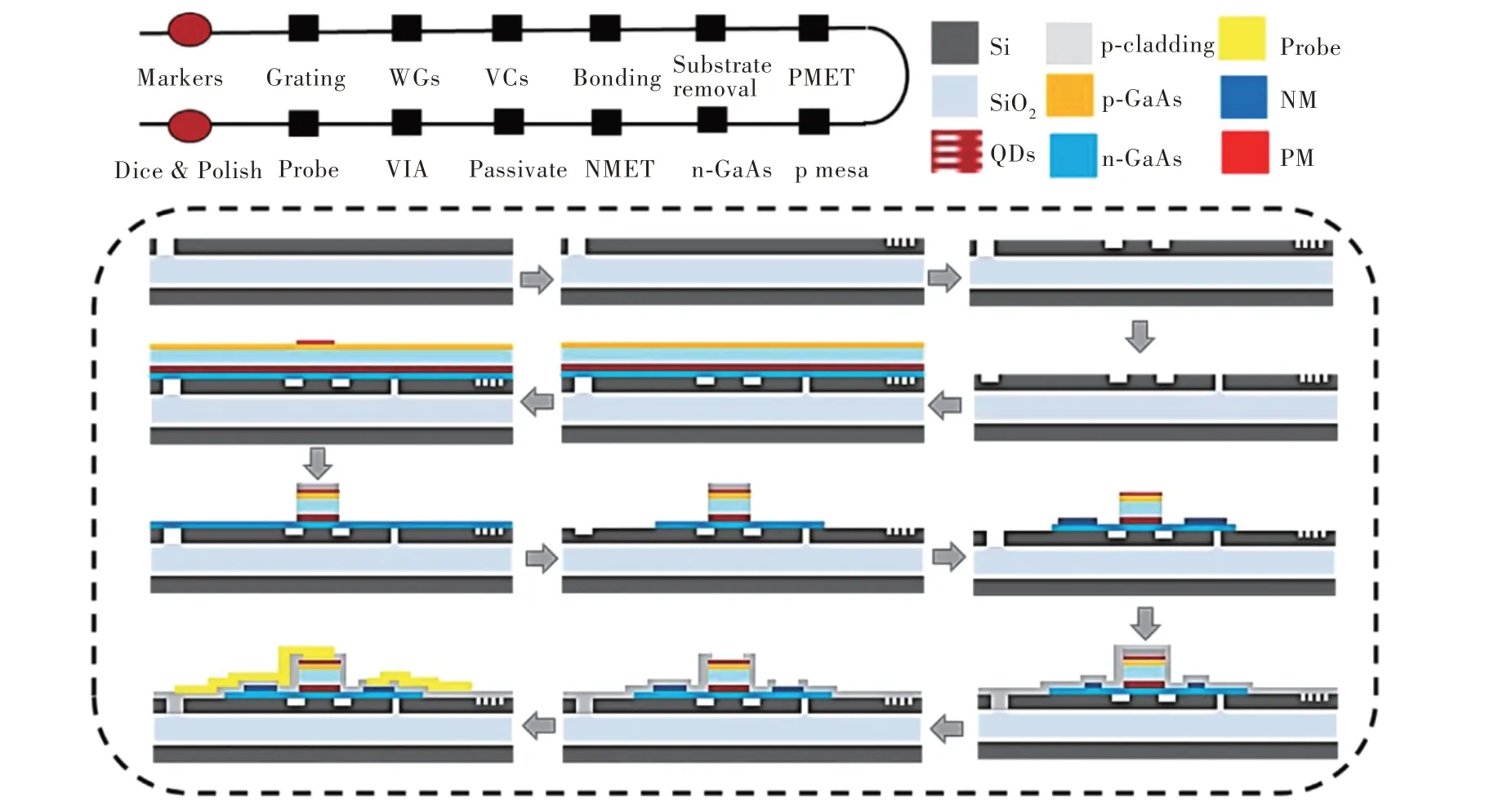

虽然在硅上外延生长量子点已经取得了很大的进展,但功能器件将光子波导限制在Ⅲ-Ⅴ层,并且Si 被简化为单纯的衬底。万雅婷等在2021年的报道中,解决了关于硅基外延激光器和硅光子波导之间关系的一系列问题[43]。通过将先进的硅光子学和优越的量子点材料结合起来,实现了向高容量集成的转变,在硅上实现了创纪录的量子点DFB 激光器,并实现了与硅波导的高效光耦合。整个层结构从上到下依次为(制造流程如图2 所示[43]):500 nm 厚的Al0.8Ga0.2As 层,用于腐蚀停止的500 nm 厚的Al0.8Ga0.2As 层,400 nm 厚的n-GaAs 层,1.4 µm 厚的下层Al0.4Ga0.6As 包层,300 nm 厚的量子点有源区,中间夹着两个30 nm 的AlxGa1-xAs 梯度层,150 nm 厚的p-GaAs 层,以及抑制键合层缺陷扩展的10/10 nm GaAs/AlxGa1-xAs 超晶格区。在量子点晶片上沉积2 nm 的Al2O3后,采用O2等离子体辅助工艺进行晶片直接键合,然后在100 ℃、1 Mpa 的压力下进行18 h 的热处理以提高键合强度。接下来,在NH4OH∶H2O2的化学溶液中去除衬底,停在500 nm 的Al0.8Ga0.2As 层,然后用稀氢氟酸(≈2.5%)去除该层。在台面刻蚀后,侧壁表面先用12 nm 的Al2O3原子层沉积钝化,然后覆盖500 nm 厚的SiO2层,以完全隔离Pd/Ti/Pd/Au 和Pd/Ge/Pd/Au 金属接触堆叠的光学模式。在器件制造完成后,晶片被切开,通过机械抛光无源硅来形成发射面。

图2 硅上倏逝DFB 量子点激光器的制备步骤[43]Fig.2 The preparation steps of a passively mode-locked DFB quantum dot laser on silicon[43]

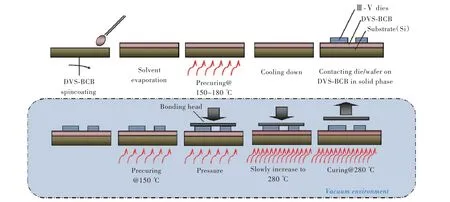

3.3 混合金属/有机粘合键合

一段时间以来,科研人员开发了一种采用金属键合技术与粘合剂键合技术相结合的混合键合技术。金属在键合界面处经过图案化处理后被选择性地应用——提供电接触,再凭借其良好的导热性进行晶片键合。此后,在键合界面处的间隙填充基于有机高分子聚合物的粘合剂,例如热固化聚合物。由此,两个晶圆通过加热固化完成键合过程。这种混合有机/金属键合方法的一个例子是金属键合和环氧树脂粘合剂键合的组合,即通过共晶焊接预先键合晶圆之后,再将环氧树脂注入到晶圆之间的间隙中。工艺过程如图3 所示[44],键合过程从清洗SOI 衬底和Ⅲ-Ⅴ芯片开始。SOI 清洁是通过将基底浸入标准清洁1(SC-1)溶液中15 min 进行的,该溶液包含体积比为1∶1∶5的氨水(NH4OH)、过氧化氢(H2O2)和去离子水,分别加热至70 ℃。在此之后,将 DVS-BCB∶均三甲基苯溶液旋涂到SOI 基底上。然后将SOI 基底在150 ℃下烘烤10 min,让均三甲基苯蒸发,然后将基板缓慢冷却至室温。最后,将SOI 安装在由Pyrex 玻璃(1 200 µm 厚,100 mm 直径)制成的载体晶圆上。同时,在键合之前,使用体积比为4∶1和1∶1 的HCl∶H2O 和H2SO4∶H2O2∶H2O 溶液,通过选择性湿法蚀刻去除Ⅲ-Ⅴ晶圆/芯片上的InP/In-GaAs 牺牲层。该过程从Ⅲ-Ⅴ模具表面去除颗粒和污染物。然后用去离子水冲洗Ⅲ-Ⅴ芯片,干燥并安装在SOI 芯片上。由于在所提出的方法中,芯片在室温下接触,因此可以轻松地将单个芯片拾取并放置到硅目标晶圆上。它们无需任何额外工具即可以500 µm 的精度手动对齐,或者可以使用倒装芯片机更精确地放置。之后,承载晶圆上的SOI 衬底被安装在传送夹具上并被装载到晶键合工具的处理真空室中。真空室被抽空(目标压力0.1 Pa)并以15 ℃/min 的升温速度加热到150 ℃(10 min),同时对Ⅲ-Ⅴ/SOI 堆栈施加压力。实际键合压力(Ⅲ-Ⅴ裸片单位面积施加的力)保持在200~400 kPa 的范围内。在150 ℃下对模具施加压力10 min 后,温度升高至280 ℃,升温速度为1.5 ℃/min。达到280 ℃后,模具在氮气气氛中在该温度下保持60 min。固化后,粘合样品冷却(以6~10 ℃/min)并从处理室中取出。然后通过使用HCl 的选择性湿法蚀刻去除Ⅲ-Ⅴ裸片的InP衬底,留下薄的Ⅲ-Ⅴ薄膜,其功能层键合到SOI裸片上,为进一步处理做好准备。这种混合高分子聚合物/金属键合在光子器件中得到有效应用,特别是在将Ⅲ-Ⅴ材料集成在SOI 衬底上的情况下,它具有良好的导热性以及与SOI 衬底良好的电接触的优点,通过金属接触/键合焊盘,使得底层硅参与载流子的注入和有效的散热过程。

图3 开发的“冷键合”工艺[44]Fig.3 The developed “cold bonding” process[44]

4 基于倒装键合技术的硅基量子点激光器

芯片之间的倒装键合组装是系统封装和集成的关键技术之一,该方法具有互连距离短、封装密度高、寄生电阻小等优点[45]。目前的倒装连接技术有焊料凸点倒装键合技术、热压倒装键合技术、热压超声倒装键合技术等。倒装芯片提供了优越的性能,并为具有高输入/输出性能的芯片提供了一种具有成本效益的互连技术。对于倒装芯片安装,需要接触凸点,以有效地将组件与基底的电、机械和热连接起来。Au 具有良好的导电性、导热性和良好的延展性,适用于接触凸点。另一方面,Au 沉积在Ⅲ-Ⅴ半导体上作为最终的金属化层,为作为接触材料的Au 提供了良好的兼容性。

热压键合是一种快速、简单、可靠的倒装芯片焊接方法,它需要由可延展材料制成的触点,例如由金线制成的凸起点,凸点位于基底或组件上。另一方面,最好使用相同材料的扁平触点作为键合材料。由于物质内部原子的热运动,当两个表面相互接触时,原子会相互扩散。如果施加一定的压力和温度,扩散过程将加剧,这就是热压键合的原理。在不液化接触材料的情况下,热压键合通过材料接触产生接头,提供可接受的机械强度、稳定性以及良好的导电性[46]。倒装芯片工艺涉及凸点下金属化,以防止焊料成分扩散到器件中,并实现与芯片顶部金属层的良好粘合。焊料凸点可以通过晶圆凸点工艺制造。焊料凸点的印刷和电镀是两种常用的方法。常见的焊接材料包括共晶SnPb、SnSb 和SnAg。印刷技术可以很好地控制焊料成分,并使各种焊料合金能够在晶圆上凸起。印刷通常更便宜,但电镀可以最小化间距。在电镀AuSn 凸点的情况下,典型的凸点直径为30~100 µm,高度为30~60 µm;可以实现直径为20µm 且最小间距为50 µm 的凸点[47]。

热超声波键合是利用热声效应,将基板芯片加热至100~150 ℃的摩擦焊接工艺。倒装芯片的焊盘横向移动,与衬底芯片的焊料凸起接触,形成特定的工作界面。超声波换能器施加的爆发力被瞬间激活。与热压键合相比,热量仅在接触界面产生,芯片内部不会产生热应力。热声键合通常用于热敏材料。此外,所需的键合力比前者小得多,芯片上几乎不产生机械压力应变,可以更好地保护芯片不变形或碎裂。从上述倒装键合的原理可知,目前对设备的可靠性、成本、性能以及体积大小要求日益增高,多数情况下需要用到倒装芯片键合以减小尺寸和提高性能。然而,倒装键合技术也存在缺点:在芯片上制作凸点的设备,材料价格昂贵,工艺复杂,良品率低于引线键合;键合点在芯片下方,键合的可靠性需要额外的步骤来检验;虽然凸点的制作方法众多,但是每种方法都有各自的优势和不足,需要根据自己的应用需求来选择凸点技术。因此,凸点技术的优化至关重要,它关系到倒装键合的稳定性和成本[46]。

倒装键合的半导体激光器组装方法主要有两种,一种是主动对准,另一种是被动对准。通过主动对准,可以实现精确定位;但对准时间长,对准位置难以确定。被动对准时间短、成本低,但是它需要高精度对准。为了通过倒装键合技术将半导体激光器被动对准到硅光子集成电路上,将半导体激光器的出光端面精确对准硅波导是非常重要的。图4(a)采用低成本硅光子集成的被动对准方法,对半导体激光器进行装配。硅光子集成电路制作完成后,制造了带有Si 对准标记和Si 基座的半导体激光器安装台,如图4(b)所示[48]。首先,为了形成波导面(图4(b-1)),通过干法刻蚀,将上包层和覆盖层向下去除到Si 衬底(图4(b-2))。其次,通过干法刻蚀,将Si 对准标记和Si 基座图案化到Si 基底上(图4(b-3))。最后,在Si 基底上形成电极(图4(b-4))。对准标记也制作在半导体激光器芯片上。图4(c)显示了半导体激光器芯片在安装台上的被动对准方法[49]。如该截面图所示,通过基板透射光使用红外相机图像进行视觉对准[50]。图4(d)是半导体激光器芯片上的标记与安装台之间的对准图像调整示例。如图4(e)所示,半导体激光器芯片和Si 衬底之间的水平偏差优于±0.5 µm。垂直定位由Si 基底制造过程确定,垂直偏差优于± 0.1 µm。

图4 (a)采用被动对准技术的半导体激光器装配方法;(b)半导体激光器安装台制造工艺流程;(c)半导体激光器芯片在安装台上的被动对准示意图;(d)半导体激光器芯片与半导体激光器安装台上标记物之间对准图像调整示例;(e)半导体激光器与Si 衬底之间测量的水平对准差[48-50]。Fig.4 (a)Laser assembly method using passive alignment technique.(b)Process flow of laser mounting platform manufacturing.(c)Schematic diagram of passive alignment of semiconductor laser chip on the mounting platform.(d)Example of alignment image adjustment between semiconductor laser chip and alignment marks on semiconductor laser mounting platform.(e)Horizontal alignment error measured between semiconductor laser and Si substrate[48-50].

倒装键合技术可以实现晶圆级集成工艺,但需要对用于异质集成的半导体激光器和硅光晶圆器件进行特殊处理,如在硅光晶圆上制作用于高度对准的特殊结构、波导耦合结构以及激光器的平坦化过程等,这些特殊工艺均会对最终产品良率产生影响,限制了该技术的发展。片间和片上倒装键合集成技术路线均依赖于高精度封装设备,其对于设备机械对准精度要求达到 0.5 µm量级,这导致该技术路线在高精密封装对准环节的耗时增加,因此生产效率较低。目前,光电异质集成的商业化应用仍停留在片间、片上混合集成方案。片上异质集成方案具有高集成度、高生产效率的优势,是光电异质集成的重要发展方向[51]。

5 直接外延生长的硅基量子点激光器

直接在硅衬底上生长Ⅲ-Ⅴ族半导体增益材料[52-53]是键合技术之外的一种极具潜力且更经济的解决方案,它不仅消除了对Ⅲ-Ⅴ族半导体晶圆和复杂键合过程的需求,而且还提供了紧凑封装和更好的散热等优势(如表1 总结所示)。但是,在Ⅲ-Ⅴ族半导体层与硅层界面处,还需要克服的挑战包括晶格失配、热膨胀系数失配以及晶体极性失配[54-55]。不匹配会导致缺陷,降低半导体激光器的性能与良率。晶格常数的不匹配导致了螺纹位错的形成。位错与作为非辐射复合中心的陷阱态有关,因此降低了器件的内量子效率[54]。此外,热膨胀系数的不匹配成为生长冷却过程中的一个问题。在冷却至室温期间或之后,残余应变导致裂纹的形成,从而影响器件的良率[56]。在生长后冷却过程中,薄膜应力状态由压缩变为拉伸,热膨胀系数是导致失配位错在有源区附近形成的重要原因。在低穿透位错密度的激光器中,由于失配位错与有源区的相互作用面积更大,因此失配位错对器件可靠性的损害比穿透位错更大。为了对抗失配位错,在有源区上下插入薄应变量子阱作为捕获层,以阻止失配位错影响有源区[57]。利用量子点有源区代替传统的量子阱,进一步推动了这一研究领域的发展。高性能电泵浦量子点激光器已经在硅基底上实现[58-59]。此外,Ⅲ-Ⅴ和Si 之间的晶体极性不匹配导致反相畴,这种二维缺陷会产生局部电荷过量或缺乏,导致激光器的效率下降[12,60]。

为了解决上述问题和挑战,2016 年,伦敦大学学院刘会赟教授团队研制了直接在硅衬底上生长的连续波InAs/GaAs 量子点激光器,通过将成核层和位错过滤层与原位热退火相结合,在Ⅲ-Ⅴ族半导体层中实现了105/cm2量级的低密度螺纹位错,其阈值电流密度低至62.5 A/cm2,室温输出功率超过105 mW,工作温度高达120 ℃。他们收集了超过3 100 h 的连续波运行数据,给出了超过100 158 h 的外推平均寿命[58]。第二年,该课题组报道了第一个在轴向Si(001)衬底上单片生长的电泵浦连续 InAs/GaAs 量子点激光器,没有任何中间缓冲层。采用 MOCVD 技术在300 mm 标准工业兼容的Si(001)衬底上首次制备了400 nm 无反相畴外延GaAs 薄膜,其表面均方根(RMS)粗糙度为0.86 nm。然后通过MBE 在无反相畴的GaAs/Si 衬底上生长出量子点激光结构,实现了1.3 µm 的室温连续激光,阈值电流密度为425 A/cm2,单面输出功率为43 mW。在脉冲工作下,实现了高达102 ℃的工作温度,阈值电流密度为250 A/cm2,室温下单面输出功率超过130 mW[61]。中国科学院物理研究所张建军团队采用同质外延构建具有(111)晶面的“V”形孔洞结构,结合原位异质外延,同样有效解决了硅基砷化镓晶格失配、热失配和反相畴等问题[70]。此外,2020 年,万雅婷等也报道了在CMOS 兼容的Si(001)衬底上生长的量子点DFB 激光器,实现了温度稳定的单纵模工作,边模抑制比超过50 dB,阈值电流密度为440 A/cm2。该研究展示了128 Gb/s 的单通道速率和1.67 bps/Hz 的净频谱效率,使用O 频段中的五个通道的总传输容量为640 Gb/s,有望应用于基于WDM 的 收发器[67]。

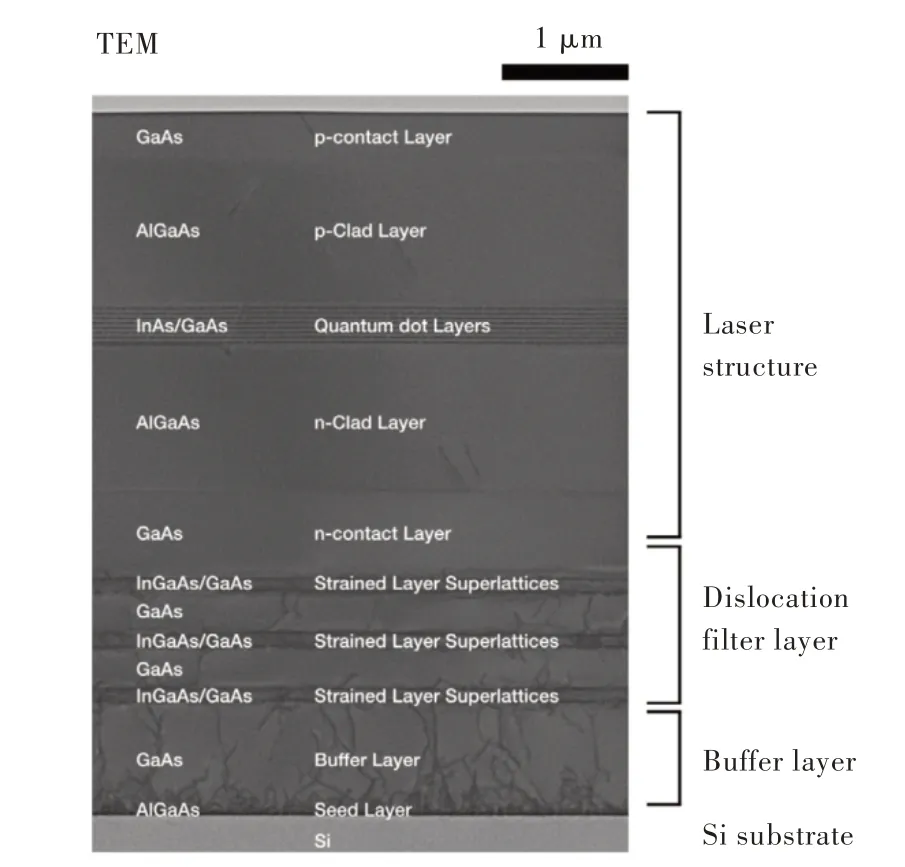

在之前的研究报道中,MOCVD 法是常用的在硅上生长种子层或缓冲层的方法。然而,利用MBE 也可以直接生长出高质量的InAs/GaAs 量子点。Kwoen 等的研究报道了第一个全过程使用MBE 方法直接在Si(001)上生长的电泵浦InAs/GaAs 量子点激光器[63]。该研究采用FP 腔的量子点激光器的阈值电流密度为320 A/cm2,单面最大输出功率为30 mW。实际上,在早期的报道中,有很多对MBE 生长条件的基础研究。Volz 团队在晶体生长之前准备了3 英寸n 型Si(001)衬底,这些Si 衬底的偏离角为+0.2°[71]。Si 衬底表面有2 nm 的天然氧化物,在用1%稀释的HF 湿法蚀刻去除氧化膜后,立即将其引入MBE 真空室。湿法蚀刻的Si 衬底表面为疏水性。这些衬底在450 ℃的真空室中脱气1 h,然后将它们转移到沉积室,在950 ℃的温度下对加热器进行10 min 的热清洗。在硅衬底上直接生长量子点激光器,主要由三部分构成,如图5 所示[50]。第一部分是在硅衬底上生长包括种子层的缓冲层。第二部分是位错过滤层,用于降低Ⅲ-Ⅴ族半导体层和Si 层之间的高位错密度。第三部分是在GaAs 衬底上生长相同的量子点层。基于MBE 生长,刘会赟教授团队报道了在硅上单片集成的低噪声量子点激光器[64],该激光器在13.5 km 长的标准单模光纤上实现了25.6 Gb/s 的数据传输,相对强度噪声小于-150 dB/Hz。此外,2019 年,Kwoen 等还通过硅上的MBE 生长,报道了Si(001)上量子点激光器的高温运行(>100 ℃)[65]。

图5 Si(001)衬底上直接生长量子点激光器的外延结构[50]Fig.5 Epitaxial structure of directly grown quantum dot lasers on Si(001)substrates[50]

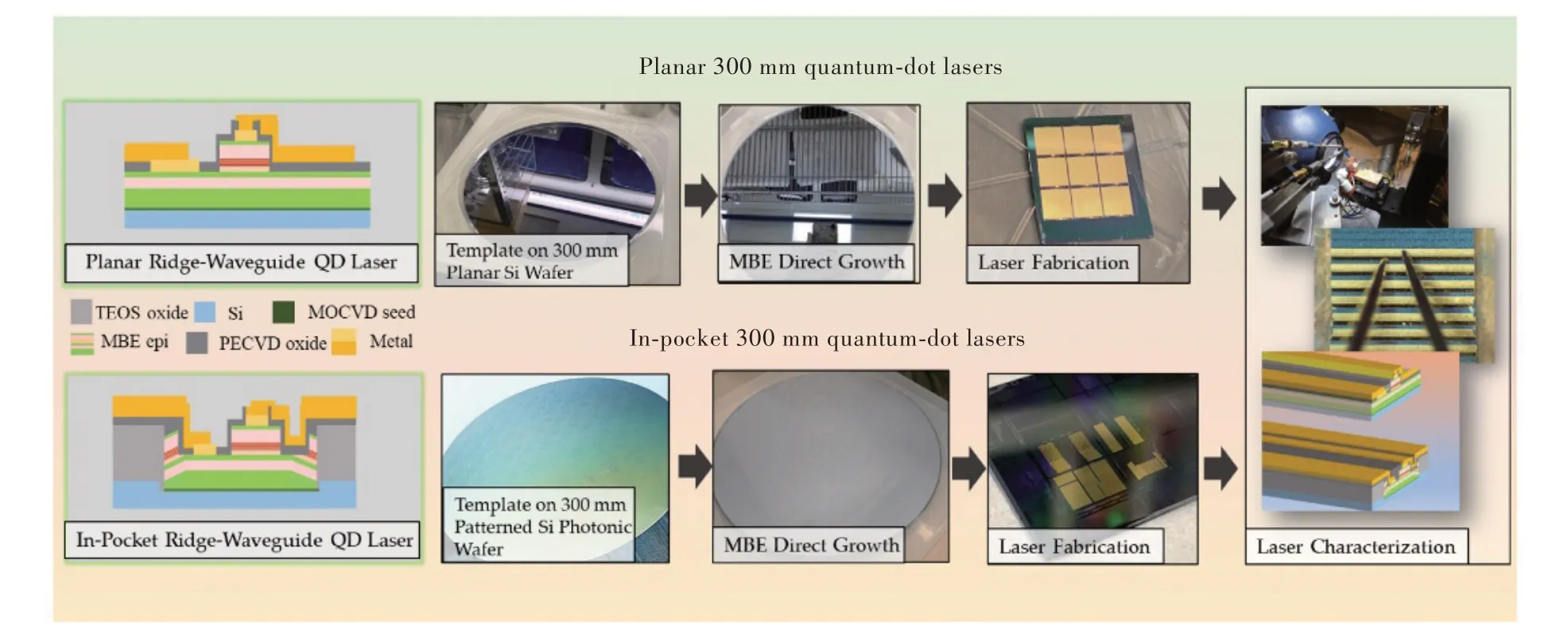

除了通过捕获层调控有源层内的缺陷之外,近年来还出现了其他解决方案。中国科学院半导体研究所韦欣教授团队提出了一种简单的方法来降低穿透位错密度——仅利用与目标GaAs组分不同的GaAs 缓冲层,而未采用复杂的位错过滤层和中间缓冲层[68]。采用MOCVD 的方法在Si(001)上生长了一层不含反相畴界的2.5 µm 厚度的 GaAs 外延薄膜,其穿透位错密度为9.4×106/cm2。利用MBE 系统在GaAs/Si(001)衬底上生长出密度为5.2×1010/cm2的InAs/GaAs 量子点。以上述方式制备的量子点激光器实现了单面室温连续波输出功率为138 mW,其阈值电流密度为397 A/cm2,激射波长为1 306 nm。此外,Shang 和Feng 等报道了硅基底沟槽中的量子点激光器,该激光器在与SiN 和Si 波导紧密相邻的300 mm 硅光子晶片上制备而成[24,72]。该研究在20 ℃ 时得到的最大双面输出功率为126.6 mW,连续激光运行温度高达60 ℃。图6 所示为制备流程图[72],在两个平台上成功制备了边发射脊波导的量子点激光器并对其进行了表征。为了进一步证明通过片上耦合将沟槽内的激光器与平面内Si 波导集成在一起的潜力,研究团队还首次提出了一种窄沟槽的量子点激光器,该激光器实现了与同一样品上相邻的Si 波导耦合。

图6 300 mm Si 上直接MBE 生长的量子点激光器及电泵浦边发射脊波导激光器制备流程图。上图为平面硅模板的制备和边发射激光器的制备流程;下图显示了用于边发射激光器和片上集成的具有紧凑沟槽图案模板的量子点激光器的制备流程[72]。Fig.6 The process flow diagram for the fabrication of quantum dot lasers directly grown on 300 mm Si by MBE,as well as edgeemitting ridge waveguide lasers with electrical pumping.The top diagram illustrates the preparation of planar silicon templates and the fabrication process of edge-emitting ridge waveguide lasers.The bottom diagram demonstrates the fabrication process for edge-emitting lasers and on-chip integrated quantum dot lasers with a compact groove pattern template[72].

量子点不仅可以降低对非辐射复合缺陷的敏感性[73],从而降低硅光子学的进入门槛,而且还提供了许多有利于光子集成电路的独特特性。在硅上生长的量子点器件已经取得了长足的进步,表现出高温稳定性[74]、低阈值运行和低反射灵敏度等[75]。由于硅基激光器缺陷管理方面的进展和有源区的创新,在与CMOS 兼容的硅基器件上,通过MBE 生长的量子点激光器在80 ℃的恒流偏置下的外推寿命已经超过22 年[76]。近期,中国科学院半导体研究所杨涛研究员团队报道了直接在轴向Si(001)上生长的超高热稳定性1.3 µm InAs/GaAs 量子点激光器,其连续波工作温度达到了创纪录的150 ℃[69]。采用优化的MBE 三步生长方法,首次制备出了低穿透位错密度为4.3×106/cm2的GaAs 缓冲层。然后,在低穿透位错密度的硅基GaAs 缓冲层上生长了8 层p 型调制掺杂的量子点激光结构,以提高器件的温度稳定性。结果表明,在10~75 ℃和10~140 ℃的宽温度范围内,量子点激光器具有超高温稳定性,其特征温度分别为T0=∞和T1=∞。量子点激光器的最大连续工作温度可达150 ℃,脉冲工作温度可达160 ℃。该量子点激光器在85 ℃和125 ℃时的连续波饱和功率分别为50 mW 和19 mW。这项工作展示了硅基直接外延量子点激光器在实现低功耗、小型化和低成本硅光子芯片方面的应用潜力。此外,中国科学院物理所张建军团队和上海交大苏翼凯团队合作采用直接外延生长的方式,在SOI 沟槽内实现了高性能Ⅲ-Ⅴ族量子点激光器的生长和制备,并首次实现了SOI基沟槽内激光器与光波导的水平耦合[77-78]。

6 总结与展望

本文综述了硅基Ⅲ-Ⅴ族半导体量子点激光器的最新研究进展。由于量子点的优越性能和优化的生长方法,在硅基衬底上键合/生长的高性能FP、DFB 和锁模边发射激光器已经得到了广泛研究,而且在寿命、阈值、功率、边模抑制比等方面的性能与在Ⅲ-Ⅴ族半导体的原生衬底上制备的激光器相当。由此可知,硅基量子点激光器足以作为硅基光子集成电路的片上光源。虽然近年来硅基量子点激光器已经取得了较大发展,但是为了满足更多的实际应用,仍然面临许多挑战,也存在一些问题亟待解决:(1)持续优化硅基片上量子点增益介质集成技术:由于硅基片与传统的Ⅲ-Ⅴ族化合物半导体材料之间晶格不匹配,导致了在硅基片上实现高质量的量子点材料的挑战。通过键合进行异质集成是目前商业上可行的方法,因为它提供了最佳的器件性能,并完美地结合了Ⅲ-Ⅴ族化合物半导体和Ⅳ族半导体的优点。然而,晶圆键合和倒装键合都不是整体集成方法,它们是短期应用的完美候选者,而从长远来看,应该开发用于高密度集成Si-PICs 的单片解决方案。因此,需要继续优化适用于硅基片的高质量量子点材料和生长技术。对于Si 上Ⅲ-Ⅴ族激光的选择性异质外延,重点应进一步增加外延Ⅲ-Ⅴ族材料的尺寸,以减少金属接触引起的光学损耗。(2)与其他材料和元件集成:对于实际应用,需要将量子点激光器与芯片上的其他材料或元件集成,例如铌酸锂、二维材料、氮化硅等材料,以及波导、调制器和探测器等元件。来自硅基激光器的光必须有效地耦合到硅波导中,这是硅上Ⅲ-Ⅴ族激光器的全面异质外延中最紧迫的问题,因为减少缺陷所需的很厚的缓冲层严重阻碍了光与硅波导的接口耦合。目前,Si-PICs 与其他先进异质光子器件的集成仍处于研发初级阶段。在未来的研究中,需要对主被动耦合和协同集成进行更多的研究。(3)制造成本和可扩展性:在工业化生产中,制造成本和可扩展性是非常重要的考虑因素。目前,硅基片上量子点激光器的制造成本较高,需要进一步优化生产工艺以降低成本并实现高质量的量产。硅上光源的生长和制造应与标准硅光子代工厂的现有工艺兼容,需要在Si/SOI 晶圆上生长有源增益材料,并有效控制污染和进行热管理。(4)波长范围限制:目前硅基片上量子点激光器主要集中在近红外和可见光波段,而在其他波长范围内的量子点激光器研究相对较少,拓展硅基片上量子点激光器的波长范围是一个具有挑战性的任务。尽管硅基片上量子点激光器面临一些挑战和瓶颈,但通过不断的研究和技术创新,相信这些问题将逐步得到解决,推动硅基片上量子点激光器的发展和应用。

本文专家审稿意见及作者回复内容的下载地址:http://cjl.lightpublishing.cn/thesisDetails#10.37188/CJL.20230185.