氮化镓基Micro-LED 侧壁对外量子效率的影响及侧壁处理技术综述

2023-12-01熊志华

邝 海,黄 振,熊志华,刘 丽

(江西科技师范大学 江西省光电子与通信重点实验室,江西 南昌 330038)

1 引言

微发光二极管(Micro-Light-Emitting diode,Micro-LED)因具有其他光源不可比拟的优势而备受关注[1-6]。首先,由于它具备自发光特性而无需偏振器,可使显示器更轻薄;其次,Micro-LED 中电光转换效率较高,理论上功耗仅为传统有机发光二极管(Organic light emitting diode,OLED)的一半,使装置的电池寿命延长、续航力更长[7-8];再次,它的响应时间为纳秒级,具备超快的切换速度,可以达到头戴虚拟现实技术(Virtual reality,VR)和增强现实(Augmented reality,AR)装备显示器最理想的像素密度,也可满足可见光通信的高响应频率要求[9-11]。此外,它具有高亮度特性,能提高装备在阳光下的可读性,可以解决由于环境光较强导致的显示器上的影像泛白、辨识度变差的问题,尤其适用于透明显示器和高亮度显示器[8,12-14]。更重要的是,Micro-LED 技术能整合多种传感器、可以识别手势,在成为显示器件的同时还可以通过加载特定频率的数据信号实现光通信功能,以满足5G 时代信息集成的需求[15-18]。可见,Micro-LED将成为解决5G 信息时代VR/AR 等高阶消费类头戴装备续航能力短、分辨率不足、亮度不够高、响应慢等问题的关键技术,同时也因能解决目前可见光通信系统传输速率低的不足而成为未来显示和可见光通信系统的理想选择,将应用于可穿戴手表、高端电视、AR/VR 等近眼显示器、物联网无线通信等领域,具有广阔的应用前景[19-28]。国际市场研究机构Research And Markets 于2021 年12 月发布的报告预测2027 年全球Micro-LED 显示市场将达211.69 亿美元[29]。

Micro-LED 自从被美国德州理工大学Jiang H X 教授团队[1,30-31]提出后,迅速引起相关科研院所和企业的关注,并取得重大成果。三星已推出了世界上第一台消费型模块化的146 英寸Micro-LED 电视。2019 年英国的Plessey 展示了Micro-LED 制备的分辨率达1 920×1 080 的VR/AR 眼镜[21]。目前Micro-LED 已应用于通信系统且传输速度可达15.78 Gbit/s,而且还在持续提高中[19,32]。这些成果充分表明了Micro-LED 强大的技术实力和发展潜力,但目前仍未商业化量产,少量已展示的Micro-LED 显示屏存在尺寸小、分辨率不够高等问题,离预期效果还有很大差距。除了仍然存在转移过程难以保证高良率以及缺乏高效红光导致Micro-LED 难以全彩化两大瓶颈外,低外部量子效率(External quantum efficiency,EQE)是Micro-LED 发展的另一大挑战[15,33-34]。目前报道的GaN 基Micro-LED 的峰值EQE 通常小于15%[35],尺寸小于5 µm芯片的峰值EQE 甚至小于1%[36],这严重影响了Micro-LED 的应用范围及产业化进程。南昌大学江风益团队制备出了高光效InGaN 基橙—红光LED 使得全彩化成为可能[37]。巨量转移技术已引起广泛关注,有望不久的将来得到解决[21,38-42]。现今,急需突破EQE 低下这一瓶颈以推动Micro-LED 产业化进程。

为了提高外量子效率,本文分析了EQE 低下的主要影响因素,讨论了侧壁缺陷对EQE 的显著影响,梳理了侧壁缺陷与载流子的作用机制,对比分析了各种侧壁处理方法的特点及范围,并展望了未来侧壁处理技术的发展趋势。

2 EQE 的主要影响因素分析

2.1 侧壁载流子损耗是EQE 低下的主要因素

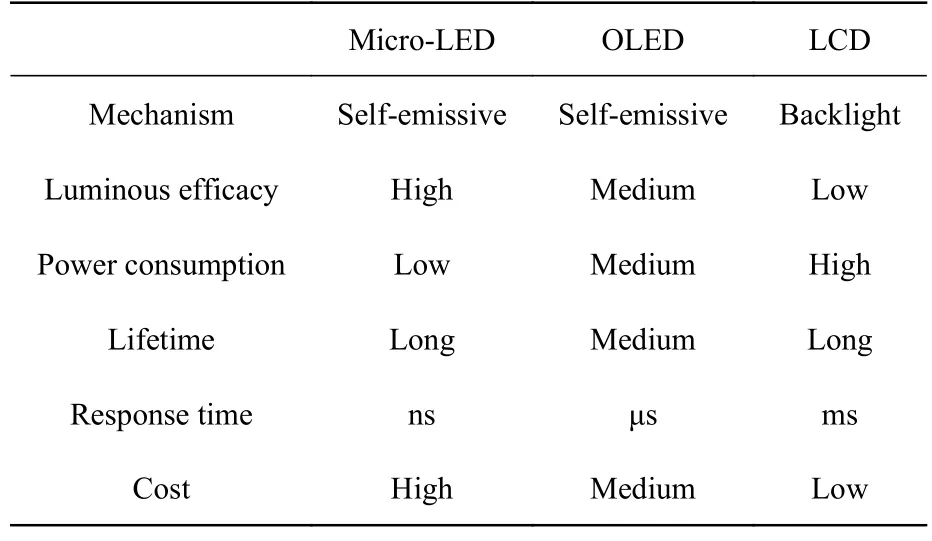

Micro-LED 具备优于液晶显示(Liquid crystal display,LCD)和OLED 的特性(见表1),但是外量子效率低下影响了其进一步广泛应用。从Micro-LED 结构示意图(见图1)可以看出,其结构包含多层,因此光的产生和传输也较为复杂,影响因素较多。

图1 Micro-LED 结构示意图(改编自文献[1])Fig.1 Schematic diagram of Micro-LEDs Structure (adapted from Ref.[1])

表1 Micro-LED 与OLED、LCD 比较[4,9]Tab.1 Performance comparison of Micro-LED,OLED and LCD [4,9]

Micro-LED 的EQE 定义为每秒发散到自由空间的光子数量与每秒LED 电子-空穴复合数之比。直接决定了LED 器件的光学性能,是非常重要的指标。如何突破低EQE 这一瓶颈已成为研究热点。诺贝尔奖获得者Shuji Nakamura 课题组等对这方面做了研究[21,33-34,42-47]。EQE 的影响因素很多,包含载流子注入、光的形成、光的传输及光的提取等,可用公式(1)表示[35]

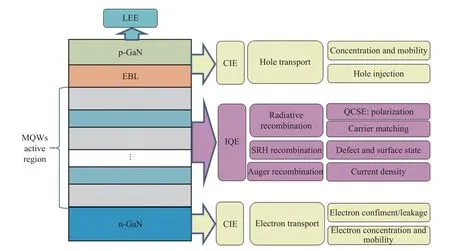

其中CIE、IQE 和LEE 分别为Micro-LED 的电流注入效率(Current injection efficiency)、内量子效率(Internal quantum efficiency)及光提取效率(Light extraction efficiency)。图2 是常见的用于模拟和效率分析的InGaN/GaN 基蓝色发光二极管的示意图。由公式(1)及图2 都可以看出,EQE 由CIE、IQE 及LEE 这三个效率共同决定:

图2 用于模拟和进行效率分析的垂直结构InGaN/GaN 基蓝色发光二极管的示意图(改编自文献[35])Fig.2 Schematic diagram of the InGaN/GaN-based blue light-emitting-diode used for the simulation and the analysis of the efficiency (adapted from Ref.[35])

(1)CIE 为输出的光功率与空间电荷区输入的电功率之比,提高载流子的匹配率可以提高CIE。由图2 可以看出,电注入效率主要由空穴和电子的注入、输运、浓度等决定,而这些都与缺陷有很大关系。主要原因是Micro-LED 中侧壁缺陷形成的非辐射复合中心严重影响了载流子的注入能力,缺陷处还容易形成漏电流通道,这些都对载流子的有效复合产生很大影响,使得CIE 降低从而引起EQE 下降[42]。

(2)LEE 为每秒发散到自由空间的光子数与每秒空间电荷区产生的光子数之比,由光的传输决定,受电极等影响较大[48]。对于LED,理想情况是载流子复合后产生的光都从顶部射出并被充分利用,但实际情况是,光在传输过程中会发生反射、散射、吸收等损耗,也可能从侧面射出未被有效利用,这些行为会引起LEE 降低,从而影响EQE。为减少光损耗提高LEE,目前常用的方法主要有提高反射层的反射率、表面粗化及表面钝化等[49-51]。

(3)IQE 为每秒空间电荷区产生的光子数量与每秒LED 电子-空穴复合数之比。根据ABC模型[43,52-54],IQE 如式(2)和(3)所示。其中:Rrad、RSRH及RAuger分别表示载流子辐射复合率、肖特基(Shockley-Read-Hall,SRH)辐射复合率及俄歇(Auger)复合率;n为载流子密度;A、B、C分别表示非辐射复合系数、辐射复合系数及俄歇复合系数。根据式(2)和式(3)可知,IQE 由载流子的复合及载流子浓度决定,发光效率由辐射复合和非辐射复合的竞争决定,要想通过提高IQE 来提高EQE,必须使得载流子自发辐射率最大化、减少俄歇复合及SRH 复合[55]。

根据以上分析,EQE 由LEE、CIE 及IQE 共同确定,受晶体质量、热管理、载流子注入效率等因素影响[56-57],其中,载流子及缺陷是主要影响因素。由图2 可见,IQE 的主要影响因素为载流子和缺陷,CIE 主要影响因素为载流子注入、浓度及迁移等,而缺陷也同时影响光的射出,从而影响LEE。因此,缺陷和载流子是EQE 的主要影响因素。Shuji Nakamura 课题组等研究结果也表明侧壁损伤及缺陷引起的载流子损耗是Micro-LED 的EQE 降低的主要原因[42-47]。因此,降低侧壁引起的载流子损耗及侧壁缺陷密度是提升EQE 的关键。

2.2 Micro-LED 中侧壁缺陷对外量子效率的影响分析

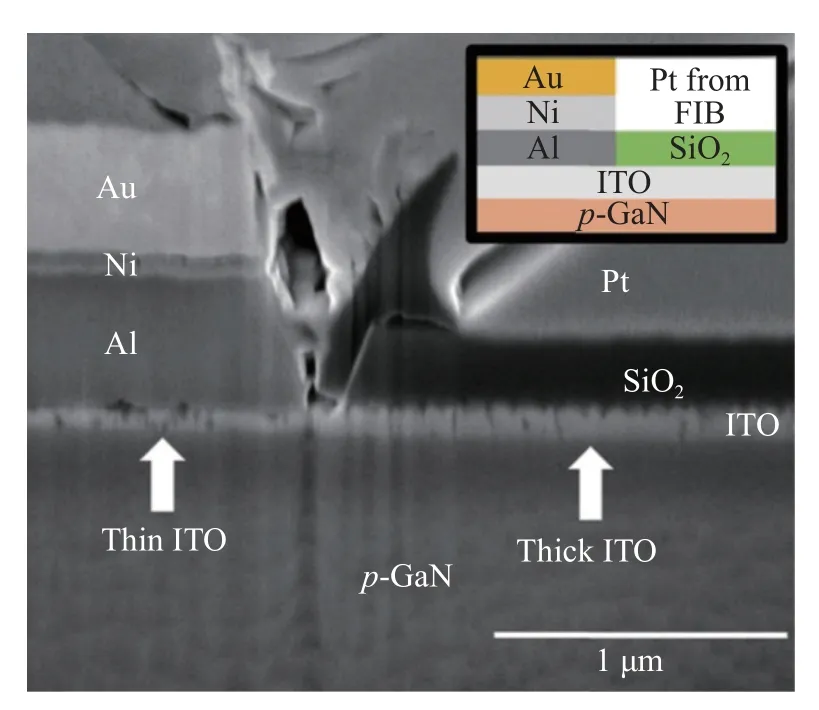

Micro-LED 制备需要经过电感耦合等离子体(Inductively coupled plasma,ICP)刻蚀工艺,图3为ICP 腐蚀后ITO 层的横断面扫描电子显微镜(Scanning electron microscope,SEM)图像。其中,左侧经ICP 蚀刻去除SiO2、右侧为在蚀刻过程中覆盖光刻胶,标记为“Pt”的层是在聚焦离子束(Focused ion beam,FIB)扫描电镜横断面成像时沉积的铂层。从图中可以看出,经过ICP 刻蚀后侧壁不可避免地留下了化学污染和损伤,主要包含:深能级非辐射复合中心、掺杂杂质、挥发性强的元素及污染层等[21,58-60]。对于常规尺寸LED,EQE 主要由外延生长和芯片结构等决定,上述侧壁损伤及缺陷引起的载流子及光损耗对EQE 的影响几乎可以忽略不计。然而,Micro-LED 一般单边尺寸小于100 μm,一些高清显示器,如面向头戴VR/AR 装备用高分辨率显示器要求芯片需小于10 µm×10 µm[43,55,61]。在这样的尺寸条件下,芯片周长与面积比值较大,刻蚀过程中产生的侧壁损伤、缺陷以及器件的表面复合区域所占的比例很大,任何缺陷和杂质都会促进表面少数载流子复合[55]。研究证明,刻蚀后的杂质和氧化物能诱导缺陷能级[60]。同时,侧壁边缘的周期性受干扰,诱导出半导体间隙中的电子态并成为非辐射复合中心[62],另外,小尺寸Micro-LED 的侧壁存在一些载流子堆积,引起“边缘效应”与“尺寸效应”[42,45,48,63]。此外,随着芯片尺寸的减小,空穴更容易被缺陷捕获,空穴注入效率也随之下降[47]。在这种情况下,漏电流也随着尺寸的减小而增大,导致EQE 随着尺寸减小而剧烈下降[64]。Ding K 等[65]研究表明当芯片尺寸从500 µm×500 µm降低到10 μm×10 μm 时,最大EQE 由10 %下降到5 %。可见,侧壁表面及缺陷引起了载流子非辐射复合,限制了载流子注入能力,导致漏电流通道的形成。这些侧壁缺陷引起的载流子损耗在Micro-LED 中非常显著,成为EQE 低下的主要原因[42,66]。

图3 ICP 腐蚀后ITO 层的横断面扫描电子显微镜(SEM)图像[62]Fig.3 Cross-sectional scanning electron microscopy (SEM)image of ITO layer after exposing to ICP etch [62]

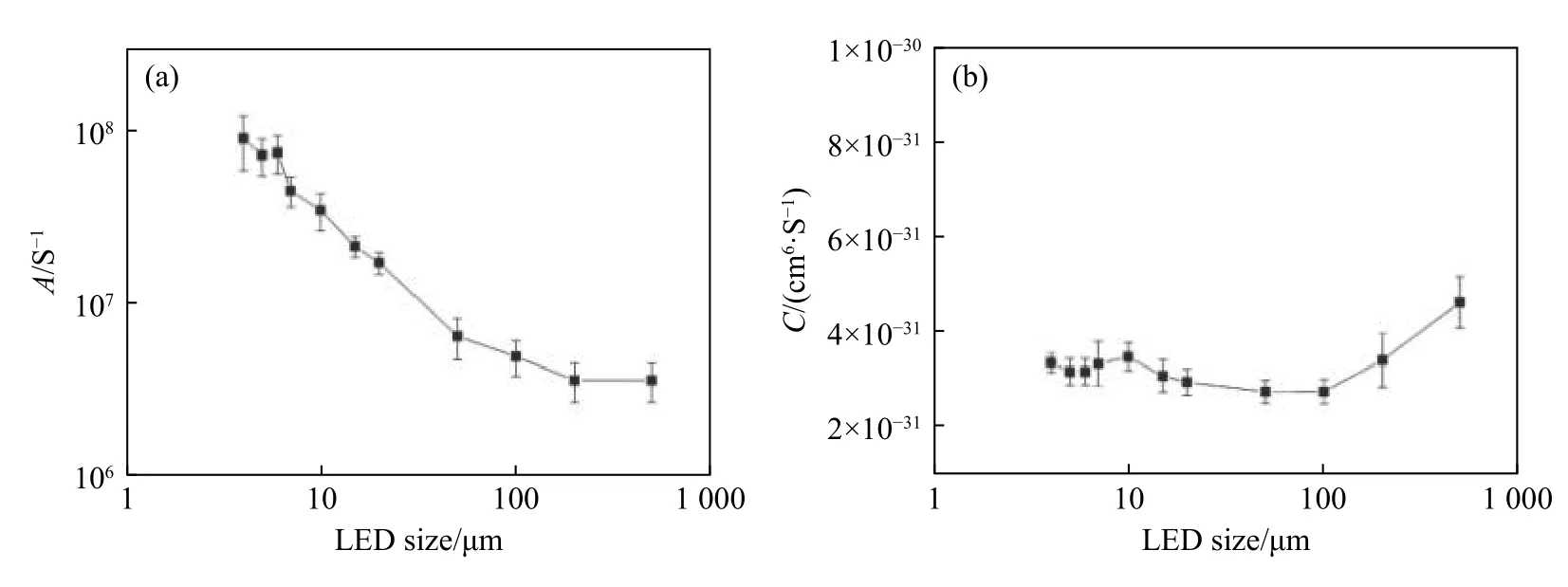

俄歇复合和SRH 复合是LED 中最主要的两种非辐射复合[55],Micro-LED 应用于显示领域时一般电流密度较低[67],此时俄歇复合占比较小,几乎可以忽略,载流子主要表现为SRH 复合。Olivier 等[53]研究了尺寸对载流子复合的影响,研究结果见图4。由图4 中可以看出:在一定范围内,ABC 模型中SRH 复合对应的系数A随着芯片尺寸减小而明显增大,而俄歇复合对应的系数C始终保持相同数量级、变化不大。结果证实了SRH 复合是小尺寸Micro-LED 的主要载流子损耗。SRH 复合由捕获中心的密度、截面及能级决定[35],Micro-LED 的非辐射复合中心集中在侧壁缺陷[64],是引起Micro-LED 的EQE 下降的主要原因。由公式(3)中得出,降低An即降低SRH 复合是提高EQE 的关键[34]。故可通过降低侧壁缺陷密度及其引起的载流子损耗实现。

图4 提取系数A(a)和C (b)随着LED 尺寸的变化图[53]Fig.4 Extracted coefficients A (a) and C (b) plotted versus LED size[53]

2.3 侧壁缺陷影响EQE 的物理机制

LED 的工作原理是将电能转换为光能。根据能量守恒定律,理想情况是注入的载流子都能有效复合转换为光子,并被合理利用。实际上,除了电子、空穴的有效复合,载流子还会有所损耗,尤其是在表面和缺陷处。对于Micro-LED,载流子损耗集中在侧壁处,主要表现为:

(1)电子、空穴在侧壁表面发生复合形成光子,但是光从侧壁散发出并未被有效利用。尺寸较小的Micro-LED 中侧向电阻低、电流扩展更好,载流子更容易输运到有源层边缘在侧壁发生辐射[33,48,68]。从图2 可以看出,侧壁处形成的光子容易选择最短路径直接从侧壁处发射或者被表面缺陷吸收,引起LEE 降低从而导致EQE 低下[49-50,54]。研究人员[48]通过模拟计算证明:“尺寸效应”很大程度取决于有源区侧壁表面的载流子复合引起的载流子损耗,因此EQE 随着尺寸减小而降低。

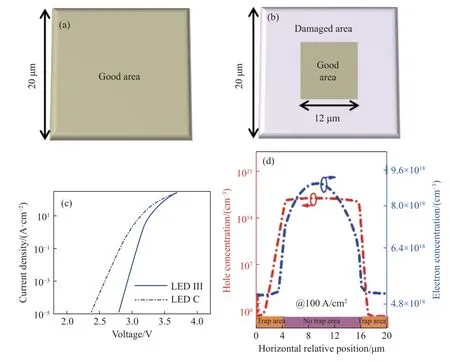

(2)侧壁损伤或者缺陷处形成泄漏通道,载流子在缺陷处形成漏电流。张紫辉联合郭浩中团队[42]对比分析了相同尺寸20 µm×20 µm 带侧壁损伤和完整未带损伤的Micro-LED,结果见图5。图5(c)为样品的I-V 曲线图,从图中可以看出Micro-LED 侧壁缺陷处易形成电流泄漏通道,最终导致EQE 急剧下降。

图5 (a)完整的Micro-LED 示意图;(b)侧壁带缺陷的Micro-LED 示意图;(c)样品的I-V 曲线;(d)样品的P 电极附近的载流子浓度变化(改编自文献[42])Fig.5 Schematic diagrams for (a) LED without sidewall damages and (b) LED with sidewall damages;(c) the current-voltage characteristics in semi-log scale for LEDs;(d) changes in carrier concentration profiles near the P-region for LED (adapted from Ref.[42])

(3)载流子在缺陷处被捕获发生非辐射复合。研究表明,俄歇辐射系数基本不随尺寸变化,而肖特基辐射复合系数随着尺寸降低而增大,这意味着小尺寸的Micro-LED 表面缺陷引起的SRH 非辐射复合严重影响EQE[53]。张紫辉团队为此做了大量工作,图5(d)显示样品台面边缘的载流子浓度快速下降,这是因为载流子在侧壁被缺陷捕获发生SRH 复合[42]。2020 年,他们又联合刘召军博士团队进一步证实[69]:晶体质量和载流子输运会影响光电性能。干蚀刻所引起的表面损伤和缺陷会引起表面非辐射复合,使得Micro-LED 的IQE 降低,严重影响EQE。2021 年,他们再次强调侧壁缺陷引起的非辐射复合是EQE 低下的一个重要原因[33]。

载流子在侧壁缺陷处行为的厘清有利于提高EQE,但是载流子与缺陷的具体相互作用机制及模式并没有被系统研究,不同缺陷与载流子相互作用的差异性也并不十分清楚,比如在空位处和位错处漏电流分布是否相同、载流子的非辐射复合是否一样等。需进一步根据缺陷种类有针对性地深入研究侧壁缺陷对载流子输运及复合的影响,为后续提出更有效的侧壁处理方法提供理论基础。

3 侧壁处理技术及缺陷修复方法

为了提高外量子效率,降低Micro-LED 的侧壁载流子损耗和缺陷密度是关键[70],缺陷修复是基本途径,目前侧壁处理技术及缺陷修复方法主要有:

(1)优化设计芯片内部结构,使得载流子远离侧壁表面。Corfdir P[71]等设计了core-shell 结构,使得载流子远离表面,从而有效降低了表面辐射。郭浩中团队通过减薄势垒层厚度来降低垂直电阻,调节扩散电流,可以更好地将电流限制在台面内、远离侧壁,以降低载流子横向输运到侧壁的几率,减少了表面非辐射复合,并提升空穴注入率,提高了EQE[69]。芯片结构的优化可以在一定程度提高EQE,但是侧壁表面及缺陷发生的载流子和光的损耗仍然存在,不容忽视。

(2)热处理法。研究已证实热处理可以消除近表面部分缺陷,降低侧壁缺陷密度,从而降低漏电流。但是处理过程中必须控制好退火工艺,假如温度过高容易引起新的缺陷,产生并导致漏电流增大[72-73]。田鹏飞等[45]通过增加退火时间部分修复了缺陷,使得低电流密度下的发光效率得到提高。但是退火不能使缺陷完全消除,在合适的条件下经退火处理后,LED 仍然存在漏电流,可能与侧壁的N 空位有关[72]。具体物理机制还有待进一步深入研究。合适的处理条件如温度、时间等应根据不同的芯片选择。

(3)化学处理法。干法刻蚀工艺使得Micro-LED 侧壁产生损伤及缺陷,很多研究人员尝试采用湿法化学刻蚀来降低侧壁损伤,目前已报道的化学法有采用氢氟酸(HF)或者氢氧化钾(KOH)处理。采用稀氢氟酸处理后制备的AlGaInP 极小尺寸红光Micro-LED,在低注入电流区和高注入电流区的EQE 分别提高到了35.48%和12.86%。主要是通过化学处理消除了侧壁表面的一些物理缺陷、污染物和材料损伤等,因此,降低了由于表面缺陷引起的非辐射复合率[74]。这对氮化镓基Micro-LED 具有重要的借鉴意义,后续可研究采用氢氟酸处理氮化镓基Micro-LED,并研究其对污染物、侧壁损伤及EQE 的影响。研究人员采用KOH 处理ICP 刻蚀后的LED 侧壁,结果显示漏电流变小了。进一步证实了经过氢氧化钾处理后侧壁缺陷的密度下降了[72]。综上,化学法可以消除部分刻蚀后留下的漏电流通道[75],但是目前常用的氢氧化钾和氢氟酸都较容易侵蚀金属,因此单独采用化学法处理后效果并不是很理想,可进一步联合采用其他方法共同处理Micro-LED侧壁以达到更好的效果。

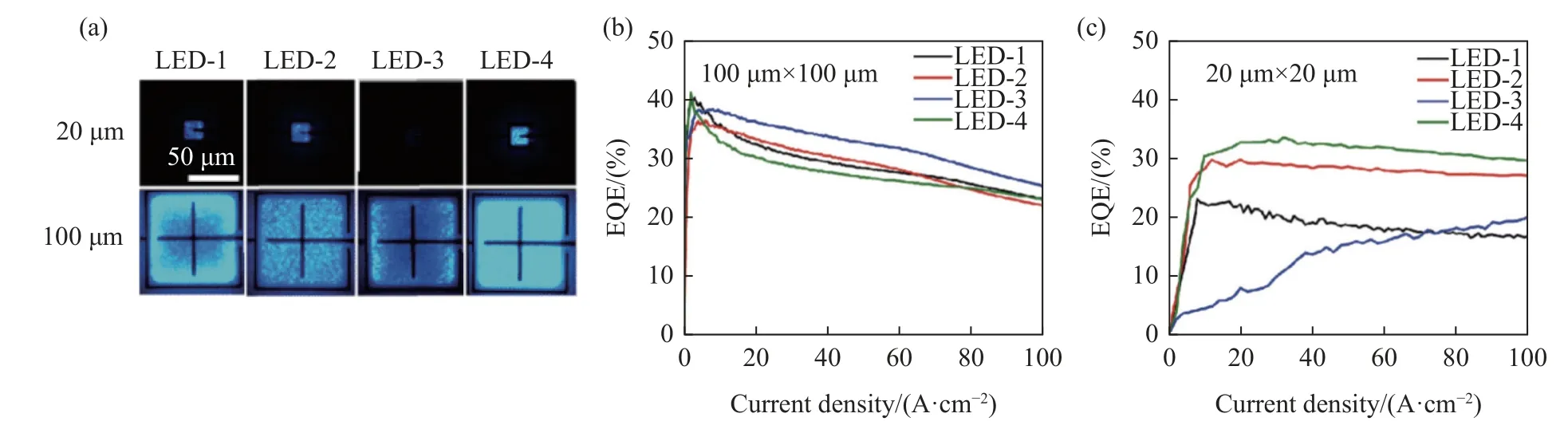

(4)侧壁钝化法。钝化是较常用的侧壁处理方法,不仅可以抑制侧壁悬挂键、降低侧壁缺陷,还可以减少光从侧壁的发出率,提升LEE,从而提高EQE[51,55,76-77],被认为是降低Micro-LED 表面辐射的关键技术[48]。生产中用的较多的是等离子体增强化学的气相沉积法(Plasma enhanced chemical vapor deposition,PECVD)。这种方法沉积速度快,对大尺寸器件有一定的减小漏电流的作用,但对于芯片面积小于60 µm×60 µm 的Micro-LED[62],PECVD 钝化并不能有效降低漏电流,主要原因是钝化层致密度不够,部分缺陷无法被有效钝化[78]。另外,PECVD 钝化可能降低ITO 层的透明度,而影响光输出[79-80]。研究人员采用原子层沉积法(Atomic layer deposition,ALD)从原子水平精确控制钝化层厚度、制备更致密的钝化层[62-81],研究结果显示钝化后缺陷密度有效降低、漏电流有所减小,主要原因是ALD 层抑制了载流子的表面辐射和侧壁缺陷引起的漏电流。Wong M S 等[62]对比了采用ALD、PECVD 侧壁钝化后及未钝化的Micro-LED,样品图及研究结果见图6。其中,样品LED-1 未经过侧壁处理,LED-2 经过ALD 钝化和ICP 刻蚀,LED-3 通过PECVD 侧壁钝化和HF 刻蚀,LED-4 经过ALD 侧壁处理和HF 刻蚀,研究结果显示:ALD 侧壁钝化后的LED 光输出较一致、漏电流最小、20 µm×20 µm芯片的峰值EQE 由钝化前的24%提高到33%。结果表明:对于尺寸较小的Micro-LED,ALD 钝化效果明显优于PECVD 钝化,主要原因是ALD 钝化可以消除一些非辐射复合中心,降低了“尺寸效应”对Micro-LED 外量子效率的影响。目前ALD 技术主要用作生长二氧化硫和氧化铝层作为钝化层,其中氧化铝的稳定性好、致密度高[82-83],是侧壁钝化的理想选择[76,81]。然而,ALD 沉积速度较低、难以沉积较厚的钝化层,因此,可以考虑根据实际情况综合使用ALD 和PECVD 这两种钝化方法[55]。研究人员对比了联合采用这两种方法制备双层Al2O3/SiO2和单独采用PECVD 制备单层SiO2钝化后的Micro-LED,结果发现前者的漏电流更小、EQE 更高,且前者侧壁未发现缺陷相关的非辐射点。研究表明联合使用ALD 和PECVD 双层钝化能有效降低侧壁缺陷[64]。这是侧壁处理技术未来发展方向,钝化层的选择也应该更多样化。

图6 (a)样品在1 A/cm2 下的电致发光图像;(b)、(c)不同尺寸芯片的EQE 随注入电流密度的变化(改编自文献[62])Fig.6 (a) Electroluminescence images of Micro-LEDs at 1 A/cm2;(b),(c) variation of EQE with injection current density for different chip sizes (adapted from Ref.[62])

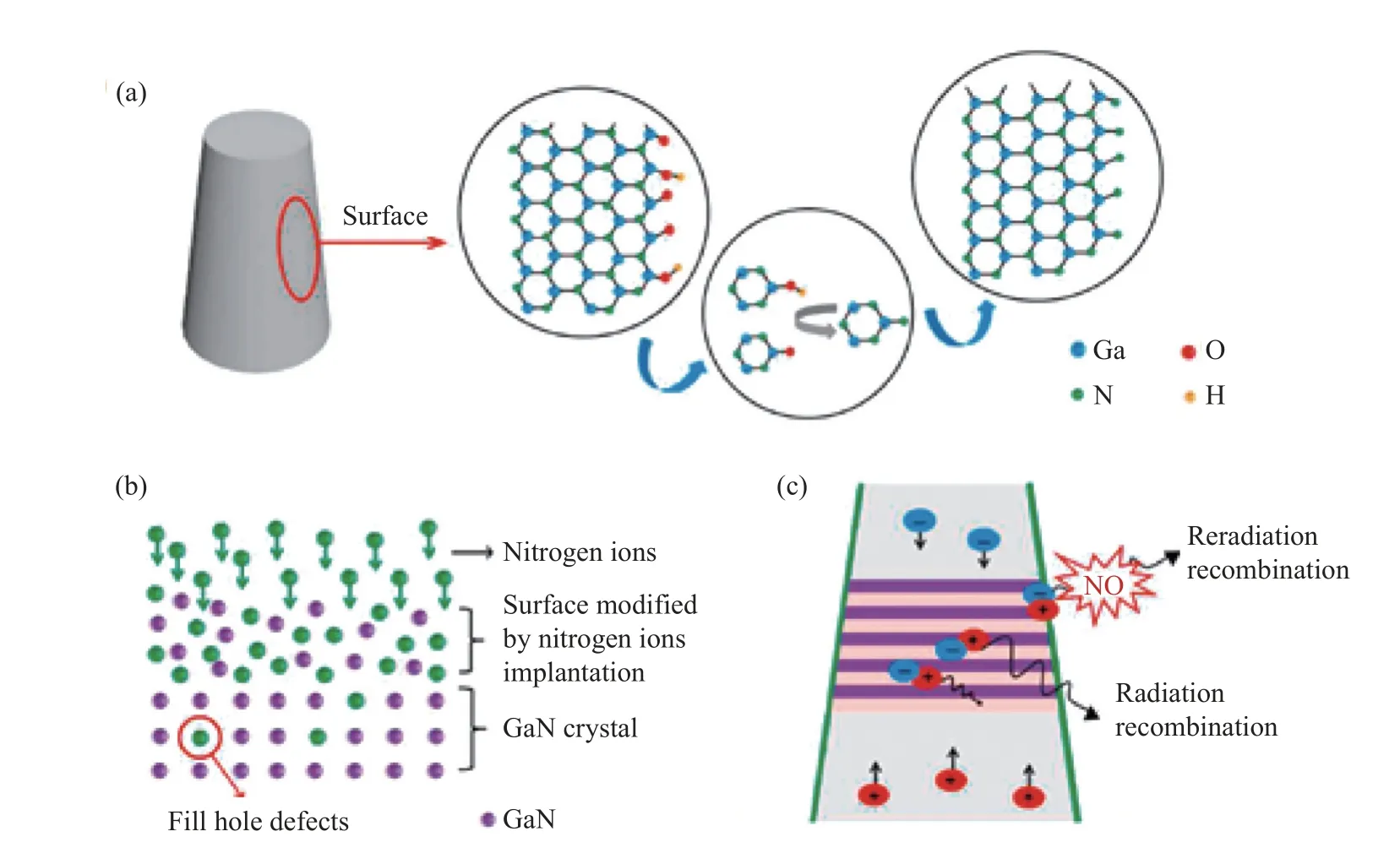

(5)离子注入法。研究发现氮离子注入Micro-LED 后,N 原子比例由23.3%增加到43.0%,而O 原子比例由21.1%降低到6.7%,器件的光致发光强度提高了7 倍,EQE 提高约33%,漏电流减小,开启电压和工作电压都降低,光电性能得到改善[70]。这意味着通过离子注入可以抑制表面悬挂键等缺陷。主要原因是N 离子注入后代替O 或者OH 与侧壁表面Ga 悬挂键发生反应,从而降低了表面的缺陷密度。离子注入后,Micro-LED 的表面变化见图7(彩图见期刊电子版)。研究结果证实了离子注入能降低缺陷密度,抑制载流子表面非辐射复合。根据以上研究结果,后续可以依据Micro-LED 的侧壁缺陷中悬挂键的类别及表面分布情况,通过合适的离子注入方式消除表面悬挂键及空位,降低缺陷密度,提高外量子效率。离子注入量及离子类型需要根据缺陷种类进一步研究。

图7 离子注入后Micro-LED 表面变化示意图。(a)表面化学结构发生变化;(b)原子排列、表面修复和空穴缺陷填充;(c)GaN 中的钝化层[70]。Fig.7 Schematic diagram of Micro-LED surface changes after ion implantation.(a) Changes in surface chemical structure;(b) atomic alignment,surface repair and cavity defect filling;(c) passivation layer in GaN[70]

(6)联合使用化学法及钝化法。研究表明单独采用化学处理法无法完全消除缺陷,Nakamura S H 团队采用HF 刻蚀与ALD 联合处理Micro-LED,使得尺寸为20 µm×20 µm 的LED 的EQE由24%提高到33%,漏电流减少,而且在低电流密度时发光均匀性较好[62]。研究人员采用KOH化学法与ALD 技术相结合进行处理。结果表明这种联合处理方法对SRH 非辐射复合和等离子体损伤诱导的表面复合具有较好的抑制作用[62,84]。可见,联合使用化学法和钝化法对于降低非辐射复合、提高EQE 具有较好的效果,后续可根据实际效果和操作性,进一步研究更多的联合处理方法。

近年来,Micro-LED 技术得到快速发展[85],目前通过侧壁处理使得EQE 低下的问题得到了一定改善,但是研究主要集中于侧壁整体处理及处理后的效果,较为笼统。侧壁中各类缺陷如空位、悬挂键、位错占比如何?它们在侧壁如何分布?各种缺陷适合的处理方法是什么?各类缺陷在各种处理方法中如何变化?最佳的缺陷修复模式和机制是什么?这些都是解决因“边缘效应”与“尺寸效应”引起的EQE 低下这一瓶颈的关键,但是目前并不十分清楚,需对缺陷特征、分布及作用机制进一步深入研究,有针对性地根据缺陷种类和分布提出更有效的侧壁处理方法。

4 结论与展望

Micro-LED 是未来高清显示器和可见光通信领域的理想选择,近年来已取得了较好的成果,但是目前Micro-LED 外量子效率仍较低下,严重影响其产业化进程及利用率。经过20 多年的研究,发现载流子在侧壁表面及缺陷处发生表面复合、非辐射复合、漏电流等损耗,是Micro-LED 外量子效率降低的主要原因。载流子的有效调控及缺陷密度降低是解决问题的关键。目前报道的侧壁处理方法主要有优化设计芯片内部结构、热处理、化学法、钝化法、离子注入法及联合使用多种方法等,这些侧壁处理方法对提高EQE 有一定的效果。

然而,现有侧壁处理方法较为笼统、针对性不强。后续需要根据侧壁缺陷种类及分布,进一步提出更有效的侧壁处理方案,以下基础性问题值得深入探讨和求索:(1)侧壁缺陷的种类及分布规律:不同缺陷与载流子的作用机制不同,侧壁处理过程中发生的反应也不同,应该厘清侧壁缺陷的种类及特征;(2)侧壁缺陷与载流子的作用机理:载流子在缺陷处会发生非辐射复合、漏电流等损耗,但是各种缺陷与载流子的具体作用机制未系统研究;(3)各种缺陷在侧壁处理过程中的作用机理及动力学:位错、空位、畸变等在侧壁处理过程中发生的反应不同,动力学也不同,应总结各类缺陷修复模式。在此基础上,有针对性地提出更有效的侧壁处理方法和缺陷修复方案,实现非辐射复合率降低、漏电流减小及缺陷密度下降的目标,为突破EQE低下这一瓶颈提供理论参考。

在进一步深入研究以上微观作用机制的基础上,针对目前常用的侧壁处理方法存在的问题和困难,提出如下展望:(1)开发一种新的侧壁处理方法,能修复所有,至少大部分缺陷,切实有效地降低缺陷密度、提高Micro-LED 的外量子效率。目前研究表明,钝化法能有效抑制悬挂键,离子注入能有效修复空位,热处理可以消除近表面部分缺陷,化学法能较好地去除一些表面污染,如何综合各方法的优点开发出一种新技术能去除、修复或者屏蔽所有,至少大部分类型缺陷,是未来研究方向;(2)利用高新科学技术,优化Micro-LED 生产工艺和设备,从源头上减少缺陷的产生,从根本上解决侧壁缺陷对外量子效率的不利影响。目前刻蚀工艺和设备的优化已受关注,但是因为Micro-LED 尺寸的特殊性,还未能完全解决侧壁损伤问题,可进一步利用光、声、电等还有其他物 理、化学反应,以及日益精湛的检测技术,减少侧 壁缺陷产生,有望不需要通过侧壁处理就能使得 外量子效率显著提高;(3)加快培养相关综合型复 合型专业创新人才培养。Micro-LED 的侧壁处理 及缺陷修复技术,涉及到物理、化学、材料、机 电、检测、显示等各领域,仅熟悉其中一两个专业 的技术人员已无法满足需求,急需培养多领域的 综合应用型人才,是解决外量子效率低这一瓶颈 的重要保障。随着技术的不断发展,Micro-LED 的侧壁处理技术会逐步完善,外量子效率会 相应提高,高性能的Micro-LED 会更好地更广泛 地应用于显示和可见光通信领域,Micro-LED 产 业化指日可待。