用于配电台区柔直互联的固态开关控制研究

2023-11-21刘卓睿蔡木良熊健豪

刘卓睿,安 义,蔡木良,熊健豪,刘 蓓,韩 星

(国网江西省电力有限公司电力科学研究院,江西南昌 330096)

配电网长期实行“环网设计、开环运行”方式,即使已进行配电自动化改造,故障隔离及故障后复电倒闸操作仍会造成非故障区的短时停电[1]。若进行跨分区合环,馈线两侧因存在电源幅值、相角差,合环运行会出现较大的冲击电流和合环电流,将严重影响电网安全运行。

背靠背柔性直流基于共用直流母线的电压源换流器,将交流系统进行AC-DC-AC 解耦互联,可实现任意馈线长期安全合环运行。为了更好地实现互联控制,需要利用固态开关实现直流连接[2-3]。随着半导体技术的不断发展,基于第三代半导体材料SiC的MOSFET 日益成熟[4-5],相比于传统的Si 材料,SiC材料拥有更高的晶体稳定度和更低的导通损耗,因此基于SiC-MOSFET 的固态开关对供配电系统功率和体积的要求,是未来的发展方向[6]。在固态开关设计中,为了提高主电路载流能力和供电冗余度,需要将多个SiC-MOSFET 并联使用从而减小单个SiCMOSFET 的电流应力,提高其寿命和可靠性[7-9]。但多个SiC-MOSFET 并联使用时会发生并联支路电流的不均衡现象[10-13],严重时会引起SiC-MOSFET 的失效,影响到整个固态开关的安全。

针对SiC-MOSFET 并联支路电流的不均衡,该文将首先对SiC-MOSFET 并联均流的影响因素进行数学分析和仿真验证,其次提出一种SiC-MOSFET并联支路动态电流均衡方法,最后通过数学推导和实验对上述方法进行验证。

1 固态开关工作原理

固态开关是集继电器的转换功能与断路器的保护功能于一体的一种新型智能开关设备,其一方面可以通过检测负载上的电压电流来开通、关断电路,另一方面也可以通过上位机的指令来开通、关断电路[14-15]。

图1 为SiC-MOSFET 固态开关基本的结构框图,从图1 中可以看出,固态开关可以分为主电路部分、数据采集部分、控制模块部分、上位机部分、驱动电路部分和供电电源部分等。

图1 固态开关结构框图

主电路部分主要包括功率电源、开关管Q1、Q2和负载,其是固态开关的功率执行部分,其主要功能是将能量由电源传送到负载,核心部件为功率开关管,因为SiC-MOSFET 具有高击穿场强、低导通损耗和高热导率等优良特性,更符合固态开关设计的要求,故开关管Q1、Q2选择为SiC-MOSFET;数据采集部分包括采样模块和信号调理模块,其主要功能是把固态开关主电路的电压、电流信息传递给系统的控制模块,其中采样电路的功能是对主功率电路的电压、电流信息进行采样并传递给信号调理模块,信号调理模块的功能是对采样后得到的电压、电流信息进行滤波处理,然后传递给控制模块部分;控制模块部分作为固态开关的逻辑处理中枢,首先要对信号调理模块输出的电压、电流信号进行模数转换,然后对数字电压、电流信号和上位机控制指令进行逻辑判断,最后控制模块输出控制信号给驱动电路,控制主电路SiC-MOSFET 的开通与关断。

2 并联均流影响因素分析

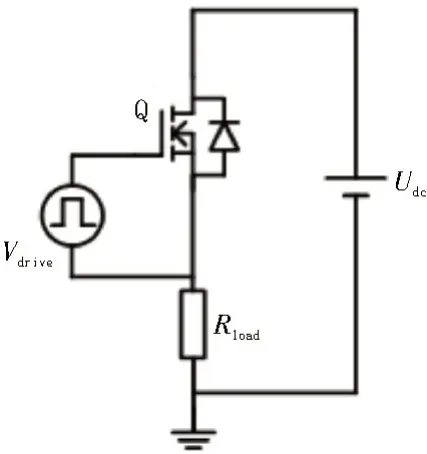

图2 为SiC-MOSFET 并联测试电路示意图,图中包含两个理想的SiC-MOSFET,分别为Q1和Q2,其驱动信号由单一驱动器产生,Cgs1(Cgs2)、Cgd1(Cgd2)、Cds1(Cds2)分别为Q1(Q2)的栅源电容、栅漏电容和漏源电容,Lg1(Lg2)、Rg1(Rg2)分别为Q1(Q2)栅极封装和电路走线所产生的寄生电感和寄生电阻,Ld1(Ld2)、Rd1(Rd2)分别为Q1(Q2)漏极封装和电路走线所产生的寄生电感和寄生电阻,Ls1(Ls2)、Rs1(Rs2)分别为Q1(Q2)源极封装和电路走线所产生的寄生电感和寄生电容,Udc为主电路电压Lload和Rload为负载电电感和负载电阻,D 为负载反并联二极管。

图2 SiC-MOSFET并联测试电路示意图

当驱动脉冲为高电平时,分别通过Lg1、Rg1、Ls1、Rs1和Lg2、Rg2、Ls2、Rs2对电容Cgs1和Cgs2进行充电,从而使得Q1和Q2由截止状态转变为饱和状态,最后到达线性状态,同时直流电源Udc分别通过Ld1、Rd1、Q1、Ls1、Rs1和Ld2、Rd2、Q2、Ls2、Rs2对负载进行供电;当驱动脉冲为低电平时,电容Cgs1和Cgs2分别通过Lg1、Rg1、Ls1、Rs1和Lg2、Rg2、Ls2、Rs2进行放电,从而使得Q1、Q2由线性状态转变为饱和状态,最后到达截止状态,同时负载Lload和Rload通过反并联二极管D 进行续流放电。

SiC-MOSFET 开关过程中,器件的漏极电流id随栅源电压Vgs的变化而变化:

式中,Udc为直流电源电压,Rds(on)为SiC-MOSFET的通态电阻,Rload为电路的负载电阻,Rd和Rs分别为SiC-MOSFET 漏极和源极寄生电阻,Vth为SiCMOSFET的阈值电压,L和W分别是SiC-MOSFET 的沟道长度和沟道宽度,μn是SiC-MOSFET 反型层中电子迁移率,Cox是SiC-MOSFET 单位面积栅氧化层电容。

由式(1)可知,通态电阻Rds(on)会直接影响SiCMOSFET 处于线性区时的电流,即SiC-MOSFET 的静态电流,而阈值电压Vth会直接影响SiC-MOSFET 处于饱和区时的电流,即SiC-MOSFET 的动态电流。图3 为SiC-MOSFET 器件参数分散性测试电路。

图3 SiC-MOSFET器件参数分散性测试电路

以UnitedSiC 公司生产的UF3C065040K3S 为例,测试7 只样品SiC-MOSFET 通态电阻Rds(on)和阈值电压Vth参数的分散性。在测试SiC-MOSFET 的通态电阻Rds(on)时,驱动电压Vdrive、主电路电压Udc和负载电阻分别保持为15 V、28 V 和5 Ω不变,通过测得负载两端的电压Vload,即可得知SiC-MOSFET 器件的通态电阻Rds(on)值为:

测试SiC-MOSFET 器件的阈值电压Vth时,保持主电路电压Udc和负载电阻Rload分别为28 V 和5 Ω不变,驱动电压Vdrive从零开始缓慢上升,利用电压表测试负载两端的电压Vload,当Vload不为零时,此时的驱动电压Vdrive即为SiC-MOSFET 的阈值电压Vth。

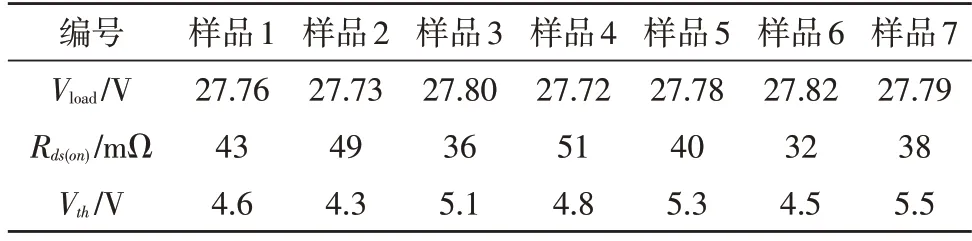

表1 为测试所得的SiC-MOSFET 通态电阻Rds(on)和阈值电压Vth分布情况表,由表1 可知,此组样品SiC-MOSFET 的通态电阻Rds(on)和阈值电压Vth分别分布在32~51 mΩ和4.3~5.5 V 之间,均存在相对偏差,分散性较大。

表1 SiC-MOSFET通态电阻和阈值电压分布情况表

1)通态电阻Rds(on)分散性的影响

通过对式(1)的分析可知,通态电阻Rds(on)主要影响的是SiC-MOSFET 处于线性区时的电流,即影响SiC-MOSFET 并联时的静态均流。SiC-MOSFET 并联电流通态电阻影响示意图如图4 所示。

图4 SiC-MOSFET并联电流通态电阻影响示意图

以图4 中两个SiC-MOSFET 并联均流为例,假设两个器件的通态电阻分别为Rds1(on)和Rds2(on),那么在通态情况下,流过两个SiC-MOSFET 的静态电流可以表示为:

由式(3)可知,当并联SiC-MOSFET 处于通态时,流过各个器件的漏极电流Id与其通态电阻Rds(on)是负相关的,由于各个支路的通态电阻Rds(on)不一致,这会导致通态电阻小的支路会流过大的电流,最终造成并联各支路静态电流的不均衡。

定义电流不均衡度为:

式中,Iav为并联电流的平均值,In为第n支路的电流值。另外由于流过电流较大的支路会产生更大的热量,而UF3C065040K3S 的通态电阻Rds(on)是正温度系数的,这会使得大电流支路SiC-MOSFET 的通态电阻因温度升高而变大,进而使得该支路的电流减小,这种负反馈调节能力在一定程度上可以抑制SiC-MOSFET 各支路静态电流的不均衡。

2)阈值电压Vth分散性的影响

通过式(1)可知,阈值电压Vth主要影响的是SiC-MOSFET 处于饱和区时的电流,即影响SiCMOSFET 并联时的动态均流。同时由前面的分析可知,SiC-MOSFET 的开关过程是驱动电路向SiCMOSFET 栅源电容Cgs充放电的过程,所以当并联SiC-MOSFET 使用单一驱动电路时,在其开通过程中,阈值电压较低的支路会先导通,同时承担较大的电流,而阈值电压较高的支路会后导通,承担较小的电流;在其关断过程中,阈值电压较高的支路会先关断,同时承担较小的电流,而阈值电压较低的支路会后关断,承担较大的电流。即SiCMOSFET 的阈值电压Vth会直接影响其并联支路的动态均流。

3 基于栅源补偿电容的均流方法

SiC-MOSFET 动态电流是指SiC-MOSFET 开通和关断阶段通过漏极的电流。影响SiC-MOSFET 动态电流的主要因素有SiC-MOSFET 的阈值电压和栅极寄生参数等[16],针对SiC-MOSFET 并联模块的动态电流不均衡问题,该文基于耦合电感主动均流方法,提出一种基于栅源补偿电容联合漏极磁通约束的动态均流方法。

根据对SiC-MOSFET 开关过程的分析,其开关过程主要是栅源电容的充放电过程。图5 为基于栅源补偿电容的SiC-MOSFET 开通和关断示意图。

图5 SiC-MOSFET栅源补偿电容动态均流方法示意图

图中,Rg为栅极电阻,Cgs为SiC-MOSFET 本身的栅源电容,Ccmp为栅源补偿电容,当驱动信号Vdrive由低电平V0转变为高电平Vs时,栅源电压和充电电流变化如下:

式(5)中ig的方向为驱动器指向SiC-MOSFET,τ为阻容电路的时间常数,其值为Rg(Cgs+Ccmp)。

当驱动信号Vdrive由高电平Vs转变为低电平V0时,栅源电压和充电电流变化如下:

其中,ig方向为SiC-MOSFET 指向驱动器。

由式(5)和式(6)可知,通过栅源极并联小电容的方法可以改变SiC-MOSFET 的充放电时间常数,进而能够改变其开通时间和关断时间,最终可以改善SiC-MOSFET 并联模块的动态电流均衡性。此外,栅源极并联小电容还可以通过减慢SiC-MOSFET的开关速度,改善其开通电流尖峰和关断电压尖峰。

4 实验验证

该文搭建了基于SiC-MOSFET 固态开关的样机和其实验平台,样机的额定电压、额定电流与额定负载值分别为28 V、5.6 A、5 Ω。通过两组开关器件并联,针对SiC-MOSFET 的并联均流电路进行实验,将分别测试未采取均流措施、采取栅源补偿电容联合漏极磁通约束措施两种工况,对SiC-MOSFET 漏极电流的动静态波形进行比较。

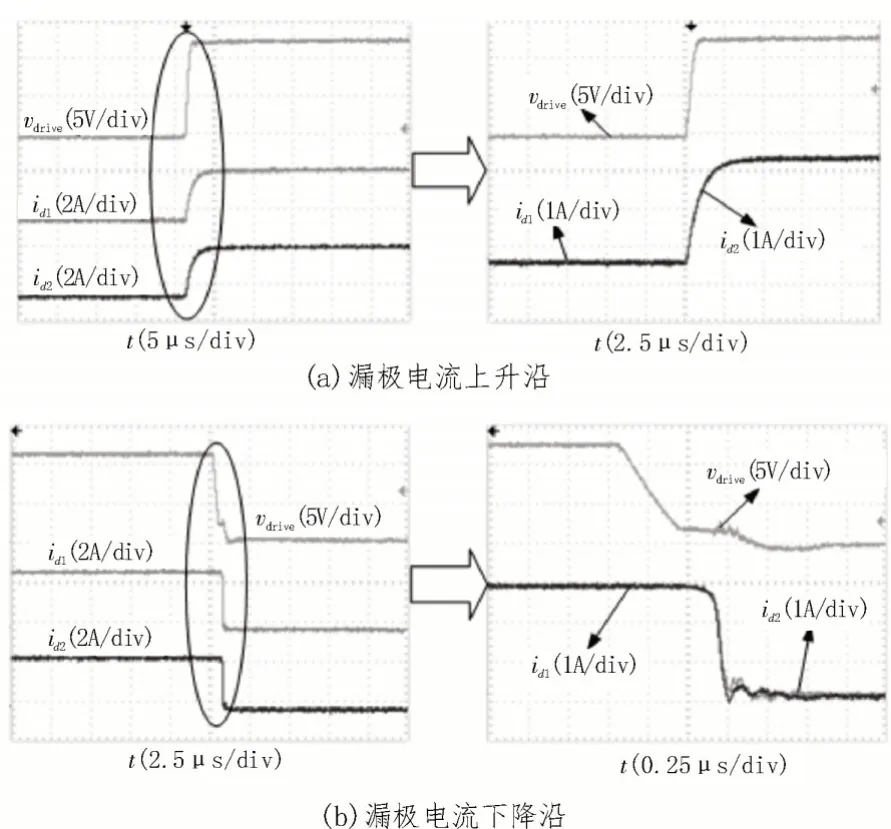

图6(a)、(b)为未采取均流措施时的SiC-MOSFET并联支路实验波形图,其中,Vdrive为两条支路上SiCMOSFET 的驱动电压,id1和id2分别是支路1 和支路2的漏极电流,从图中可以看出,未采取均流措施的情况下,在SiC-MOSFET 开通和关断的瞬间,支路1 和支路2 的电流会出现很明显的不均衡。

图7(a)、(b)为采取栅源补偿电容措施时的SiCMOSFET 并联支路实验波形图,其中支路1 和支路2的漏极补偿小电阻均为0.1 Ω,从图中可以看出,SiC-MOSFET 并联支路通态时的电流不均衡现象得到了明显的抑制,支路1 与支路2 的动、静态电流基本平衡。

图7 SiC-MOSFET并联支路动态和静态均流实验波形图

通过对上面对比实验结果的分析可知,基于栅源补偿电容动态均流方法可以有效抑制SiCMOSFET 并联支路动、静态电流的不均衡。

5 结束语

该文针对配电网台区低压柔直互联提出了固态开关方案,并针对基于SiC-MOSFET 的固态开关的并联支路的均流控制方法。从并联均流的影响因素上分析,包括SiC-MOSFET 本身的通态电阻、阈值电压和其驱动电路上的栅极电阻、栅极电压以及功率回路上的各种参数;并提出了一种栅源补偿电容动态均流方法,可以在一定程度上抑制其动态电流的不均衡。最后,通过实验验证证明了方法的有效性。