H.265/HEVC 熵解码的分组并行流水线实现

2023-11-10王世豪周志刚郭旭殷先英薛晓娜赵靖宇

王世豪,周志刚,郭旭,殷先英,薛晓娜,赵靖宇

(杭州电子科技大学 电子信息学院,浙江 杭州 310018)

0 引言

与H.264/AVC 相比,视频压缩标准H.265/HEVC 能够在相同的图像质量下实现更低的码率,即更高的压缩比[1]。基于上下文的二进制自适应算术编码(Context-Adaptive Binary Arithmetic Coding,CABAC)是H.265/HEVC 支持的熵编码方案。CABAC 在熵编码方案中具有极高的数据压缩率,相对于另一种熵编码方案基于上下文的自适应可变长编码(Context-Adaptive Variable Length Coding,CAVLC),在同等编码质量下,CABAC 可节约10%~15%的比特率。

在CABAC中,上下文建模的保持与更新需要大量的计算和内部存储器件的访问。在解码过程中,语法元素需要其前面的语法元素来确定上下文地址,在每个binVal 被解码获得时,解码过程需要检查流是否被更改或保持在相同的语法元素中。因此,解码过程比编码过程具有更多的依赖性。同时,在标准的熵解码流程中,由于位流指针(binIdx)的存在,导致熵解码过程串行程度过高,占用了较长的解码时间。导致CABAC 模块成为视频解码器的吞吐量瓶颈。因此,有必要针对以上问题设计一种高并行、高吞吐量的硬件结构。

目前CABAC 解码器的工作可以分为3类,分别是基于流水线的时域并行性扩展、基于单周期的多位解码、基于预测的解码和基于子区间重排序的解码。文献[2-3]通过流水线的方式扩展时域并行性,但码流之间的高数据依赖使反馈环路串行程度过高,导致在流水线架构中过多的时钟冗余。文献[4-9]通过增加额外的解码逻辑来增加每周期的解码输出位,但该种方法实现的时钟速率较低。文献[8-9]通过使用基于预测解码的方法节省了预存解码信息的硬件开销,但带来了额外的关键路径延迟,且有较高的预测失误惩罚,导致了较低的吞吐量。文献[10]提出适用于HEVC 的多路并行硬件CABAC 解码器架构。该CABAC 解码器采用multi-bin解码方式,其吞吐量可达到3 026 Mbins/s。这种结构改进算术编码(子区间重排序),缩短了关键路径,但这种架构前端的码流控制容易出现性能瓶颈。文献[11]在算术编码子区间重排序的基础上,采用5 级流水线的结构,进一步使用锁存器来减少熵解码的面积开销,布局布线后可实现峰值为1 696 Mbins/s 的解码性能。但使用子区间排序后,编码器和解码器必须同时使用才能保证编解码一致性,实用性不高。

针对上述方法存在的不足,本文根据CABAC 解码算法特点和FPGA 硬件高并行的特性,提出了一种多路并行的CABAC 解码器。通过将语法元素分组并行处理,减少了内部寄存器使用与访问次数,优化了关键路径,增加了CABAC 解码器的吞吐量,并且在编码端不需做任何特殊配置,所提出的结构实用性很高。

1 CABAC 解码

CABAC 解码器架构如图1 所示,由上下文建模器、二值化解码器和去二值化解码器组成。图1 箭头方向表示数据及控制。其中,二值化解码器依据不同语法元素的解码通路分为常规算术解码、旁路解码和终止解码。

图1 CABAC 整体算法架构图

常规算术解码模块适用于解码概率分布不均匀的语法元素,需要估计符号的概率,关键路径较长。其算法流程如图2 所示,其中stage1 为区间划分与位流判决,stage2 为重归一化工程。首先,初始化算术解码引擎:区间大小ivlCurrRange 和偏移量ivlOffset。对于Main 档次,ivlCurrRange 初始值为510,ivlOffset初始化为输入码流的高9 bit。然后以ivlCurrRange 的高2 位和概率状态索引pStateIdx 为查找表索引,查表得出小概率区间值RLPS 值、小概率状态transIdxLps 以及比特流左移的位数。最后,根据这些数据和当前ivlOffset 值一起解码出1 bit 的二进制值binVal,将更新后的上下文变量valMps、pStateIdx 合并为上下文模型,回写到上下文存储器中。同时,区间大小ivlCurrRange 和ivlOffset 进行重整归一化处理,即ivlCurrRange 向左移位,ivlOffset 向左移动位并与输入的比特流相加得到更新后的偏移量ivlOffset,始终保证ivlCurrRange 的值大于等于256。

图2 常规算术解码算法流程图

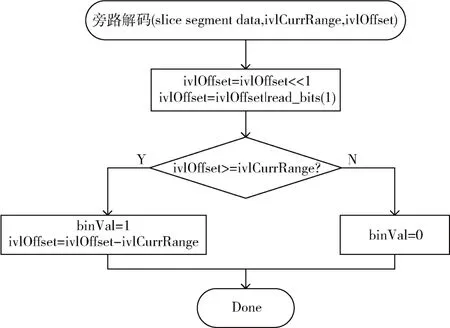

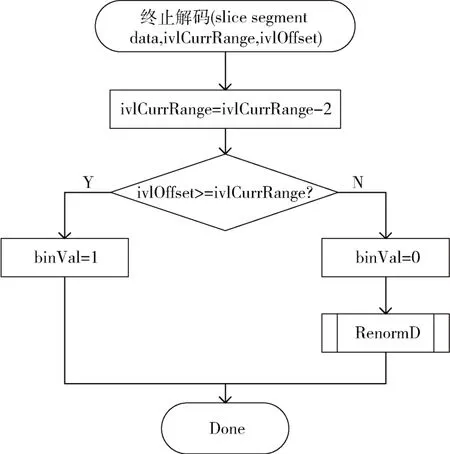

与逻辑复杂的常规算术解码模块不同,旁路解码模块适用于解码近似均匀分布的语法元素,无需上下文建模,从码流控制模块直接过渡至旁路解码模块。图3 为旁路解码算法流程图。这个过程的输入是位流、偏移量和区间范围,输出是解码bin 值、偏移量和区间范围的更新值。当终止解码模块只用于解码少数语法元素,如Slice 解码结束标志,执行的终端解码过程。终端解码的流程如图4 所示。

图3 旁路解码算法流程图

图4 终止解码算法流程图

2 多路并行流水线实现结构

针对传统CABAC 解码器吞吐量稳定性较差的问题,提出一种流水线结构,如图5 所示。根据H.265/HEVC 码流的特性,对二值化解码器部分进行了优化。其中,不同种类的二值化解码为并行运算,在调用频率最高的常规算术解码模块内部也采用了并行优化。考虑到在HEVC 解码器中CABAC 熵解码模块是首先接收比特流的模块,因此输入端采用串行输入。

图5 CABAC 解码器流水线架构图

完整的CABAC 解码器总体为3 级流水线设计,首先第1 级流水线中比特流经过语法元素状态机,通过解析不同语法元素所需要经过的不同数据通路,输出各个解码模块所需使能信号;第2 级流水线中上下文状态机通过判别上一级流水线收到的使能信号建立特定的上下文索引寄存器,对应的语法元素与初始化信息一并存储在上下文模型存储器中,这也是在后续解码过程中存储上下文更新模型的地方,这一模块将准备好的使能信号、上下文模型与slice data 送入状态选择器;第3 级流水线为解码器中的解码部分,解码出二进制的语法元素值binVal 后传入语法元素各自所在的模块中进行去归一化(De-Binarization,DB)。其中常规算术解码根据不同的语法元素的上下文建模大小并行为5路,减少了CABAC 解码过程中的不同大小的语法元素之间的寄存器等待。采用流水线的设计,减少了语法元素的解码延时,提高了硬件资源的利用率。

由于常规算术解码算法中各模块之间相关性很强,且不同的语法元素所需的上下文建模存储位宽不同,为提高该模块的吞吐量,提出一种基于上下文模型位宽的并行硬件结构,如图6 所示。

图6 基于上下文模型位宽的5 路并行结构

根据不同类型语法元素所需上下文建模位宽的不同,将常规算术解码分组并行为5路,分组为样值自适应偏移组、编码单元组、预测矢量组、残差系数组、sig,在不同组模块内完成上下文模型读取与上下文模型更新,解码计算模块在模块内单独进行例化。通过整体流水线结构中第2 级流水线中输出的控制信号控制不同组的解码流程。其中单路常规算术解码硬件结构如图5 所示,结合stage2 重归一化环节的判断左移并补位的结构,本模块输入裁切为当前码流的高5 位。在stage1中,各组需要通过查表进行概率状态转移和概率区间的读取,状态转换数据没有规律,为了提高吞吐量,在硬件设计时使用LUT 预存储需要更新的数值。在stage2中,根据硬件特性,将原本的比较结构改为移位判断选择器结构,通过直接判决ivlCurrRange 最高位,减少了关键路径,增加了吞吐量。

3 FPGA 实现与性能验证

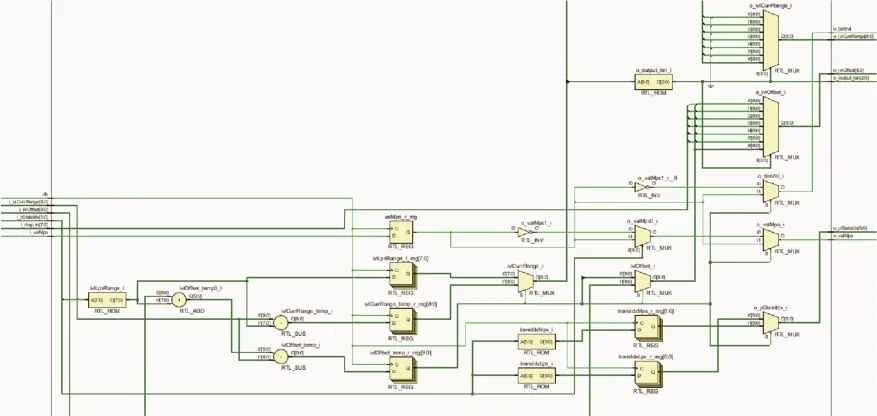

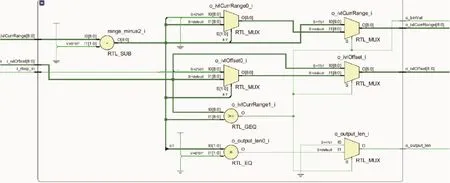

整体的硬件实现整体结构如图7 所示,算术解码模块、旁路解码模块和终止解码模块的硬件实现如图8~图10 所示。

图7 提出的CABAC 解码器硬件架构图

图8 单路常规算术解码硬件实现

图9 旁路解码硬件结构

图10 终止解码硬件结构

单路常规算术解码模块输入的rbsp 为高5位,结合重归一化部分的判断后左移读取位流补位的结构,因此输入舍弃了低3 位。在stage1中,最重要的步骤是通过查表进行状态的转移和ivlLpsRange 的读取,因为表中数据没有规律,无法进行逻辑推导,因此在设计时使用两个LUT 预存需要更新的数值。在stage2中,通过优化原始的比较大小改进为逐位判断选择器结构,ivl-CurrRange[8]等于1时,ivlCurrRange 必大于256。在硬件电路中减少判断所需的路径,提升了吞吐量。

旁路解码模块与终止解码模块结构较简单,其中两模块输入均为1位,旁路解码整个过程区间值保持不变,首先对ivlOffset 偏移量左移1位,同时从比特流中读取1 位用以补位,然后进行判断,输出二进制的语法元素值和更新后的ivlOffset。终止解码直接对偏移量与区间范围进行比较,判别是否进行常规算术解码中相同的重归一化并输出bin 值。

为了验证所提出的熵解码分组多路并行流水线结构,基于FPGA 进行了实现和性能评估验证,电路结构采用Verilog HDL 设计,在XC7Z035-FFG676-2 芯片上综合通过,使用ModelSim 进行仿真,并与HM16.19 测试平台中的结果进行比较,结果一致,证明本文设计的正确性。如图11 所示,首先对应语法元素所在分组的使能信号拉高,驱动该解码模块工作,输出更新的区间值和偏移量,结束常规算术解码的程序后,该使能信号重新拉低,旁路解码的使能信号拉高输出更新的偏移量。本设计中偏移量和区间值的更新均延后了一个时钟周期进行。

图11 ModelSim 仿真图

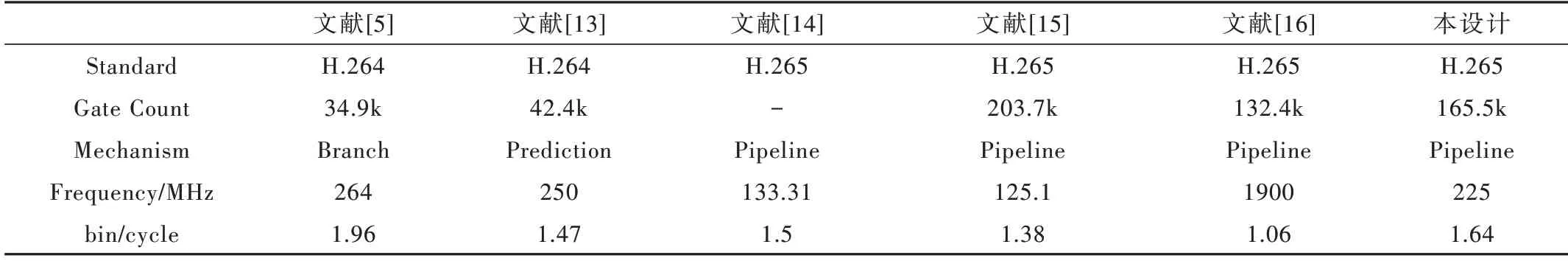

本设计所占用的资源如图12 所示,与同类工作的对比如表1 所示。通过对比可知,本设计在减少板上资源的情况下,提高了每周期输出的语法元素数量。

表1 同类工作性能对比

图12 硬件资源消耗

4 结论

本文提出了一种基于H.265 的CABAC 解码的硬件设计,由于CABAC 解码过程中有极高的数据依赖性,在解码过程中十分消耗时间。因此,通过分析并优化CABAC 解码过程中运行占比最高的常规算术解码模块,根据不同的语法元素的上下文模型,分组并行处理常规算术解码,提高了该模块的工作效率。系统采用Verilog 语言进行设计,经过综合、仿真验证,证明了该模块工作的正确性。通过与同类工作对比,本工作在逻辑面积的使用上进行了优化,减少了寄存器的使用,增加了整体的解码效率。