一种应用分段式电容阵列的20 MS/s 10-bit SAR ADC*

2023-11-10崔海涛张继陈玉蓉胡伟波李超润

崔海涛,张继,陈玉蓉,胡伟波,李超润

(1.南开大学 电子信息与光学工程学院,天津 300350;2.中国电子科技集团公司第五十八研究所,江苏 无锡 214063;3.北京大学深圳研究生院,广东 深圳 518055)

0 引言

模拟数字转换器(ADC)是信号链的核心器件,是沟通模拟信号与数字信号的桥梁。自然界中大部分信号都是时间连续、幅值连续的模拟信号,比如温度、压强、速度等。因为数字信号抑制噪声的能力要强于模拟信号,并且方便计算机处理,所以在信号处理时,通常需要ADC 将连续的模拟信号转换成离散的数字信号。ADC对芯片系统的整体性能起着决定性的影响,因此得到了学术界和工业界的极大关注[1]。ADC 有多个种类,如逐次逼近 型(SAR)[2-3],∑-Δ型[4-5],Flash型[6-7]等。其 中SAR ADC 的应用范围最广,其通过对采样信号进行二次幂地逐次逼近,使ADC 内部的数模转换器 (DAC)产生的电压逼近于采样得到的信号,最终实现对采样信号的量化。随着SAR ADC 的发展,多种新的架构被提出来[8-11],这些新思想新技术极大促进了ADC 的发展。传统SAR ADC 的电容阵列是以二次幂的形式增长的,当DAC 的位数较多时,最大电容的容值就会很大,该电容翻转时所需要的稳定时间较长,这不利于ADC 的快速转换。此外,对于SAR ADC 而言,比较器的失调电压直接体现在ADC 的输出中,使ADC 的输出相对输入信号存在直流偏移。

针对上述问题,本文基于180 nm CMOS 工艺设计了一个10 bit 20 MS/s 采样率的SAR ADC。该ADC 采用分段式电容阵列设计,缩短了量化过程中大电容翻转后所需要的稳定时间,提高了量化速度。本文还提出了一种新颖、高效的比较器校准方法,有效降低了比较器的失调电压,进一步提高了ADC 的精度。此外,本文对不同结构中电容翻转后参考电压的恢复时间进行了建模分析,为分段式电容阵列对ADC 量化速度的提高提供了理论支持。本设计实际测试结果表明,在1.8 V 电源电压,20 MS/s 采样频率下,该ADC 消耗了0.81 mW 的功耗,实现了58.24 dB 的信号噪声失真比(SNDR) 。

1 一般的SAR ADC 整体结构

传统的SAR ADC[12]如图1 所示,一般由DAC、比较器、采样电路、逻辑控制电路组成,其原理是基于二进制搜索算法进行逻辑转换。DAC 的类型一般有电容型、电阻型、电流型等,其中应用最广泛的是电容型DAC。其工作原理为,采样电路将输入信号保存在电容阵列中,逻辑电路根据比较器的结果从大到小地逐个控制电容下级板的开关接在VREF 或GND上,使DAC 中的电荷重新分配,DAC 产生的电压逐次地逼近输入信号,当DAC 产生的电压与输入信号足够接近时,DAC 的输入数字码即可看作输入信号的数字码。图1 中电容左上角的数字N表示该电容由N个单位电容并联组成,如图1所示,传统的SAR ADC 的DAC 是由呈二次幂递增的电容阵列构成。对于10 bit 的ADC 而言,其最大电容C9为最小电容C0的256倍,DAC 单侧电容阵列的总电容值Ctot为512C0。

图1 一般SAR ADC 结构

如图2 所示,参考源的简单模型[13]由电压为Vref0的理想源、输出电阻Rout、去耦电容Cout组成。对于片内参考源而言,受限于面积问题,一般Cout不能做得太大,同时,为了减轻电容翻转时对VREF 的扰动,Cout也不能太小,此处取Cout的值为3Ctot。

图2 电容翻转后VREF 恢复示意图

当最大电容C9的下级板由GND 接到VREF时,如图2 所示,由于短时间从VREF 抽取了很大电流,导致VREF 的电压Vref下降了一个Vdrop电压:

随后Vref需要经过tsettling时间恢复到足够接近Vref0,比较器才能进行下一周期比较,以避免结果出错。一般需要恢复到Vref与Vref0的差值小于1/4 个LSB,即:

在恢复过程中,根据一阶RC 充放电模型,Vref随时间的变化可以表示为:

将式(1)、式(3)带入式(2)中解得:

虽然只有当最大电容翻转时Vref才需要如此长的时间恢复,但是由于很难分别控制每一个比较器周期的长度,实际上只能为每一个电容的翻转都留出大于tsettling的时间以供Vref恢复,这显著降低了ADC 的量化速度。

2 改进的系统

2.1 CDAC 结构和工作原理

如图3 所示,本ADC 的DAC 是在传统结构的基础上,用连接开关将10 bit 的 DAC 分成4 bit 的MDAC 和6 bit 的LDAC。若将LDAC 整体看为尾电容,则电容CM5、CM4、CM3、CM2、CM1、LDAC 将组成一个ADC。同理,若将(CL1+CL0)看作尾电容,则CL5、CL4、CL3、CL2、(CL1+CL0)可组成一个ADC,且其电容比例满足式(6):

图3 本文的DAC 结构

这说明,对于这两个ADC 而言,量化相同的信号,其对应电容的翻转方式是相同的。因此,如图4 所示,MDAC 和LDAC 同时采样后,连接开关断开,LDAC 作为一个ADC 开始工作,进行第一阶段量化,在量化出4 bit 的数据后,即CL5、CL4、CL3、CL2完成翻转后,将CL5、CL4、CL3、CL2的结果对应地复制给CM5、CM4、CM3、CM2,随后LDAC 复位,这时,整个电路的状态与MDAC 和LDAC 合并作为10 bit ADC 量化出4 bit 结果后的状态是完全等价的。即图4 中上下两个ADC 在图示状态时是完全等价的。此后LDAC 作为低位6 bit 电容进行第二阶段的量化,再量化出6 bit 数据。实际上,对于这种分段式电容阵列而言,其电容阵列并不一定需要二次幂分布,只需满足式(6),即可按照上述方式工作。

图4 新结构在完成翻转结果复制及复位后与传统结构的等价性

在这种结构下,最大的Vdrop在第一阶段量化CL5翻转时产生,有:

带入式(2)得:

可见新结构VREF 的稳定时间只有传统结构的55%,此种结构的每个电容翻转后VREF 所需的稳定时间大大减少了,从而加快了ADC 的量化速度。

2.2 工作时序

如图5 所示,ADC 上电后先进行比较器的一次性校准,随后开始正常的采样-量化周期。在采样阶段,采样开关和连接开关均闭合,MDAC 和LDAC 同时对输入信号进行采样。采样阶段结束后,采样开关先断开,随后连接开关断开,LDAC 开始进行第一阶段量化,在4 个比较器周期后,输出4 bit 数据,电容CL5、CL4、CL3、CL2完成翻转,第一阶段量化结束。随后连接开关闭合,将CL5、CL4、CL3、CL2的结果对应地复制给CM5、CM4、CM3、CM2,随后LDAC 复位,待电荷重新分配完成、VREF 恢复后,开始第二阶段量化。此时,MDAC 和LDAC 作为一个整体,且电容CM5、CM4、CM3、CM2已经翻转完成,由LDAC 再次根据比较器的结果进行翻转,得到剩下的6 bit 数据。

图5 ADC 工作时序

2.3 比较器及校准

比较器是ADC 的核心模块,对于高速ADC 而言,比较器在较短时间内得出比较结果对于速度的影响是至关重要的。因此本设计采用了一种将第二级latch 电路的输入对管放在反馈回路中的设计,以增加比较器的速度。

本设计采用的比较器结构如图6 所示,CLK 下降沿比较器对输入信号进行比较,当VIP>VIN时,输出OUTP 为高电平,OUTN 为低电平,当VIP<VIN时,输出OUTP 为低电平,OUTN 为高电平。CLK 高电平比较器复位,OUTP 和OUTN 均为高电平,电路电流为零。MP1和MN1 是一个反相器,用于将时钟信号CLK 反向,以控制其他MOS 管。MP2 管在CLK 下降沿到来时为输入对管提供电流,第一级放大器工作,当CLK 为高电平时,该MOS 管截止以降低功耗。MP3 和MP4 是整个放大器的输入对管,负责将输入的差分信号放大。MN2 和MN3 是第一级放大器的负载对管,其栅极接CLK 信号,CLK 低电平时截止,作为MP1 和MP2 的输出负载进行工作,CLK 为高电平时,MN2 和MN3 导通,将DIP、DIN拉到低电平使MN4 和MN5 截止,从而切断第二级latch电路的上拉和下拉。MP5 和MP8 是复位上拉对管,其栅极接时钟的反相信号CLKB,使得当CLK 处于高电平(CLKB 低电平)时,这两个MOS 管导通,将输出拉至OUTP=OUTN=VDD 的状态。MP6 和MP7 是第二级latch 电路的正反馈上拉对管,在CLK 下降沿到来时将OUTP 和OUTN 中较高的电压拉至VDD。MN4 和MN6是第二级latch 电路输入对管,将第一级放大器的输出,经过进一步放大后,由正反馈回路进行处理。MN7和MN10 是第二级latch 电路的正反馈下拉对管,在CLK 下降沿到来时通过MN4 和MN6 将OUTP 和OUTN 中较低的电压拉至VSS。MN6 和MN11 是复位下拉对管,其栅极接时钟信号CLK,当CLK 处于高电平时,这两个MOS管导通将MN4 和MN5 的源极电压拉到VSS。MN8、MN9 和MN12、MN13 是用于校 准Offset 的辅助正反馈下拉管,通过调整MN9 和MN13 的栅极电压,来调整latch 电路中P 端和N 端的下拉能力,进而将比较器自身的输入失调电压补偿掉。

图6 比较器及其校准电路

校准的工作过程如图7 所示。

图7 比较器校准方案流程图

比较器校准前后的输入失调电压如图8 所示,校准前输入失调电压的标准差为5.59 mV,校准后只有145 μV,可见本文所提出的校准方法能显著降低比较器的输入失调电压。

图8 一次性校准前(上图)后(下图)的比较器失调电压分布图

3 测试结果

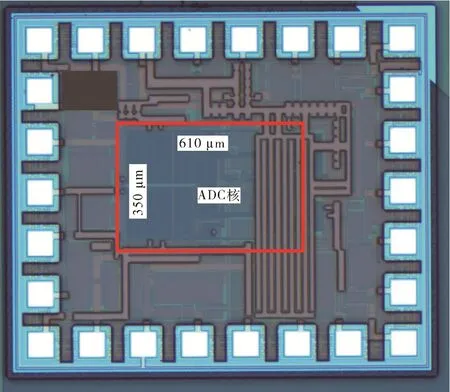

本文所设计的ADC 应用180 nm CMOS 工艺制造,核心电路面积0.213 5 mm2,芯片照片如图9 所示。测试时供电电压1.8 V,输入差分信号-1.2~1.2 V,采样频率为20 MS/s,功耗为0.81 mW。

图9 芯片显微照片

图10 为ADC 对5 MHz 正弦信号采样结果的FFT 频谱,可以看到对该频率的信号实现了55.2 dB 的SNDR。图11 为不同输入信号频率下SNDR 的曲线图,可以看到该ADC 对500 kHz 信号采样的SNDR 达到了58.24 dB,对奈奎斯特频带信号采样的SNDR 达到了53.37 dB。如图12 所示,本设计实现了-0.45~0.3 LSB 的微分非线性和-1.30~0.76 LSB 的积分非线性。本设计与其他同类设计的性能对比如表 1 所示,考虑到本设计是基于180 nm工艺设计制造的,其性能基本上达到了此类转换器的前沿水平。

图10 对5 MHz 信号采样的频谱特性

图11 SNDR 随输入信号频率变化

图12 ADC 的静态特性

4 结论

本文基于180 nm CMOS 工艺设计了一个10 Bit 20 MS/s 采样率的SAR ADC,详细介绍了该ADC 中所采用的分段式电容阵列的原理及工作过程,并对不同结构中电容翻转后参考电压的恢复时间进行了建模分析。此外,本文还提出了一种高效的比较器校准方法,并对其校准的效果进行了仿真验证。ADC 的实际测试结果表明,在1.8 V 电源电压,20 MS/s 采样频率下,该ADC 消耗了0.81 mW 的功耗,达到了58.24 dB 的信号噪声失真比(SNDR),基本上达到了此类ADC 的前沿水平。

表1 本设计与其他同类设计的对比