SoC 芯片的RomCode 设计与FPGA 验证研究

2023-11-10张梅娟张明月杨楚玮朱心杰

张梅娟,张明月,杨楚玮,朱心杰

(中国电子科技集团公司第五十八研究所,江苏无锡 214035)

近年来,随着移动设备的爆发式需求以及信息化产业的推动,带来了巨大的电子信息类产品的功能和服务需求[1]。嵌入式处理器作为移动设备的心脏,其应用场景更加丰富的同时,对其各项指标也提出了新的需求[2-3],这也对嵌入式处理器的集成电路设计提出了新的挑战。集成电路的设计为了更加完美地满足以上需求,需要有更多的设计思考以及更丰富的验证方法,而作为处理器关键组成部分的RomCode 亦如此[4]。

RomCode 在芯片上电复位后运行,其核心目标是使得处理器可正常加载、运行位于外部存储介质中的用户级程序[5-6]。现代处理器的基本技术指标是多核特性,基于多级Cache 结构,在硬件层面提高CPU 指令的执行、调度效率[7],而RomCode 作为处理器的一部分必须要支持处理器多核启动功能。

由于ARM 内核具有高性能、低功耗、高可靠性、定制性强以及生态完整等特点,已成为嵌入式领域处理器SoC 芯片的不二之选[8]。该文提出的基于ARM 多核处理器SoC 芯片的RomCode,可对芯片上电后的时钟进行管理,同时具备从芯片外接的TF卡、SD卡、emmc 等存储介质中加载用户级程序,支持常见的多核操作系统,如Linux、Vxworks 等。同时,为了保证集成电路设计阶段RomCode 设计的正确性,在Palladium 与Haps 两种FPGA 环境下进行充分的芯片原型验证。

1 RomCode设计

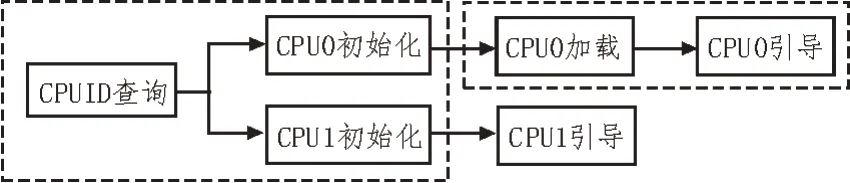

设计的RomCode 架构框图如图1 所示,其中CPU0 为主核、CPU1 为从核,后文不再赘述。主核加载引导包括处理器内核初始化、最小系统外设初始化以及用户级程序加载引导等;多核初始化由主核初始化和从核初始化组成;多核引导设计首先对多核启动所存在的技术问题进行了讨论,并提出了解决方案,然后给出了主核引导从核启动的具体实现。

图1 RomCode架构框图

1.1 地址空间分配

地址空间分配是RomCode 架构设计的重要组成部分,它决定了RomCode 程序的存储结构划分和加载的用户级程序在内存中的存放位置[9]。

地址空间由ROM区、SRAM 顶部区、SRAM 底部区三部分构成:

1)ROM 区:text 段用于存储RomCode 程序对应的机器指令,该部分是固定的,程序存储地址和CPU的运行地址保持一致,rodata 段用于存储只读数据,如程序中使用的宏定义。

2)SRAM 顶部区:用于存储多核运行的堆栈区、bss 段区、data 段区。

3)SRAM 底部区,用于存放从外部存储介质中加载的用户代码头部信息和用户代码。具体空间分配如图2 所示。

图2 RomCode空间分配框图

1.2 主核加载引导

对用户级程序完成正确的加载和引导是RomCode 实现的核心功能,该段程序负责从不同类型的外部存储介质中加载用户级程序到RAM 中并引导运行[10]。

用户级程序的加载阶段,RomCode 将其从外部存储介质中加载到对应的内存位置,并进行数据正确性校验[11],如图3 所示。

具体步骤如下:

1)该系统支持三种类型的存储介质,分别是TF卡、SD卡、emmc,RomCode 按此顺序依次扫描。

2)从相应的存储介质中读取用户代码的配置区信息,并对配置区的有效性进行校验,信息正确性由密钥和信息摘要算法保证,配置区正确,则进入步骤3),反之,则进入通信模式,并反馈错误位置。

3)从相应的存储介质中读取用户级程序,根据配置区的源地址、目的地址、用户代码大小等信息,将用户代码加载到SRAM 中,对用户代码进行循环冗余校验CRC,用户代码正确则进入引导阶段,反之,则进入通信模式,并反馈错误位置。

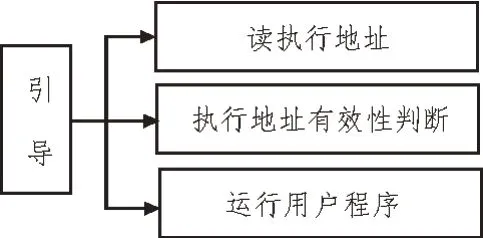

用户级程序的引导是在正确加载用户配置区和程序后,如图4 所示。

图4 引导阶段框图

具体步骤如下:

1)读取用户代码配置区中的程序执行地址参数。

2)对该地址参数进行有效性判断,检查该参数是否处于RAM 的有效地址区间,即用户代码存储区。

3)设置程序计数寄存器PC,运行用户级程序。

1.3 多核初始化

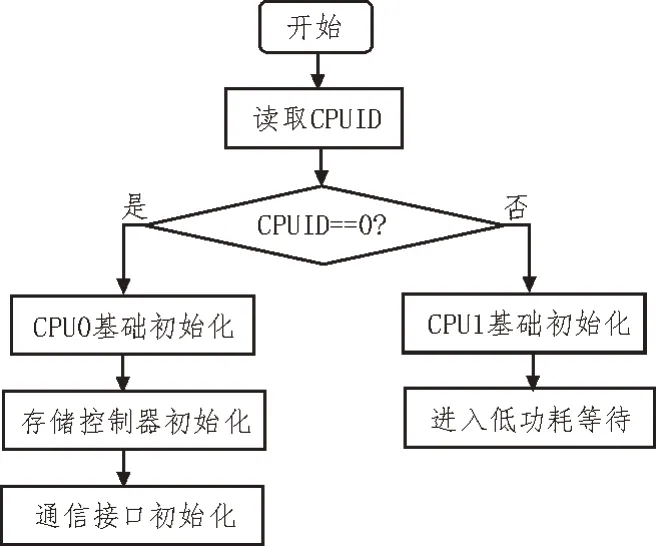

多核初始化包括了CPUID 判断、内核基础初始化、主核和从核初始化路径选择、最小系统外设初始化等部分。

内核基础初始化是配置内核模块的过程,为RomCode 中C 代码准备安全可靠的运行环境。初始化步骤包括异常处理配置、特权模式配置、关闭MMU、关闭L1 Cache,如图5 所示。异常处理配置为该ARM 处理器的七种异常提供异常处理;处理器模式配置将CPU 配置成特权模式;内存管理MMU和L1 Cache 通过系统协处理器CP15 将MMU 和L1 Cache 设置为禁止状态,减少异常的发生。

图5 内核基础初始化

根据CPUID 信息区分出主核与从核,并跳转至不同的内核初始化分支,若为主核,则进行最小系统外设初始化,若为从核,则进入到低功耗等待模式,如图6 所示。

图6 多核初始化流程图

1.4 多核引导

1.4.1 关键问题

多核处理器架构主要包括对称多核处理器(SMP) 和非对称多核处理器(AMP)两种。该文所述的处理器SoC 芯片为SMP 模式,其最大的特点是处理器的所有资源均共享,如操作系统、总线、内存以及外设资源等[12]。另外,用户级程序的加载引导由主核完成[13]。

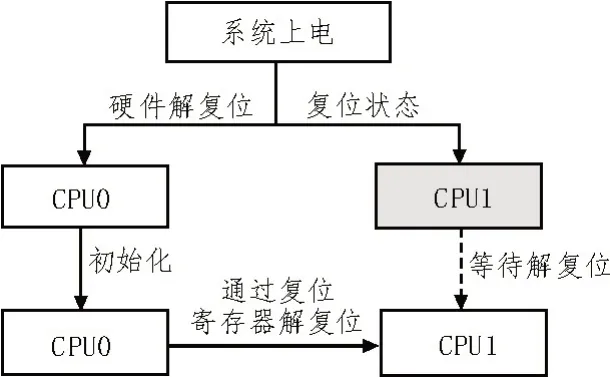

SMP 模式下,多核启动时会引发资源抢占[14],从而导致程序的乱序执行。为解决该问题,该文所述RomCode 设计了一套多核启动复位系统,如图7所示。

图7 多核顺序启动过程

首先,系统上电后,复位系统直接对CPU0 进行硬件解复位,而将CPU1 强制处于复位状态,操作系统启动后由CPU0 完成对CPU1 的解复位操作,以此决定各CPU 的启动顺序。

其次,各CPU 运行同样的用户级程序,势必导致共享资源的重复初始化,引起程序异常,常见问题诸如共享的L2 Cache 被CPU0 初始化并使用,CPU1 再次初始化L2 Cache,会导致严重的Cache 一致性问题,引发系统崩溃。为此,该RomCode 将CPU0 和CPU1 的初始化区分开来,避免对同一资源的重复初始化。具体的措施包括:

1)通过查询CPUID寄存器确定当前运行RomCode程序的CPU 核心,以此区别各CPU 初始化的引导路径,以实现主、从核的特定功能。

2)提供CPU1 的操作系统入口地址寄存器,由CPU0 配置该寄存器。CPU1 完成初始化配置后,则加载入口地址寄存器,获取CPU1 下一步运行的代码;此时,CPU1 即将运行的代码已跳过了资源初始化部分,避免了缓存重复初始化导致的Cache 一致性问题。

3)提供CPU0 软中断唤醒(SGI)和CPU1 等待中断唤醒(WFI)功能,CPU1 进入WFI 模式后,处于低功耗模式,等待CPU0 发送SGI 进行核间唤醒,有利于CPU0 对CPU1 进行唤醒安排,保证各CPU 有序执行。

1.4.2 多核启动流程设计

相对于单核RomCode 程序,SMP 模式的多核处理器的RomCode 需要结合芯片设计,解决多核启动的顺序和CPU 重复初始化共享资源两大问题。该节将详细介绍RomCode 如何结合硬件设计解决以上问题,顺利完成主核CPU0 对从核CPU1 的启动引导流程。

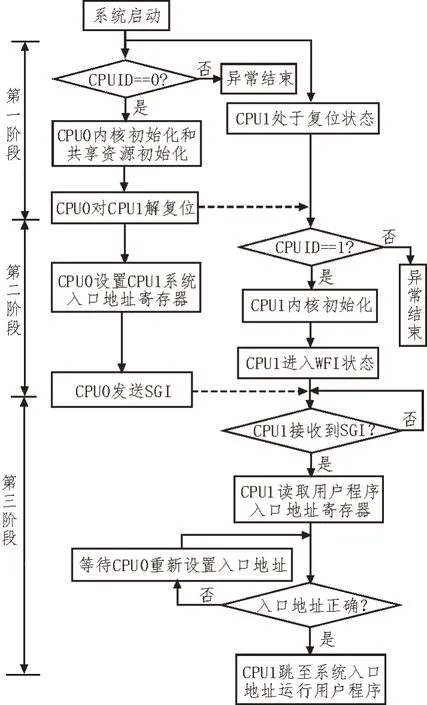

具体启动引导过程如下:

第一阶段:系统上电后,CPU0 硬件解复位,RomCode 查询CPUID 以判断当前运行核心是否为CPU0,然后顺序执行CPU0 的初始化程序和共享资源的初始化,最后CPU0 配置复位寄存器对CPU1 进行解复位。

第二阶段:CPU1 释放复位后,查询CPUID 判断当前运行核心,若为CPU1,则跳转至CPU1 的初始化程序,进行内核初始化,之后CPU1 进入WFI 状态,此时,CPU1 处于上电、无时钟的低功耗状态。该阶段CPU0 的主要工作为配置CPU1 系统入口地址寄存器,为真正进入用户级程序做准备,并发送SGI 软中断到CPU1。

第 三阶 段:CPU1 接收到CPU0 发送 的SGI唤醒指令后,读取入口地址寄存器的值,RomCode 检查该值是否处于有效的地址区间,如SRAM 或DDR 内存等,若有效,则设置PC 值并跳转至入口地址处运行用户级程序。

具体启动引导流程如图8 所示,图中左侧为主核对从核启动的配置,右侧为从核的启动流程。

图8 多核引导流程

2 FPGA原型验证

2.1 Palladium FPGA原型验证

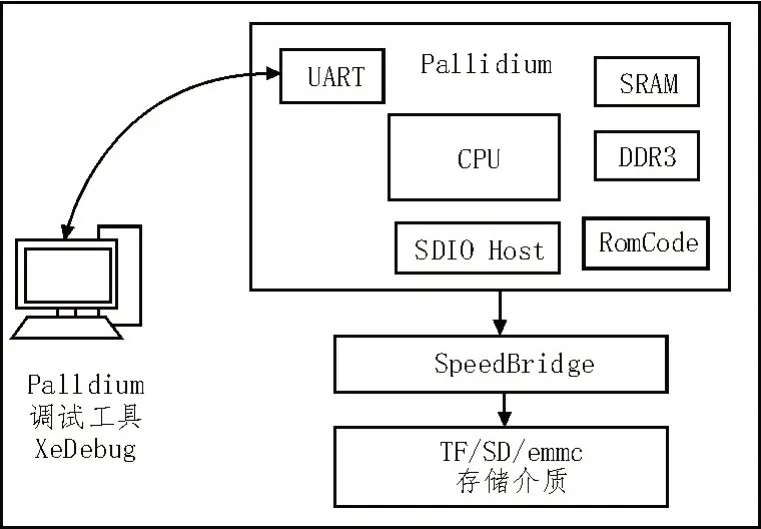

基于Palladium FPGA 对RomCode 进行的原型验证,可获取到RTL 级别的调试手段,并同芯片RTL 设计保持同步,通过时序波形图准确地分析芯片的运行状态[15]。验证环境如图9 所示。

图9 Pallidium FPGA原型验证环境框图

其中,RomCode 存储于芯片内部的Rom 空间,用户级程序U-Boot 和Linux 操作系统镜像存储于TF/SD/emmc 中,由RomCode 将U-Boot搬移到SRAM 中运行,再由U-Boot 将Linux 操作系统镜像搬移到DDR 中运行,在Linux 操作系统中使能处理器多核功能,由RomCode 支撑处理器运行于多核状态。

基于芯片验证EDA 工具verdi 分析RomCode的运行情况,从XeDebug 的终端可观察到U-Boot的启动信息,通过verdi 时序分析图可查看到TF 卡工作时钟被分频控制为10 MHz;UART 总线时钟为200 MHz,基于此进行时钟分频,设置UART 波特率为115 200 bps。通过verdi EDA 可看出主核、从核均从PC 为0 处正常启动。

2.2 Haps FPGA原型验证

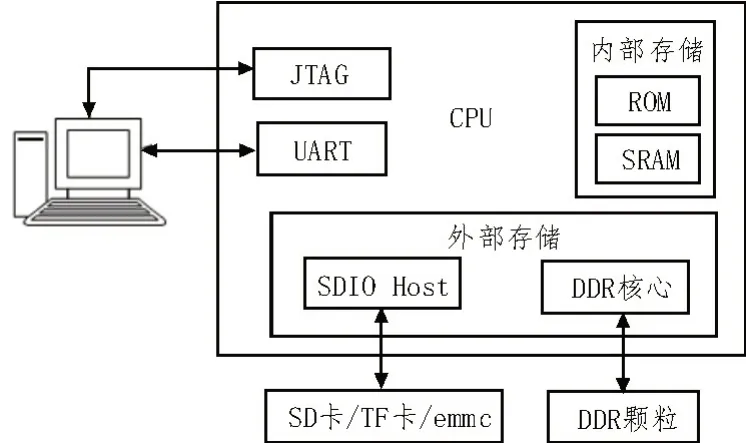

Haps 作为先进的FPGA 原型验证工具,提供了更为真实的硬件环境[16],极大地丰富了调试手段,可以加快软件的开发、迭代周期[17]。而该文基于Haps验证RomCode的CPU 启动、多核等功能。Haps FPGA原型验证环境如图10 所示。

图10 Haps原型验证环境框图

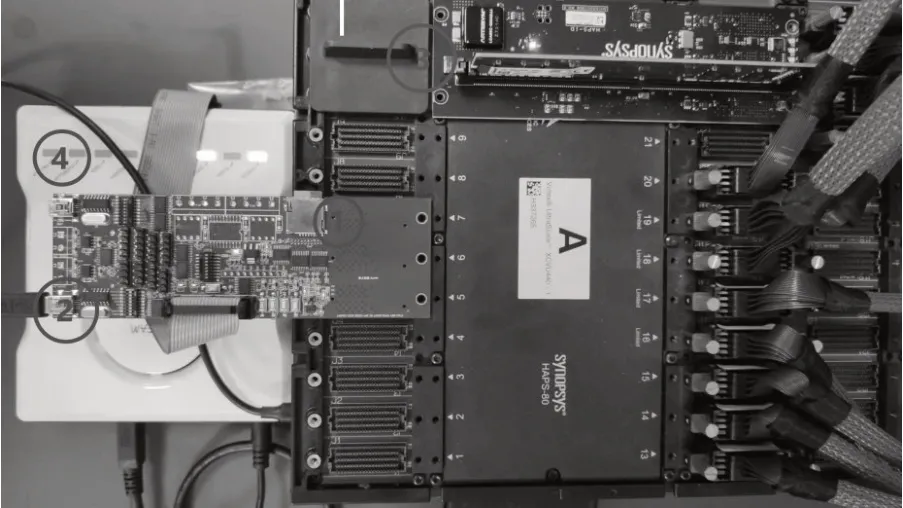

硬件环境如图11 所示,其中,RomCode 固化于bitfile 中,U-Boot 及Linux 操作系统镜像存储于图中标示1 的TF 卡,由RomCode 将U-Boot 搬移到标示3的DDR 内存中运行,基于标示2 的串口将CPU 信息输出到上位机用以查看其内部运行状态。同时,辅之以标示4 的JTAG 调试工具可快速定位CPU 异常。

图11 验证硬件环境

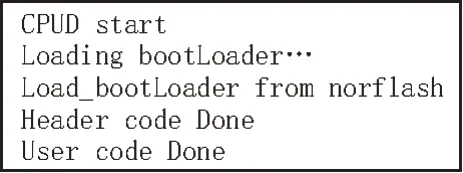

芯片上电解复位后,由主核运行程序,从TF 卡中获取镜像文件并进行文件正确性检查,若文件镜像正确,则进行镜像文件搬移,反之丢弃。在该实验中,正确的识别到U-Boot 镜像且文件正确,串口输出的打印信息如图12 所示。

图12 CPU0加载U-Boot程序打印

文件正确性校验通过后,由RomCode 负责将UBoot 搬移至DDR 中运行,若搬移正确,则U-Boot 会引导Linux 操作系统的启动,反之,启动失败。在该实验中,U-Boot 运行正常且完成了系统的加载,串口输出的打印信息如图13 所示。

图13 主核程序运行状态打印

该文加载的Linux 操作系统具备多核特性,当其进入到处理器多核启动流程时,RomCode 实现的多核功能被激活[18-19]。若多核启动成功,则通过串口可查看到从核的启动信息,如图14 所示。

图14 kernel从核启动信息

3 结束语

针对该文所述的RomCode 功能点,重点分析了其实现原理,同时,该RomCode 提供了多种外部存储介质接口,保证了用户级程序的存储多样性和安全性。基于Pallidium 与Haps 的FPGA 原型验证体现出该多核RomCode 设计的可行性和功能的正确性,针对多核嵌入式处理器的启动,提供了高效可靠的设计方案和验证方法。