基于ECG 的活体检测与身份验证SOC 设计

2023-10-28王永蔹陈子为杨玉航

王永蔹, 陈子为, 曹 坤, 杨玉航, 谢 帅

(成都信息工程大学电子工程学院,四川 成都 610225)

0 引言

身份识别在金融交易等安全应用领域中已经越来越重要, 传统的密码、智能卡等身份识别方式存在容易被破解、遗忘、复制和被盗窃等风险[1]。 为解决传统身份识别方式存在的种种弊端,提出了根据人体独特的生理特征的生物识别方法,大大加强了身份识别的安全性。 常用的生物识别方案有人脸识别、指纹识别、声音识别等,但是这些常用的生物识别方法易受表示攻击(presentation attacks)[2],如指纹可被乳胶复制,人脸可以被打印或带人脸假体面具,声音也可能被录制。 由于每个人的皮肤电传导性、体重、是否有先天性疾病、心脏和胸腔的位置、形状、大小均不一样,因此每个人的心电图ECG(electrocardiogram)信号均不一样,并且只能在体内测量,难以模拟或复制,具有很高的安全性[3-4]。 而且,心脏运动随着人的生命开始而开始,随着生命的结束而停止,ECG 信号仅能在活体上被采集到,可以作为人内在的活体检测方式。 这样使用人体独特而复杂的心电图信号进行身份识别可以解决目前生物识别中的表示攻击问题。

随着微电子技术飞速发展,IC 设计工艺不断提升,集成度越来越大,出现了系统级SOC(system-on-chip)芯片,将整个电路系统集成到一个芯片上。 基于FPGA 的可编程SOC 由于充分利用了FPGA 的并行性、流水线操作以及软硬件协同设计的优势,目前广泛应用在对智能信号处理算法进行硬件加速方面,以满足其实时性需求[5-6]。 利用ARM 开源的Cortex-M3 微处理器软核,在FPGA 上搭建了一个集心电图采集接口电路、ECG 身份识别电路和串口屏显示接口电路于一体的SOC。 该SOC 控制ADS1292 模块采集心电图数据,并传输到基于PCA 和欧几里得距离度量的ECG 身份识别算法硬件加速器上获得识别结果,再根据识别结果判断被测者身份,将身份识别结果显示在串口屏上。

1 身份识别算法

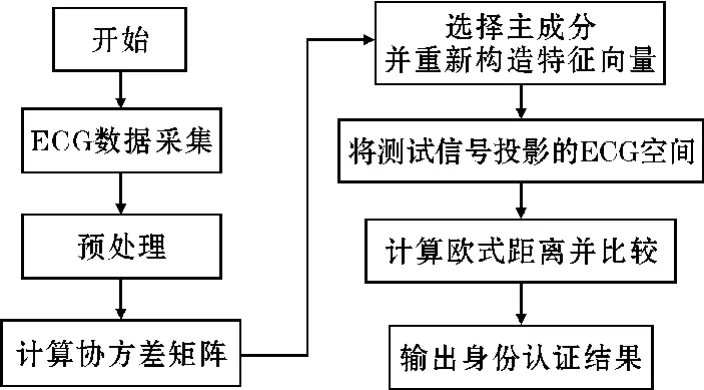

算法流程图如图1 所示。

图1 身份识别算法流程图

1.1 算法介绍

(1)数据获取。 将ECG 训练集存储在大小为N×P的矩阵T中。 矩阵的每一列表示一段ECG 信号,共有P段。 每段ECG 信号采集N点。 所有ECG 信号必须有相同的长度和分辨率,并且都以R 波为中心点。

(2)预处理。 首先求出所有训练集上每个采样点的均值,即对T的每一行求均值:

然后,将训练集上的采样点减去该均值,得到矩阵A:

(3)计算矩阵A的协方差矩阵:

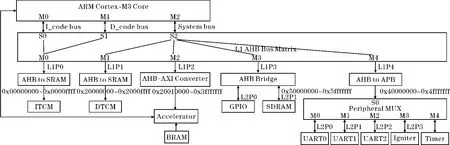

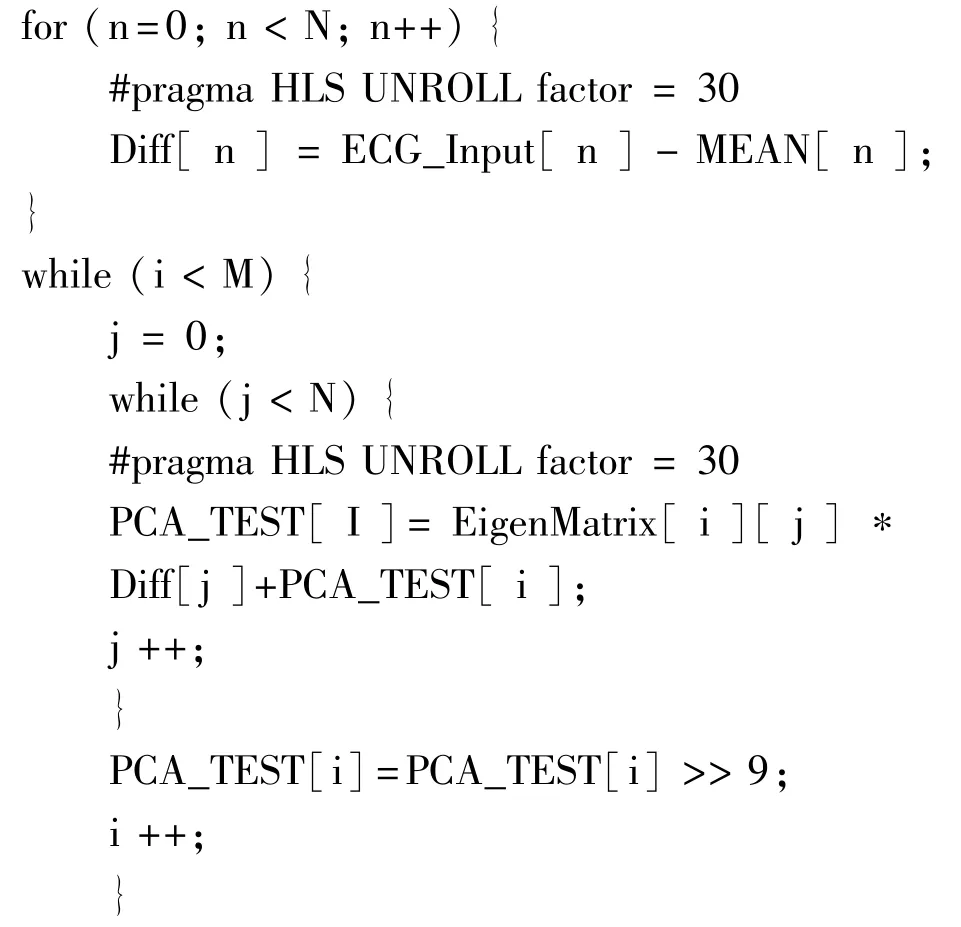

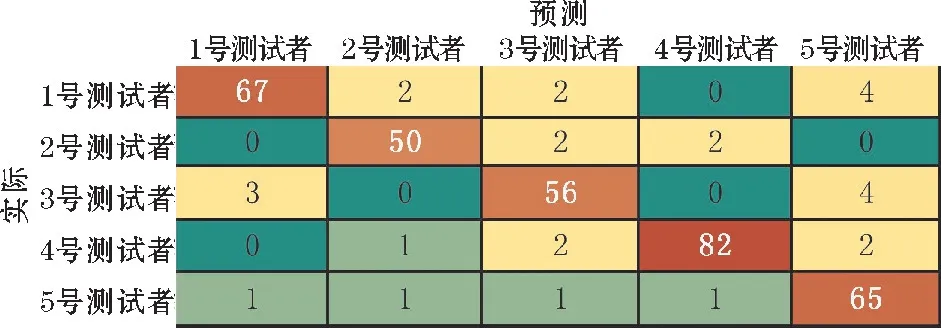

协方差矩阵的计算是运算密集型的,因此需要采取优化算法减少这个运算量。 由于对于N×P的矩阵,其非零特征值的最大数目为P-1 与N-1 中较小的一个。 一般P 计算代理矩阵L的特征向量V与特征值D。 其对角线元素即是L的特征值。 藏匿在英子宫里面的肿瘤细胞,从肆无忌惮的活跃一步步走向奄奄一息的死亡,从放疗初期的极其不适,到放疗中期的剧烈反应,再到放疗后期的渐趋适应。英终究还是挺过来了。英竭力隐忍的经历,再一次告诉她,身体的一切痛楚都是过眼云烟。 (4)选择主成分并重新构造特征向量。 将小于给定门限值的特征值排除掉,这可以大大降低矩阵的维度。 一旦根据前面得到的特征值得到特征向量,就可以根据特征值从大到小(即特征的重要程度)对特征向量排序: 式中,p是大小为P×M的L的协方差矩阵。 由于L是C的代理矩阵,目的是计算C的协方差矩阵而不是L的协方差矩阵,这可以通过下面的方法得到: 式中,E即为协方差矩阵C的特征向量,大小为N×M,表示了训练集T的ECG 信号的最重要的M个特征向量,其包含了训练集中所有的主成分系数,并已在列上按照主成分方差大小降序排列。 (5)将采集的ECG 信号投影到ECG 空间中。 为了将采集的ECG 信号用它的主要特征值表示,需要将其投影到ECG 空间中。 方法是先将采集的待测试的ECG 信号减去均值向量mu,得到I矩阵,然后按照下面的方法投影到ECG 空间中: 其中y为投影到ECG 空间的测试向量。 (6)计算欧几里得距离并比较。 测试向量y与保存在数据库中的P段ECG 信号分别计算欧式距离: 从P个人中找到距离最近的那一个: 也就是找到最小的那个d(i),此时的i即为i*,代表身份识别出的结果ID。 设置一个阈值,并且d*小于设定的阈值时,则可判断是这个人,若其最小值d*大于这个阈值,说明身份认证失败。 算法实现分为身份登记与身份识别(认证)两个阶段。 身份登记阶段采用MATLAB 实现。 首先录入每个人的ECG 数据信息,然后在MATLAB 中运行脚本“[coeff,score,latent,tsquared,explained,mu] =pca(A,'algorithm','svd',...);”得到的coeff 即为前面的E,score 即为前面的p,将Matlab 计算得到的两个矩阵(coeff 与score)和一个列向量(mu)保存到数据库中,然后存储在FPGA 的存储器中。 身份识别阶段采用FPGA 实现,在FPGA 中将实时采集的ECG 信号按照1.1 节中的步骤(2)进行预处理得到x,然后应用硬件加速的方法实现矩阵相乘,实现Y=ET×x得到PCA 投影后的测试向量y,然后将该测试向量y与代表数据库中P个不同人的P个投影训练向量pi分别进行欧氏距离计算,并找出欧式距离最小的那一个,通过这个最小欧式距离值与设定的阈值比较,最终确定是否是已在数据库中登记的人,到底是哪一个人。 由于计算欧式距离时,是否开平方根运算的结果并不影响欧式距离最小值的搜索,因此在FPGA 上用硬件实现欧式距离时,为减少运算量,降低硬件资源开销,计算欧式距离时没有进行开平方根运算[10]。 本设计采用基于ARM 软核[11]的软硬件协同设计方式设计SOC。 其中软件部分采用Cortex-M3 微处理器负责对程序进行控制,对SOC 系统中的ECG 数据进行读取、调度和简单的预处理,以及实现对串口屏的驱动及将身份识别结果显示在串口屏上。 硬件部分(即FPGA 数字逻辑部分)负责将MATLAB 端训练得的系数部署到FPGA 内的存储器中,实现身份识别算法所需的矩阵相乘运算的硬件加速。 本文SOC 采用ARM 公司提供的DesignStart Eval版本Cortex-M3 IP 核[12]作为微控制器核心,SOC 整体部署在FPGA 平台上。 硬件电路部分还包括时钟及复位管理模块、硬件加速器、AHB 外设接口、AXI 桥接器、APB 桥接器和各个AHB、APB 外设接口等,片上系统设计框图如图2 所示。 图2 片上系统设计框图 Cortex-M3 内核使用AHB 总线与外设连接,所以该SoC 的设计采用AHB 总线将内核与片内存储器和GPIO 进行连接,使用APB 总线连接UART、定时器、动作发生器等外设,而APB 总线上的外设通过AHBAPB 总线桥接器与内核进行数据交互与应答。 如图2 所示,Cortex-M3 处理器通过3 根总线与其余部件通信。 其中的I-CODE 总线和D-CODE 总线是基于AHB-Lite 总线协议的32 位总线, 负责在0x00000000 ~0x0000ffff(64KB)之间的取指、数据访问操作。 在使用keil 进行调试时,更新后的软件代码可以通过D-CODE 端写进ITCM。 Cortex-M3 的系统总线控制了Cortex-M3 存储模型的大部分地址区域,包括本系统的DTCM、AHB-AXI Convertor 及AHB、APB 外设部分。 在Cortex-M3 DesignStart Eval 开发套件中提供了一个相当有用的工具CMSDK(Cortex-M System Design Kit)[13],为开发SOC 应用提供了便利。 CMSDK 包含了许多关于AHB 总线的转接模块,例如在本系统用到的基本总线矩阵、AHB-to-APB 总线桥等。 存储器控制器、I/O 接口、定时器以及UART 等,都可以从ARM 和其他IP 供应商处取得。 使用Verilog HDL 编写其他组件可实现整个系统的集成。 由于Vivado 提供的IP 核大多数基于AXI 总线,而采用HLS 设计也能很方便地设计出具有AXI 接口的硬件加速器,为了加快设计进度,本设计采用开源代码Verilog AXI Components[14],实现AXI 总线与AHB总线的相互转换以及AXI 的互联。 本设计采用高层次综合HLS(high-level synthesis)实现身份识别硬件加速器。 HLS[15]是Xilinx 推出的高层次综合工具,是一种由更高抽象度的行为描述生产电路的技术。 通过HLS 的directive 添加对应的约束,可以设置接口的类型、时序、内部资源的占用等,实现对所设计的硬件的自动优化。采用HLS 后,FPGA 开发的时间大大降低,这加速了FPGA 的开发进程,使开发具有了更强的灵活性和高效性,HLS 的逐步完善使FPGA 的开发高效性更进一步。HLS 技术的发展使人们可以把精力放在设计上,而更少地去关注底层的具体实现。 2.3.1 投影ECG 测试信号到ECG 空间 将采集的ECG 测试信号先减去保存在FPGA 存储器上的均值向量,然后投影到ECG 空间上,其代码片段如下: 通过Pragma HLS UNROLL factor 可以对循环体展开成30 份,这可以大大提高算法执行的并行性,但同时使硬件资源消耗也相应提高。 实际使用时需要综合考虑实时性与资源占有率,对factor 的取值进行折中设置。 2.3.2 计算欧式距离 计算欧式距离的代码片段如下: 通过pragma HLS UNROLL 对内循环进行展开。由于主成分个数M一般较小,内循环可以完全展开,因此在进行循环展开优化时没有指定展开因子factor的值,即默认采取完全展开的方式。 对于外循环,采用pragma HLS PIPELINE 进行流水线优化,这可以显著提高系统的数据吞吐量。 APB 外设有UART、动作发生器( Igni- ter )、计时器(Timer)这3 个模块,它们由APB 总线挂载到系统中,负责实现系统的辅助功能。 2.4.1 UART 本文SOC 系统使用了3 个UART,分别进行系统调试、ECG 数据采集和驱动串口屏显示。 采用心电图信号采集模块ADS1292 采集心电图信号,然后通过蓝牙模块无线发送给SOC。 SOC 采用UART1 连接蓝牙模块,接收ADS1292 模块发送过来的心电图信号。 在身份识别硬件加速器模块对心电图信号进行处理、身份识别之后,将识别的结果通过SOC 上UART2 接口相连的串口屏进行显示,同时在调试时还可以通过SOC 上的UART0 连接到电脑上的串口调试助手中显示识别结果。 2.4.2 动作发生器 动作发生器负责接收来自Cortex-M3 处理器的指令,根据具体的指令,唤醒身份识别硬件加速器或者ECG 采集模块进入工作状态。 动作发生器的物理地址为0x40003000,且与Cortex-M3 处理器、身份识别硬件加速器、ECG 采集模块连接。 当Cortex-M3 处理器往该地址写入0xAE 后,可以唤醒硬件加速器,同时Cortex-M3 处理器进入待机状态,直至硬件加速器工作完毕。 当Cortex-M3 处理器往该地址写入0xCE 后,可以唤醒ECG 采集模块,同时Cortex-M3 处理器进入待机状态,直至ECG 采集模块已经将新的ECG 数据写入BRAM 中。 2.4.3 计时器 为统计系统身份识别所需要耗费的时间,加入了独立于处理器外部的计时器模块。 计时器接入板载100 MHz晶振作为时钟源,计时精度可以达到1 ms。在计时之前,可以通过软件代码将计时器归零,同时启动计时器,并在执行完相应的计算之后读出计时器的计时结果,从而实现对算法执行时间的记录功能。 设计采用Matlab2009a 在登记阶段进行训练,采用版本号为AT421-MN-80001-r0p0-02rel0 的Design-Start Eval 利用Vivado v2021. 1 进行硬件开发,采用MDK v5.23 进行软件开发,最终在廉价的Ego1 开发板(FPGA 型号为XC7A35TCSG324-1)上实现。 所设计的SOC 系统硬件资源利用情况如表1 所示,可以看出消耗了82.32%的查找表资源和18%的触发器资源。其中大部分资源用于创建所设计的SOC 结构,例如AXI-AHB 协议转换器、乘法器等。 其运行性能最高可以达到90 MHz,满足实时性需求。 表1 硬件资源利用情况 5 位年龄在18 ~45 岁的志愿者进行现场测试。先录入ECG 信号,Matlab 端将数据训练好后,带上心电图测量设备开始实物测试,系统完成识别后结果显示在串口屏上,如图3 所示。 经过实验,取欧几里得距离阈值为5,得到的混淆矩阵如图4 所示。 图4 中每个小方格的数值表示识别测试者的次数。 如第1行表示对1 号测试者进行测试,其中有67 次正确检测为1 号测试者,错误检测为2 号、3 号测试者各2 次,检测为4 号测试者0 次,检测为5 号测试者4 次。 由图4可知,这5 位测试者的平均识别正确率可以达到96.8%,识别结果满足要求。 图3 实物测试图 图4 实物测试混淆矩阵 由于每个人的ECG 数据具有独特性和难复制性,使对活体利用ECG 进行身份识别具有很强的安全可靠性。 本设计根据ECG 身份识别场景的需求,利用FPGA 的灵活重构性定制化设计SOC,将负责系统控制的微处理器软核和算法硬件加速器部署到同一个FPGA 上。 通过在FPGA 上搭建片上系统,ECG 身份识别用硬件电路实现,使身份识别更具有灵活性、高效性,可靠性等特点。1.2 算法实现

2 SOC 设计

2.1 软硬件分工

2.2 系统框架设计

2.3 身份识别硬件加速器设计

2.4 APB 外设设计

3 系统测试

3.1 资源利用率与性能

3.2 现场测试

4 结束语