基于ZYNQ 的数字信道化接收机实现

2023-10-28王铎荣张灵玉

张 军, 王铎荣, 张灵玉, 杨 波

(成都信息工程大学电子工程学院,四川 成都 610225)

0 引言

随着军事现代化进程的加快,各种新型电子系统在现代战场上得到广泛应用,导致电子侦察困难,体现在以下几个方面:频率范围宽、信号样式多样、单位时间内接收信息量大。 因此,为满足现代战场对电子侦察接收机的需求,接收机应该具有瞬时带宽大、高灵敏度、高分辨率和多信号同时处理的能力。

目前,数字信道化接收机的主流信号处理架构由ADC+FPGA+DSP 构成,由于现代电磁信号的干扰复杂,FPGA 与DSP 的数据传输受到严重影响。 为提高数据传输能力,减少误码率,将采用Xilinx 公司的集ADC、FPGA 和ARM 为一体的异构芯片——Zynq UltraScale+RFSoC,为数字信道化接收机提供一种新的信号处理架构。 将时分复用技术[1-4]应用于基于多相DFT 的数字信道化结构[5-8]中,并通过后续信号处理模块实现信号检测、脉冲参数测量和DMA(direct memory access)数据传输等功能,为军事信息化技术的进步与发展提供基础性保证。

1 数字信道化基本原理

高速ADC 可为数字接收机提供大的监视带宽,同时也造成ADC 高采样速率与低速数字信号器件处理数据能力不匹配的问题。 可通过配置不同的调谐器、原型滤波器和抽取器的多路DDC 并行信道化结构实现对整个频带的监视,但当子信道数目的快速增加时,原型滤波器导致资源量损耗急剧上升。 为解决数据率不匹配和FPGA 硬件资源消耗过大的问题,提出多路DDC 并行信道化结构的高效实现结构。

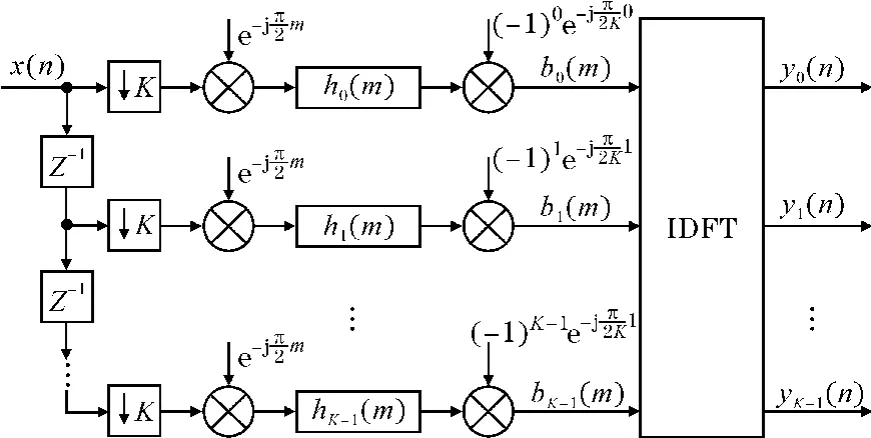

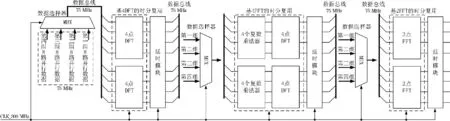

在多路DDC 并行信道化结构中,直接限定数控振荡器的输出频率,其所得一般结构中的原型滤波器对ADC 输出所有数据点进行混频和滤波处理,而子信道输出点数只有ADC 数据点数的1/M,导致数字信道化的一般结构浪费大量的FPGA 资源。 推导得出基于多相DFT 的数字信道化结构,其结构框图如图1 所示。

图1 基于多相DFT 的数字信道化结构

2 基于时分复用的数字信道化接收机的实现

2.1 主要芯片介绍

本设计是基于Xilinx 新一代SOC 芯片Zynq Ultrascale+ RFSoC 实现[14-16],其主要结构由可编程逻辑单元(programmable logic)、4 个Cortex-A53 内核和Cortex-R5 内核所组成的ARM 微处理单元、8 个12 位4.096 GSPS 的ADC 和8 个14 位6.554 GSPS 的DAC组成,该款芯片可为开发者提供一个快速、全面的RF模数信号链原型设计平台。

ZYNQ RFSoC 架构可缩短产品研发时间。 Vivado软件集成了可用于PL 和PS 通信的IP 核,节约了开发时间和人力成本,单芯片解决方案通过内部互联进行通信,省去FPGA 与外部处理器之间的约束。 单芯片内部的互联通信在提高接口带宽的同时,也提高了数据传输的安全稳定性、降低数据传输的误码率。

2.2 数字信道化接收机工作流程

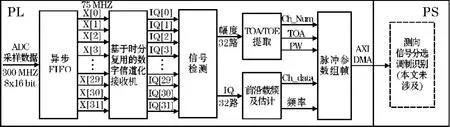

设计的数字信道化接收机的工作流程如图2 所示。 模拟中频信号经采样率为2.4 GHz 的ADC 采样后得到300 MHz 的串行数据,并通过串并转换为并行的数字信号,将并行32 路的数据以及随路时钟传给信道化模块,信道化模块将基带信号传输给信号检测模块、前沿测频和估计模块,分别实现对32 个子道做信号检测和测量信道内脉冲信号前沿的载频。 最终将信道编号、脉冲宽度(PW)、脉冲重复周期(PRI)、信号前沿载频值和128 点基带IQ 组成数据组帧,通过AXI DMA 传输至PS 端等待后续处理。

图2 数字信道化接收机的工作流程图

2.3 基于时分复用的数字信道化接收机应用

为减少硬件乘法器的使用,引入时分复用技术,设计基于时分复用的多相DFT 数字信道化接收机。

2.3.1 基于时分复用的多相滤波器的FPGA 设计与仿真

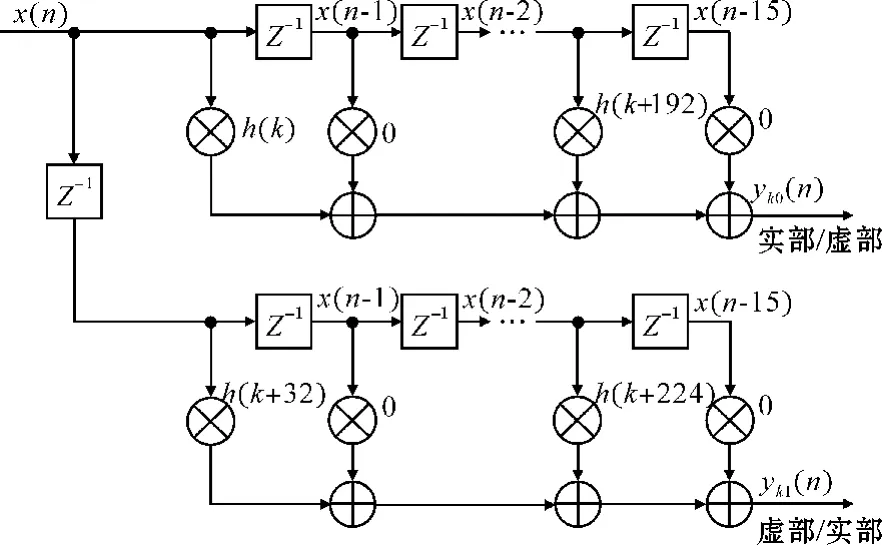

本文研究的雷达信号数字接收机需要较高的相位,故采用通带和阻带50%交叠的线性相位的FIR 型数字滤波器作为多相滤波器组。 将原型滤波器进行32 相分解所得的高效数字信道化结构,其第k路FIR滤波器高效实现结构如图3 所示。

图3 第k 路FIR 滤波器的高效实现结构

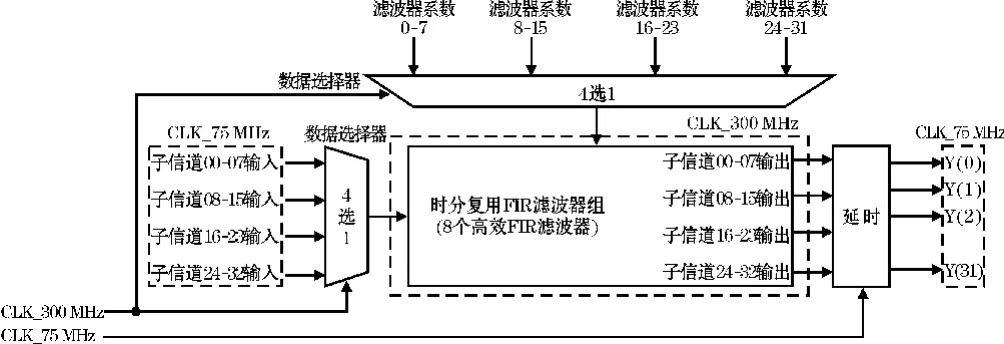

基于时分复用的FIR 多相滤波器组的FPGA 实现的框图如图4 所示。 将两个4 选1 的数据选择器对子信道32 组的数据及抽头系数进行抽取选择,传输给FIR 滤波器组进行处理输出数据,延时模块将数据时序对齐。

图4 基于时分复用的多相滤波器组

2.3.2 基于时分复用的并行FFT 设计

为实现信号快速处理,FFT 模块采用多级流水线设计。 本文采用二维FFT 方法实现基于时分复用的32 点并行FFT,其实现框图如图5 所示。

图5 基于时分复用的32 点并行FFT

文中,基于时分复用的32 点并行FFT,工作于300 MHz,则子信道可进行4 次采样。 对于第二级16点并行FFT,需要2 个基4FFT 完成32 路信号的处理。对于2 点FFT 而言,需要4 个基2FFT 即可完成信号的处理。 因此,基于时分复用的32 点FFT 共耗用30个DSP48E2,节约硬件资源。

2.4 CORDIC 模块

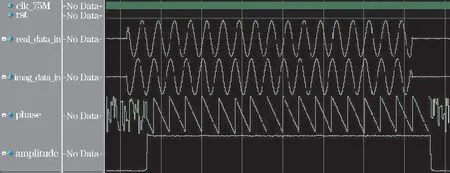

通过对CORDIC 算法[17-18]研究,本文采用Xilinx的CORDIC IP 核来计算信号的瞬时幅度及瞬时相位,配置好IP 核的参数和数据转换格式,并仿真CORDIC IP 输出相位phase 和幅度amplitude,如图6 所示。 由图6 可知,CORDIC IP 输出的相位在多个信号周期内是不连续的,发生了相位模糊,致使测频错误。

图6 CORDIC IP 的仿真图

本文采用相位差分测频法来解决相位模糊问题以及满足系统实时性需求,使用CORDIC 算法对数字信道化结构的输出求瞬时频率,并对瞬时频率做防脉冲平均值滤波,再做均值便可解决相位模糊问题。

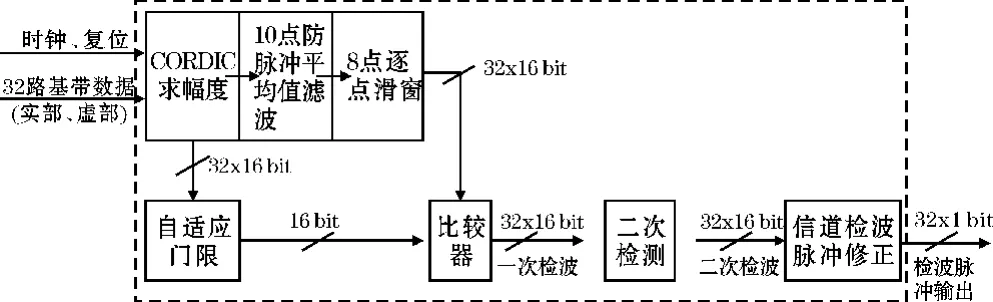

2.5 信号检测模块

鉴于ADC 采集数据时可能产生干扰以及信道化器固有的“兔耳效应”,本文将中值滤波算法和防脉冲干扰平均值滤波算法相结合对雷达信号进行检测,其检测的流程图如图7 所示。 首先,32 组基带数据通过CORDIC 模块得到信号瞬时幅度,并分两路送至防脉冲平均值滤波模块和自适应门限模块得到32 组信号幅度和自适应检测门限。 其次,将所得幅度与门限作比较,若幅度大于门限则输出“1”,否则输出“0”。 此时完成第一次检测。 为降低信号检测的误检概率,需对信号进行二次检测,最后经过检波脉冲修正后得到信号的检波脉冲[19-20]。

图7 雷达信号检测的流程图

2.6 数据组帧传输至PS 端

为避免在不同时间点获得的脉冲参数产生错乱,采用流水缓存设计方法,将抽取的基带信号IQ 分量、PW、PRI 和脉冲前沿频率进行统一编码形成数据帧。在获取到需要的数据帧后,使用Vivado 中的AXI DMA IP 核来实现将数据从PL 端传输至PS 端。 使用AXI Stream 协议DMA 可以直接访问内存,既减少了CPU的资源占用,又提高了传输数据的速度。

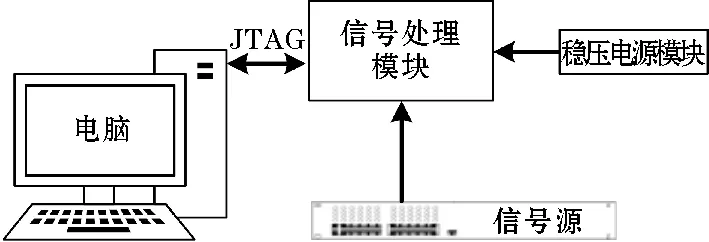

3 数字信道化接收机的软硬件及系统测试

本文数字信道化接收机是基于Xilinx 新一代SOC芯片Zynq Ultrascale+ RFSoC 实现时分复用的数字信道化,数字信道化器资源耗用118 个DSP48E2,使用较少的硬件乘法器。 接收机系统测试的流程如图8 所示。 信号源输出的信号经过线缆输送至中频数字信号处理板的ADC 输入端,然后信号处理板运行算法并通过集成于FPGA 内部的逻辑分析仪ILA 捕获和显示FPGA 的实时信号。

图8 测试流程图

3.1 数字信道化结构输出测试

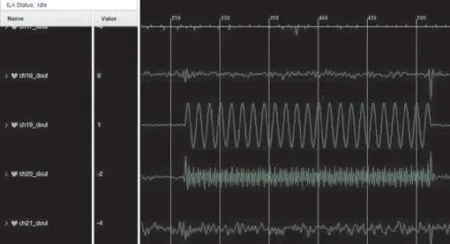

使用信号源模拟频率1666 MHz、脉宽2 μs、脉冲重复周期5 μs、信号功率为-20 dBm的中频信号,对基于时分复用的数字信道化结构进行测试,使用ILA 捕获的输出波形如图9 所示。 由图9 可知,ch19_dout 幅值要大于ch20_dout,表明第20 子信道的信号是由第19子信道外泄所产生的,避免发生混叠现象。 因此,本文的数字信道化器能正确地将时域重叠的信号提取出来,剔除虚假信号解决信道模糊问题。

图9 数字信道化结构的输出

3.2 信号检测模块测试

将数字信道化结构输出的32 路IQ 信号传输至检测模块,可得到ILA 抓取结果如图10 所示。 其中,ch19_ampli_dout 是经防脉冲平均滤波算法产生的平滑信号,auto_thresh 表示信号的自适应检测门限;first_detect 为第一次检波脉冲;ch_dout_valid 表示的数字信道化结构输出检波信号。

图10 数字信道化输出的信号检测

由以上分析可知,防脉冲滤波算法和中值滤波算法能有效地消除信号的随机噪声和脉冲干扰。 对信号进行二次检波可避免由子信道产生的幅度波动,提高雷达信号检测的准确性。

3.3 PW 和PRI 的测试

测试环境:信号源产生信号频率为1340MHz、功率为-20 dBm 的中频模拟信号。 脉冲宽带PW 和脉冲重复周期PRI 的仿真结果如图11 所示。

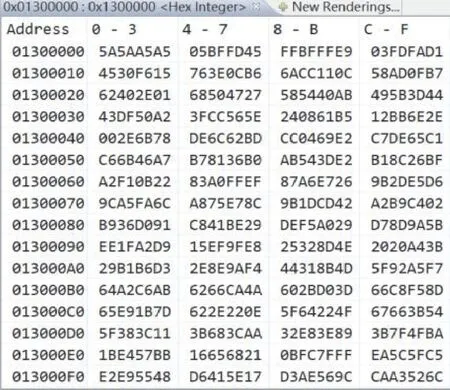

由数字信道化接收机仿真结果可知,当信号PW<1 ms时,其误差<100 ns,PRI 的测量误差<100 ns;当信号1 ms FFT 测频模块对频率为1250 ~2350 MHz、频率步进为100 MHz及功率为-30 dBm的中频模拟信号进行频率测试的结果如表1 所示。 由表1 可知,FFT 测频的最大偏差为4.5 kHz,满足信号载频测量精度≤0.1 MHz的设计指标。 表1 脉冲前沿频率及测频误差 数据传输方面,首先,AXI FIFO 缓存组帧数据并输出。 其次,通过DMA IP 核将数据传输至PS 端的DDR 中,如图12 所示。 由图12 可知,接收缓存区的首地址0x01300000 缓存的正是数据帧的帧头,说明PS 端已正确接收到来自PL 端的数据,验证了软件设计的有效性。 图12 PS 端DDR 中的数据 结合实际工程需求,完成了基于多相DFT 的数字信道化接收机的实现。 采用多路DDC 并行信道化结构对各个模块的参数进行限定,并推导得出基于多相DFT 的数字信道化结构。 同时,将时分复用的技术引入到基于多相DFT 的数字信道化结构,设计并实现了单通道的32 路基于时分复用的数字信道化结构,有效降低了硬件乘法器的耗用量,提高系统的整体工作性能和实效性。 同时,对各个模块进仿真测试以及对整体接收机进行测试的结果表明该结构在FPGA 上实现的可行性以及实用性,达到了项目的预期指标。3.4 测频精度测试

3.5 DMA 数据传输测试

4 结束语