DMA传输在二次雷达译码中的应用

2023-10-28刘娟

刘娟

摘要:针对二次雷达译码数据传输的突发性和实时性要求,研究了直接存储器访问(direct memory access,DMA)传输在二次雷达译码中的应用方法,并通过时序分析,验证了DMA 传输在二次雷达译码时的优势和可行性。应用DMA 传输大大增强了二次雷达系统的数据吞吐能力和处理能力,有效保障了二次雷达系统目标应答信号的实时性。

关键词:二次雷达;译码;DMA;实时

中图分类号:TN919 文献标识码:A

0 引言

二次雷达是空管监视系统的重要组成部分,其在天线发现目标期间,需实时获取目标的身份代码、高度、方位和距离信息。空中目标信号具有随机性和突发性,二次雷达信号处理系统要完整、实时地接收处理这些信号,就要求二次雷达信号和数据处理系统具有较高的数据吞吐能力和处理能力。

二次雷达的信号处理模块接收前端的中频IQ数据(信号正交分解后的两个分量),对数据进行解调、去交织、译码等处理,形成二次雷达原始数据。信号处理模块由现场可编程门阵列(fieldprogrammablegate array,FPGA) 完成; 数据处理模块对信号处理后的原始数据进行关联、凝聚、数据解析等处理,一般由中央处理器(centralprocessing unit,CPU)完成。

为了匹配信号处理模块与数据处理模块间的数据可靠传输,选择总线直接存储器访问(directmemory access,DMA)作为通信方式。DMA 是总线并行方式,具有突发传输能力,读写速度快,稳定性高,总线内存直接访问,不占用CPU 有效工作时间,能够大大提高系统的实时性和吞吐能力。

1 DMA传输原理

外设与存储器之间以及存储器与存储器之间的数据传输,通常采用程序中断方式、程序查询方式和DMA 控制方式。程序中断方式和程序查询方式都需要CPU发出输入/ 输出(In/Out,I/O)的指令,然后等待I/O 设备完成操作之后返回,期间CPU 需要等待I/O 设备完成操作。

DMA 在传输存储器和I/O 设备的数据时,无须CPU 来控制数据的传输,直接通过DMA 控制器(direct memory access controller,DMAC)完成外设与存储器之间以及存储器与存储器之间的数据高速传输。

一个完整的DMA 传输包括DMA 请求、DMA响应、DMA 传输和DMA 结束4 个步骤。

DMA 传输原理如图1 所示,图中I/O 设备为源端设备,由I/O 设备向目的端设备(存储器)传输数据,其DMA 的基本传输过程如下:① CPU 对总线控制器进行初始化,制定工作内存空间,读取DMAC 中的寄存器信息,了解DMAC 的传输状态[1];② I/O 设备向DMAC 发送DMA 请求(DMArequest,DREQ),DMAC 收到此信号后, 向CPU发出总线保持信号(HOLD); ③ CPU 当前总线周期执行结束后发出总线响应信号保持确认(holdacknowledgment,HLDA); ④ DMAC 收到总线授权后,向I/O 设备发送DMA 响应信号DMA 确认(DMA acknowledgment,DACK),表示允许I/O 设备进行DMA 传送;⑤开始传输时,DMAC 首先从源地址读取数据并存入内部缓存中,再写入目的地址,完成总线数据从源地址到目的地址的传输[1];⑥ DMA 传输完成后,DMAC 向CPU 发出结束信号,释放总线,使CPU 重新获得总线控制权。

一次DMA 传输只需要执行一个DMA 周期,相当于一个总线读/ 写周期,因而能够满足外设数据高速传输的需要。

2 DMA在二次雷达中的应用

2.1 FPGA 和PowerPC 协同架构

系统架构直接决定系统的性能、特点、处理能力和调试难易度等[2]。传统的二次雷达译码器大多采用分立元件和中小规模集成电路的方式设计[3],其数据处理能力有限,无法完成大数据量的应答处理。

本文的二次雷达系统采用FPGA 和嵌入式处理器(PowerPC)协同架构。FPGA 易于处理大数据量的流水数据,同时PowerPC 处理器具有强大的运算能力,寻址灵活,处理速度快,能实时处理高密度、大容量的应答信号。FPGA 主要用于原始应答信号的延時对齐、量化反窄、框架检测、旁瓣抑制、代码提取等信号处理,形成原始目标应答报文[2]。PowerPC 主要用于点迹凝聚、航迹处理、假目标处理等的复杂运算和实时处理。同时FPGA 和PowerPC 通过一种高速串行计算机扩展总线标准(PCI express,PCIe)进行总线互联,采用DMA 的数据传输方式。PCIe 使用点到点的差分信号传输方式,可有效避免数据传输过程中的串扰问题[4],保证二次雷达译码电路高速、稳定运行。

2.2 DMA 报文传输原理

如图2 所示,FPGA 采集到总线上的数据后,送入译码单元完成目标译码,按照FPGA 与PowerPC 处理器之间的通信协议,将处理后的译码数据组包后放在先进先出数据缓存器(first in firstout,FIFO)中,根据DMA 上报的秩序,依次将数据上报至上位机PowerPC [5],形成目标原始应答报文DMA 数据帧。PowerPC 根据译码单元上报的DMA 报文,剔除非法的数据,将一个目标的多次应答整合成一组目标数据,并将各模式应答信息装填到点迹数据帧中上报终端处理。

二次雷达FPGA 和PowerPC 的DMA 数据传输的协议包括以下5 点:① PowerPC 通过片上通用I/O 读取FPGA 提供的目标应答数据;② PowerPC利用D0 ~ D15 数据总线,以16 位数据宽度读取数据;③ FPGA 向PowerPC 发送中断请求信号,通知PowerPC 读取所有的应答数据;④ PowerPC访问FPGA 的FIFO 地址;⑤ PowerPC 读取数据生成目标报文后输出到规定的端口。

2.3 DMA 报文传输流程

二次雷达系统中,PowerPC 包括以下信号:① 16 位数据总线D0 ~ D15 (LSB,最低有效位为D0),I/O; ② 总线读信号IOR#(# 代表负逻辑),低电平有效(PowerPC 输出);③总线写信号IOWD#,低电平有效(PowerPC 输出);④地址允许信号AEN(PowerPC 输出):AEN=0 时为CPU地址,AEN=1 时为DMA 地址。

DMA 通信包括以下控制信号:①外部DMA 请求DREQ,高电平有效(PowerPC 输入);② DMA响应回答DACK#,低电平有效(PowerPC 输出)。

二次雷达的译码数据传输时,根据约束条件将DMA 大小设置为固定值,以便CPU 通过查找同步头解析数据形成雷达数据帧。FPGA 首先向PowerPC 的DMA 发送DREQ 信号,当DMA 收到DREQ信号后,向CPU发出总线请求信号(HRQ),CPU 收到HRQ 信号后,释放总线控制权。DMAC获得总线控制权后,向FPGA 发送DACK 响应回答,通知FPGA 可以进行DMA 传输。PowerPC 发送总线读信号IOR(input/output register,输入/ 输出寄存器),把译码数据从FPGA 写入内部存储器。当16 位数据传输完成后,DMAC 释放总线控制权,CPU 重新接管总线控制权,至此DMA 传输完成。

3 DMA传输时序分析

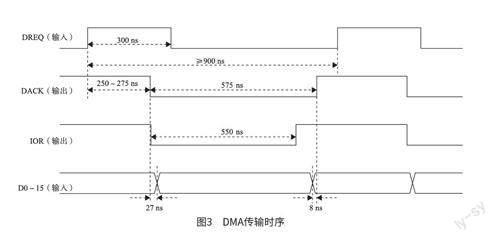

一个DMA 传输只需要执行一个DMA 周期。本文以二次雷达系统中使用的典型PowerPC 为例进行DMA 数据传输的时序分析。

如图3 所示,PowerPC 完成一次DMA 传输需要900 ns,也就是说传输16 位数据需要900 ns。

以最常用的串口通信数据传输方式为例,完成一次传输包括固定起始位1 位、数据位8 位、无校验位、停止位1 位,用串口通信最大波特率115200 b/s 计算,因此,传输16 位数据需要的时间为173 600 ns。

European Mode S Station Functional Specification(欧洲关于S 模式的一个标准)中规定二次雷达系统在询问天线10 r/min 的转速下,0.5 海里到256海里范围内,3.5°扇区目标容量峰值为54 批[6]。

通常应答信号数目的需求至少为6 个,才可以获得较好的真实目标并确认应答数据的准确性,所以在扇区内收到的原始应答信号数量至少为324 个,由于二次雷达目标应答信息报文基本长度至少为11个字(本文1 个字为16 位),可知此时需传输的数据长度为3 564 个字。

天线转速为10 r/min,故天线旋转3.5°扇区的时间为0.058 3 s(需要在此时间内传输3 564 个字),则1 个字的传输时间为16 358 ns,而用DMA 方式传输时1 个字只需要900 ns,因此DMA 传输可以有效保证应答目标原始报文的高速和实时传输。若使用串口通信传输1 个字需要173 600 ns,远超获得有效目标的时间要求,所以串口通信并不满足大容量目标原始报文的有效传输需求。

4 结论

本文研究了DMA 传输设计在二次雷达译码中的应用,在信号处理与数据处理模块,采用DMA传输方式进行数据交互,电路简洁,可适应数据突发传输,不消耗CPU 有效工作时间,适合作为嵌入式处理系统内模块间的数据高速传输,在复杂空域环境中有效提高了二次雷达系统探测目标的实时性和可靠性。

参考文献

[1] 高阳. 基于SoC 芯片的高性能DMA 控制器的设计与实现[D]. 哈爾滨:黑龙江科技大学,2022.

[2] 邾琳琳,丁岐鹃,张卿. 二次雷达应答代码的提取及解析[J]. 科技信息,2011(10):787-788.

[3] 蒋睿. 基于DSP 的二次雷达应答解码器软件设计[D].成都:电子科技大学,2004.

[4] 沈洋,李纪三,夏东方,等. 多功能相控阵雷达多通道DMA 传输系统设计[J]. 舰船电子工程,2022,42(9):82-86.

[5] 杨小飞. 基于FPGA 和DSP 技术的二次雷达应答处理器[D]. 成都:电子科技大学,2004.

[6] European Organization for the Safety of Air Navigation. European Mode S Station Functional Specification: SUR/MODES/EMS/SPE-01 [S/OL]. [2023-05-20]. https://www.eurocontrol.int/sites/default/files/2019-04/surveillancem o d e - s - e u r o p e a n - m o d e - s - f u n c t i o n a l -specification-20050509.pdf.