一种带动态环路增益控制器的全数字锁相环

2023-10-25蒋小军刘小勇龚江涛刘运松

蒋小军,刘小勇,龚江涛,刘运松

(湖南铁道职业技术学院,湖南 株洲 412001)

0 引言

锁相环(PLL)是无线收发器、高速模数转换器(ADC)和片上系统(SOC)等电路的关键部件。锁定时间是全数字锁相环的关键参数之一,在理想情况下,锁定时间应尽可能小。锁相环采用调频字估算和预置技术[1-3],调节DCO频率控制字,使之接近目标频率,从而减少锁定时间。但锁相环输出频率范围小,滤波器带宽窄,精度不高,抖动大,稳定差。基于TDC-PFD的全数字锁相环,便于快速捕获频率,但是增加了功耗和面积。

针对上述全数字锁相环存在的问题,本文提出了一种基于比例积分(PI)控制器和动态环路增益控制器(DLGC)的全数字锁相环,可以减少锁相环锁定时间。采用EDA软件对整个系统进行设计和仿真,给出了计算机的仿真结果。

1 全数字锁相环的方案设计

全数字锁相环的系统结构如图1—2所示。该锁相环主要由数字鉴相器(DPFD)、自适应模式选择电路(AMSC)、动态环路增益控制器(DLGC)、PI控制的数字环路滤波器(DLF)、累加型数控振荡器(DCO)和分频器(DIV)等电路组成[4-5]。

图1 全数字锁相环系统结构

图2 DLGC和DLF电路结构

数字鉴相器(DPFD)由双D触发器和与非门构成,具有频率检测和相位检测作用。自适应模式选择电路(AMSC)主要由时间数字转换器(TDC)和相位误差检测模块组成,如图1所示,用于锁定过程中选择锁定模式,并产生选择快速锁定模式或者PI锁定模式的控制信号M。当参考(输入)信号与分频(输出)信号之间的相位误差QE大于标志相位误差QS时,M=1;反之,M=0。

2 电路设计和仿真分析

2.1 数字鉴相器的设计

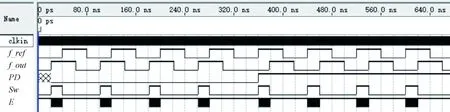

数字鉴相器(DPFD)的电路,如图3所示,由可复位的D触发器(DFF)和与非门(NAND)等组成[5]。其作用是比较输入与输出信号的触发沿,并产生超前或滞后的极性信号(PD)、相位误差(Sw)和频率或相位误差序列(E)。仿真波形如图4所示,当输入参考信号f_ref滞后反馈信号f_out时,则PD=0;当输入参考信号f_ref超前反馈信号f_out时,PD=1。

图3 数字鉴相器电路

图4 数字鉴相器电路仿真波形

2.2 动态环路增益控制器的设计

动态环路增益控制器(DLGC)的工作流程,如图5所示。当M=1,表示相位误差大于标志相位误差,此时环路选择快速锁定的工作模式。在该模式中,动态环路增益控制器(DLGC)开始工作,和数字环路滤波器一起调节整个锁相环的环路增益。动态环路增益控制器的参数和增益的计算过程如下:

y1=y1±1

(1)

y2=ym,y2+y1>ym

(2)

y2=y2+y1,-ym≤y2+y1≤ym

(3)

y2=-ym,y2+y1<-ym

(4)

G=y2

(5)

公式(1)“±”符号表示相位增减方向,取决于超前或滞后信号PD极性。y1、y2是有正负之分的符号数,可以大于0,也可以小于0。ym是y2的最大值,与数字环路滤波器的频率控制字的字节有关,而且PD是一个连续的高电平“1”或低电平“0”。如果M=1,锁相环的整体环路增益将累积到一个较大的值,以加快锁定过程。

当M=0时,表示相位误差QE小于锁定相位误差QS,环路切换到正常的PI锁定模式。在这种模式下,动态环路增益控制器停止工作,DLGC中的积分器复位,即y1=0,y2=0,并通过M旁路掉(见图2),有效降低了电路功耗。如果相位误差PD=1,则G=1;如果PD=0,则G=-1。此时该锁相环就是一个传统的比例积分控制锁相环。

根据动态环路增益控制器(DLGC)的工作流程,本文采用VHDL编程完成该模块的设计。

2.3 数字环路滤波器的设计

通过分析计算,可以推导出数字环路滤波器(DLF)的比例积分参数计算公式如下:

P=BG

(6)

I=I±AG

(7)

本文对比例积分控制的数字环路滤波器的结构进行改进,如图6所示。采用流水线的乘法累加器设计的数字环路滤波器,比例积分参数A、B和DLGC输出的增益G只需要7位,经乘法器处理后就可以得到14位的频率控制码FCW,提高了锁相环的运行速度并节省了资源。

图6 DLF的电路

2.4 整体电路设计

依据图1锁相环系统的结构,本文利用Altera公司的QuartusⅡ软件,对整个锁相环系统做综合设计和仿真,锁相环的仿真电路如图7所示。

图7 锁相环的仿真电路

在输入参考信号都为1.25 kHz的情况下,基于PI控制和DLGC的全数字锁相环大概经过5.19 ms快速锁定频率,如图8所示。当M=1,锁相环处在快速锁定区。若PD=0,环路增益G减少;反之,环路增益G增加。当M=0,锁相环换处在PI控制区。若PD=0,环路增益G=1;反之,增加环路增益G=-1。与基于PI控制的锁相环换相比,本文设计的锁相环锁定速度快,但抖动较大,不够稳定。

图8 基于PI控制和DLGC的全数字锁相环的时序

3 结语

为了提高锁相环的锁定速度,本文提出了一种基于比例积分(PI)控制器和动态环路增益控制器(DLGC)的全数字锁相环。锁相环中的动态环路增益控制器可以动态调整数字环路滤波器的增益,减少锁定时间。仿真结果表明,与传统的PI控制的全数字锁相环相比,该锁相环具有电路结构简单灵活、锁定速度快、低功耗、低面积和易于集成的特点。