面向FPGA知识产权保护的低开销按次付费授权方案

2023-10-21宋斌威王耀

宋斌威,王耀

面向FPGA知识产权保护的低开销按次付费授权方案

宋斌威,王耀*

(郑州大学 电气与信息工程学院,郑州 450001)( ∗ 通信作者电子邮箱 ieyaowang@zzu.edu.cn)

知识产权(IP)核按使用次数授权付费可以使系统设计者根据实际情况以较低的价格购买IP,已成为一种主要的IP授权方式。针对IP核按次付费的应用需求,提出一种应用于现场可编程门阵列(FPGA) IP的基于可重构有限状态机(RFSM)和物理不可克隆函数(PUF)的新型按次付费IP授权方案RFSM-PUF。针对在实际应用中不同厂家的IP保护方案协议无法通用的问题,提出一种适配所提方案的IP保护认证协议确保IP认证的保密性与灵活性。首先,在IP的原始有限状态机(OFSM)中嵌入一个RFSM,使得只有IP核设计者能够正确解锁IP;其次,将激励输入PUF电路中产生响应;最后,将license和PUF响应组成的密钥共同输入RFSM中来解锁IP。安全性分析结果表明,所提方案满足各项安全指标。在LGSyth91基准电路上的测试实验结果表明,在满足各项安全条件的前提下,所提方案在每个IP核中相较于基于PUF的按次付费授权方案平均查找表(LUT)数减少了1 377,显著降低了硬件开销。

现场可编程门阵列;知识产权;可重构有限状态机;物理不可克隆函数;LGSyth91基准

0 引言

现场可编程门阵列(Field Programmable Gate Array, FPGA)依据自身的可重构性、设计周期短、低成本等优点逐渐成为数字系统设计的主流平台,在控制、通信、医疗等方面的作用显著。可复用知识产权(Intellectual Property, IP)模块的出现显著缩短了产品的设计周期,降低了设计成本[1]。IP核的使用频率也随着FPGA系统设计规模的增加而上升,但是目前的IP核的保护授权方案仍不够完善,无法精准控制IP核的授权使用[2],用户在使用IP核时通常需要用户支付大量的使用费。一些不法分子为了在不支付使用费的情况下使用IP核,采取非法手段,如克隆攻击、反向工程、过度制造、机器学习等[3],破解IP核。IP核的破解与滥用侵犯了IP设计者的合法权益,甚至给数字系统带来较大的安全隐患。因此,设计一个更加灵活安全的IP保护方案是亟待解决的问题。

国内外研究人员在IP核保护方面提出了多种保护技术[4-11]。根据保护的机制,这些保护技术可以分为主动保护和被动保护。主动保护是主动限制IP核的使用,在用户使用IP核之前通过让用户输入正确密钥的方式达到保护IP核的目的。主动保护主要是通过在IP核中加入加密算法或者计量模块实现[12],是目前比较受欢迎的保护形式。被动保护原理是IP设计者通过检测可疑用户使用的IP核中是否存在数字水印,从而判断该IP核是否正常授权[13]。被动保护最明显的劣势是它的保护只能通过人为检测可疑IP的方式进行,保护即时性差,效率低。虽然两种方式的保护方案都能达到保护IP的目的,但是并不完善,存在以下3个方面的缺点:

1)目前基于加密算法的FPGA IP保护方案依赖于永久密钥存储和管理,引入了安全漏洞(如物理攻击[14])和大量的资源开销。

2)基于物理不可克隆函数(Physical Unclonable Function, PUF)的按设备付费的IP授权方案可以解决密钥存储带来的安全漏洞,但是按设备付费方案不能满足所有用户的需求,尤其是无法负担永久许可费的用户。

3)现有的按次付费的IP许可方案虽然更灵活,但是需要将PUF和可靠性增强模块嵌入每个IP核,无法在安全性和开销之间取得平衡。

针对以上不足,本文提出一种基于可重构有限状态机(Reconfigurable Finite State Machine, RFSM)[4]和PUF的低开销的按次付费的IP核保护方案RFSM-PUF,使用PUF为FPGA设备上的IP核提供部分密钥序列,并将RFSM嵌入原始IP核中作为IP核的锁,状态机的正确路径由PUF响应和IP设计者密钥两部分决定。当输入的密钥与RFSM的预定路径输入不一致时,用户不能通过RFSM成功进入IP核的原始有限状态机(Original Finite State Machine, OFSM)中,只有用户输入正确的license时,状态机才能正常运行并解锁IP,实现IP核的功能,同时RFSM中的状态序列在下次使用之前实现重组形成一个新的锁。

本文的主要工作如下:

1)设计一种低开销的按次付费的IP核保护方案,使用PUF锁定特定的FPGA设备,并使用RFSM取代嵌入IP中的PUF模块实现按次付费功能。

2)调整传统的三方交互协议,使之与所提授权方案契合,保证IP在三方交互过程中的安全性与灵活性。

3)在LGSyth91基准电路上进行开销与时序测试,与现有的按次付费方案对比分析,实验结果验证了所提方案具有更低的资源开销。

1 相关工作

针对IP核滥用的问题,目前用于IP核检测的安全方案大多采用被动检测技术,不能快速、有效地保护IP核。Torunoglu等[5]提出了一种基于序列函数作用于有限输入输出集的水印方案和一种水印检测算法,数字水印作为输入输出序列隐藏在IP核中。当IP设计者怀疑自己的IP核在未经许可的情况下被滥用,可通过检查IP核中嵌入的数字水印维护自己的权益,但是这种静态数字水印方案无法有效抵抗攻击者的攻击。Cui等[13]提出了一种动态数字水印方案,通过修改IP核中的有限状态机(Finite State Machine, FSM),将水印嵌入IP核的输出部分,提高了数字水印方案的安全性;但是攻击者可能尝试追踪并删除水印,导致这种方法非常耗时。当前数字水印方案的弊端是它们只能在IP核被非法使用之后保护,在即时性方面仍没有实质性改进。因此,水印技术不能有效地保护IP核的非法使用。

主动保护技术可以在用户非法使用IP核之前控制IP的使用,从而达到更快保护IP核的目的。然而,主动检测技术本身也存在各种安全隐患。Maes等[15]提出一种基于有源计量的授权方案,通过在IP核中加入一个计量模块,解锁时需要计量密钥解锁IP,从而实现IP核的追踪与控制[12]。系统设计者在使用IP核之前,需要将计量模块和计量密钥配置到FPGA设备上的可配置逻辑块(Reconfigurable Logic Block, CLB);其次解密模块解密计量密钥,并生成最终的IP密钥;最后,解密模块使用解出的IP密钥对IP核设计解密,配置器将它配置到FPGA的CLB中,密钥、计量模块比特流和IP核比特流一起存储在片外非易失性存储器(Non-Volatile Memory, NVM)中。由于存储在NVM中的license是不变的,所以该方案容易被侧信道攻击破解,而且容易遭受克隆攻击[16]。

Kumar等[17]以蝶形PUF为例提出PUF可以应用于IP保护,为IP保护提供了一种新思路,然而用于IP保护的PUF响应在可靠性方面有严格的要求。近年来,随着PUF电路的不断优化,它的可靠性和稳定性也越来越高,但是仍然无法达到直接应用于IP中的标准。潘畲稣等[18]指出PUF响应的不稳定性导致它无法直接应用于IP保护或密钥生成。模糊提取器的出现使PUF的可靠性可以提高至99.9%以上[19],缓解了PUF在IP保护方面的可靠性欠缺问题;但是使用模糊提取器在增强PUF响应的同时,也会带来巨大的资源开销。

Zhang等[20]提出一种应用于FPGA IP的PUF-FSM绑定方案,这是一种将片上PUF和FSM保护结合起来的按设备付费授权方案。系统设计者将存储在NVM中的激励输入片上PUF中以产生唯一的PUF响应,响应经过可靠性增强模块处理之后被当作license的一部分输入FSM中,最后由FPGA配置器完成IP核的解锁和配置。该方案存在一定的局限性,如果系统设计者只使用一次IP核设计系统,但却需要花费大笔费用购买片上所有IP核的永久license。因此,这种按设备付费方案局限于永久使用IP的大型设计,不能满足小型设计用户的需求。

Sun等[21]提出了一种新的按次付费方案,将一个PUF嵌入IP核内部作为安全模块。IP设计者通过从FSM中抽取PUF的响应计算license。IP核在综合时,它内部PUF的位置会随机改变,导致PUF的激励‒响应对(Challenge Response Pair, CRP)发生不可预测的变化,最终使原本的license失效。只有当IP设计者根据PUF响应重新计算license并发送给系统设计人员之后,IP核才能正常使用。相较于按设备付费方案,该方案虽然在灵活性方面更优越,但是IP核的正常工作取决于PUF响应是否可靠,为了获得高可靠性的响应,每个嵌入IP中的PUF块都需要一个模糊提取器优化响应[19,22]。从Sun等[21]的实验结果与最近的模糊提取器资源报告可以明显看出,该方案没有考虑模糊提取器。因此,该方案在可实现性以及开销方面存在较大的弊端。

综上所述,现有的IP授权方案在可实现性和资源开销方面面临巨大的挑战,为了解决这一问题,本文结合RFSM和PUF提出一种低开销RFSM-PUF按次付费授权方案。

2 本文方案

首先,使用PUF生成的响应作为FPGA的唯一序列号,用于完成设备认证;其次,在每个IP模块中引入一个RFSM,作为实现按次付费的功能模块,只有IP设计者授权的FPGA设备才能保护IP;最后,用户获得正确的PUF响应并将它与license共同输入RFSM时,RFSM控制锁定和解锁的正确跳转路径,IP核执行与原始IP相同的功能。RFSM的状态序列在IP运行之后会重新编码形成一个新的保护电路。RFSM-PUF授权方案从以下两个方面保护IP:

1)如果片上PUF不能输出正确的响应,那么IP设计者无法计算license并输入RFSM中,用户最终不能使用该设备上的任何IP。

2)解锁并综合IP核后,由于RFSM模块的状态比特流的更新会导致license失效,从而控制IP核的使用次数。

2.1 协议描述

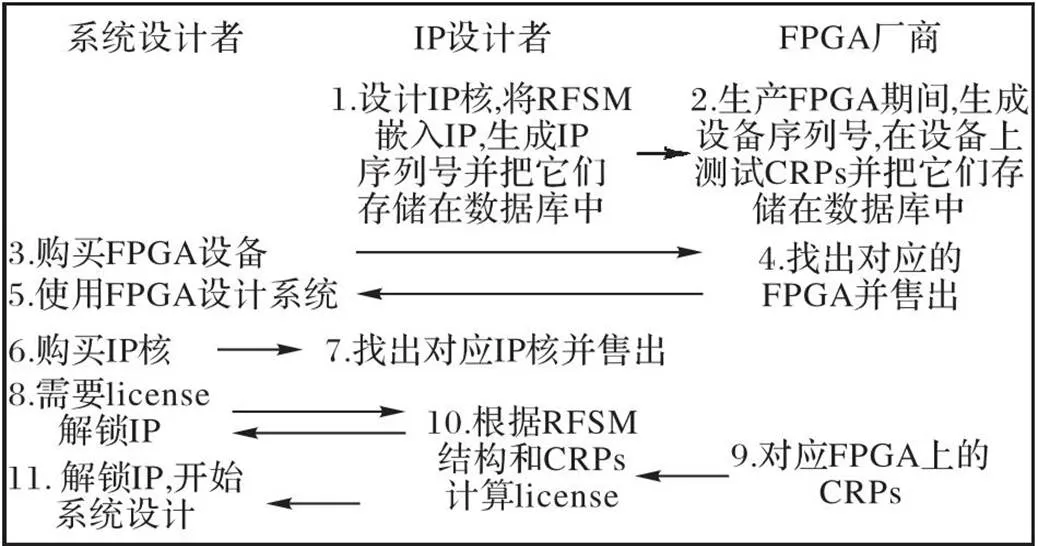

基于RFSM-PUF授权协议由FPGA厂商、IP设计者和系统设计者这3个独立对象交互,具体交互流程如图1所示。

图1 IP保护协议流程

1)FPGA厂商。每个生产出来的FPGA都会携带一个唯一的设备序列号。FPGA厂商在FPGA设备上测试片上PUF电路,并将生成的CRPs存储在数据库中。PUF的激励是公开的,而PUF响应是保密且不可预测的,仅有FPGA供应商知道真实的响应。FPGA供应商使用设备序列号出售FPGA设备,当IP设计者需要根据CRPs计算对应FPGA上IP核的license时,FPGA供应商从数据库中找出对应设备的CRPs并发送给IP设计者。

2)IP设计者。IP设计者根据设计需要设计具有特定功能的IP核模块,并将具有锁定功能的RFSM嵌入IP核中。每个设计完成的IP核都会生成一个的IP序列号,当系统设计者需要某一IP时,将IP核的序列号提供给IP设计者。IP设计者根据IP核序列号找到相应的IP核,同时将锁定的IP核位流发给系统设计人员。若需要解锁IP核,则需要将FPGA序列号发送到IP设计者,IP设计者根据FPGA序列号向FPGA厂商索要CRPs。IP设计者根据RFSM的正确跳转路径和CRPs计算出license,并发送给系统设计者。

3)系统设计者。首先,系统设计者使用FPGA设计数字系统前,需要根据FPGA序列号向FPGA供应商购买设备。其次,系统设计者若想使用IP核进行电路设计,需要根据IP序列号向IP设计者购买IP。未解锁的IP核需要系统设计者向IP设计者提供特定的IP和FPGA的序列号并购买该IP核的license实现正常功能。再次,IP核设计者根据FPGA供应商提供的CRPs以及RFSM结构计算出license,并将它出售给系统设计者。最后,系统设计者在购买的设备上使用IP核进行系统设计。注意,license只能供系统设计者使用一次。当系统设计者需要再次使用该IP核时,需要再次向IP设计者购买license,而IP设计者只需要根据RFSM结构重新计算license完成更新。

2.2 保护机制

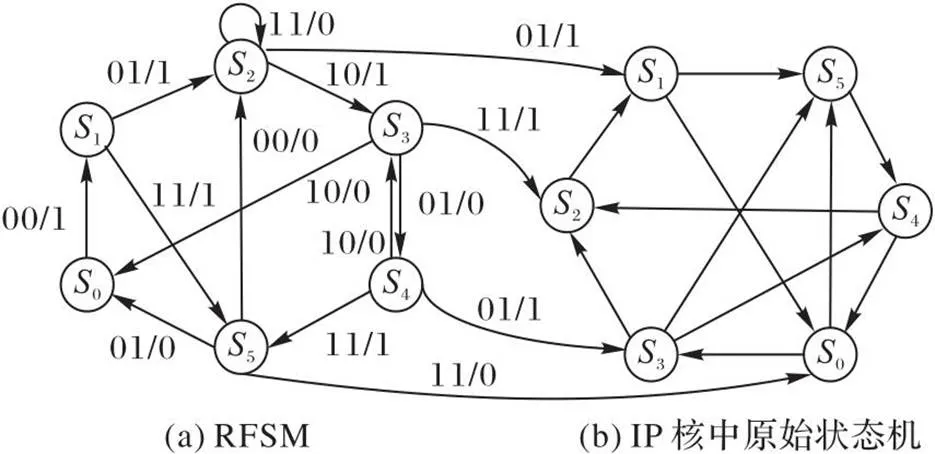

保护机制的原理是PUF响应与IP设计者提供的license共同组成解锁IP核的密钥。其中,PUF响应由弱PUF提供,以授权FPGA设备,PUF响应与IP设计者提供的license必须共同作用才能保证IP核的正确解锁。在每个IP核内部嵌入一个RFSM,以实现按次付费功能。RFSM包括一个状态寄存器、一个转换寄存器和一个重配置器[23]。状态寄存器负责存储RFSM的状态信息,转换寄存器存储状态路径转换的信息,重配置器负责更新RFSM的状态比特流,状态和转换寄存器的更新由重配置器控制。首次在FPGA上综合IP时,系统设计者只有在RFSM中导入正确的密钥,RFSM根据密钥的指示通过正确的转换路径跳转到原始IP中,进而使IP从正确的复位状态运行,否则IP核不能正常使用。RFSM能否正确进入原始IP中是由PUF响应和license共同决定,因此输入RFSM中的PUF响应必须是完全可靠的,才能保证IP核的正常解锁。RFSM-PUF保护机制如图2所示。

图2 RFSM-PUF保护机制

目前,通过附加技术提高PUF响应可靠性需要依靠模糊提取器完成。因此,从IP核的安全性出发,RFSM-PUF考虑了模糊提取器的影响。为了混淆RFSM与原始IP核之间的转换路径,本文从RFSM中随机挑选4个状态,并在将它在原有转换的基础上与原始IP核内部状态连接,这些混淆转换不影响原始IP核的任何性能。IP核综合之后,RFSM的状态寄存器被重配置器更新,从而使RFSM状态跳转信息发生改变(如图3所示),并在下次综合之前配置到FPGA中。

2.3 锁定与解锁

图4为RFSM与IP核绑定示意图。本文以=6、=2、=1、(,S,S+1,)为例,其中、、、分别表示为状态、转换、输入和输出。状态机的初始状态为0,下一个状态是1;整个转换表示为(01,0,1,1)。RFSM与原始IP之间的混淆路径如图4中的2RFSM→1OFSM、3RFSM→2OFSM和4RFSM→3OFSM,这些路径的实现方式与其他转换路径没有区别,这些转换作为RFSM众多转换之一,带来的开销可以忽略不计,具体开销详见第4章。在整个安全电路中,只有一条正确路径能够使RFSM成功进入原始IP的正确复位状态,如图4中0RFSM→1RFSM→2RFSM→3RFSM→4RFSM→5RFSM→0OFSM。因此,IP核被售出后处于待激活状态。

图4 RFSM与IP中的OFSM连接

给出RFSM2状态的转换在dk16基准电路上的具体实现。当RFSM的状态为2=s10000000时,通过判断该状态下的输入序列in,确定下一个状态和当前输出:

1) s10000000:casex(in)

2) 2'b00:beginnextstate=s10000000;out=3'b001;end

3) 2'b01:beginnextstate=s00010000;out=3'b010;end

4) 2'b10:beginnextstate=s01000000;out=3'b001;end

5) 2'b11:beginnextstate=s00001000;out=3'b010;end

6) endcase

解锁时,IP设计者向FPGA生产商索要FPGA上相应PUF的相应,接着IP设计者根据PUF响应与IP核中的RFSM结构计算license。系统设计者将购买的IP核的license输入RFSM中解锁IP核,并可以在该FPGA器件上运行一次,随后RFSM的转换和状态编码被重配置器修改并存储到NVM中,因此IP核综合之后会生成一个新的RFSM,重新锁定IP核。系统设计者如果想要再次综合IP核,先前的密钥将不能解锁更新之后的IP核,需要向IP设计者重新购买新的license。此时新的license由IP设计者根据RFSM结构重新计算得到。密钥的具体组成和密钥如何控制RFSM解锁的过程详见2.4节。

2.4 密钥设计

基于RFSM跳转路径和片上PUF响应,IP设计者设计相应的license。输入RFSM中的密钥包括PUF响应和IP设计者计算的license。密钥通过解锁更新前的RFSM的正确跳转路径,进入原始IP核。IP核运行后,RFSM结构发生改变,若需要再次使用,需要IP设计者根据RFSM更新机制重新计算license。

整个RFSM转换中的完整密钥记为,由RFSM所有的子密钥组成。引导一条RFSM的正确跳转路径,表示为:

RFSM与原始IP核中的状态机具有相同的输入位宽,RFSM需运行步才能进入到原始IP中。和决定了的长度,且可根据实际应用情况自由调节。因此,的总长度为:

其中:表示RFSM路径中第次跳转;key表示第步的子密钥;和分别表示PUF响应和license。

同理,完整密钥中需要的IP设计者需要计算的license总长度为:

3 安全性分析

针对RFSM-PUF授权方案可能存在的安全性问题,分析以下潜在的威胁:

1)暴力攻击。尝试暴力攻击的攻击者们会使用遍历方式猜测密钥中所有的组合情况,直到找出正确的密钥。但是密钥的组合数与它的长度呈指数级递增关系,即长度为的密钥序列的组合数是2,因此暴力攻击几乎是不可能实现的。

2)FSM反向工程。攻击者通过使用FSM反向工程技术从IP比特流中获取FSM的状态转换图[24]。RFSM的状态转换和更新与IP中的OFSM存在交织。攻击者不清楚完整的配置与更新原理,最多从单个状态的转换中解释模糊逻辑,因此不能直接从相互交织的部分中分离出原始IP;同时,RFSM的转换由PUF响应与IP设计者控制,保证了RFSM的安全性。

3)PUF建模攻击。攻击者通过收集整理PUF的CRPs,并使用专业的建模工具使之函数化,最终建立一个与实际PUF具有相同映射关系的PUF。目前的建模攻击技术大多应用于强PUF电路[25],这需要大量的CRPs构建PUF的模型关系。但是依靠当前的技术,强PUF尚不能应用到IP保护中,而弱PUF的CRPs较少[26],无法对弱PUF实施建模攻击。

4)反向工程。攻击者可能使用反向工程技术导致IP核的加密机制暴露[14],并尝试克隆IP核。由于密钥另一个组成部分是PUF响应,而PUF具有抗反向的物理特性,克隆出的PUF与原始PUF拥有截然不同的CRPs。PUF通过提取制造过程中随机的工艺误差(如温度、噪声等)使它具有唯一性,即使同一家制造商也无法制造完全相同的PUF,因此攻击者无法通过反向工程设计相同的PUF。

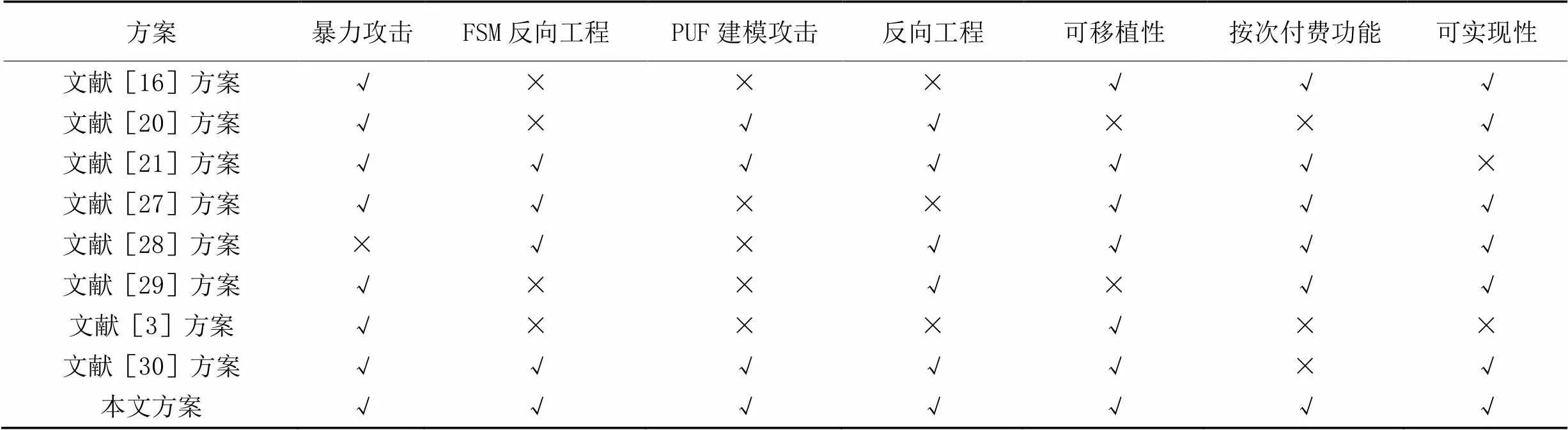

表1展示了RFSM-PUF授权方案与其他授权方案在7个方面的对比结果。

由表1可知,大多数对比方案在系统级架构上保护IP核或者使用安全算法,但这些方案都无法抵抗反向工程,也会引入大量的资源开销,不适用于资源受限的数字系统。Sun等[21]将PUF引入IP保护中,看似做到了安全性与灵活性的契合,但该方案并没有在IP保护中考虑PUF的可靠性问题,而是认为PUF是理想模型,忽略了占用较大逻辑资源的模糊提取器;因此该方案的可实现性较差,在实际应用中有待改善。Zhang等[20]使用模糊提取器处理PUF生成的密钥,使之满足应用于IP的需求;但是该方案针对大型FPGA系统,不满足按次付费功能。本文设计的RFSM-PUF授权方案解决了以上存在的问题,其中PUF保证IP核的安全性,RFSM实现IP核的按次付费功能。

表1 IP保护方案的性能对比

注:“√”表示方案能够实现对应功能;“×”表示方案不能实现对应功能。

4 实验与结果分析

将提出的保护机制在LGSyth91基准电路上测试,其中RFSM配置=6、=2、=1、=15进行实验。首先,修改KISS2格式的基准电路[31],将RFSM序列添加到原始IP核中;其次,使用Kiss2v将修改后的KISS2格式的基准电路转换成Verilog格式;最后,使用XC7z020clg484-1实验板在Vivado 18.3上进行综合测试,并对比分析测试结果。

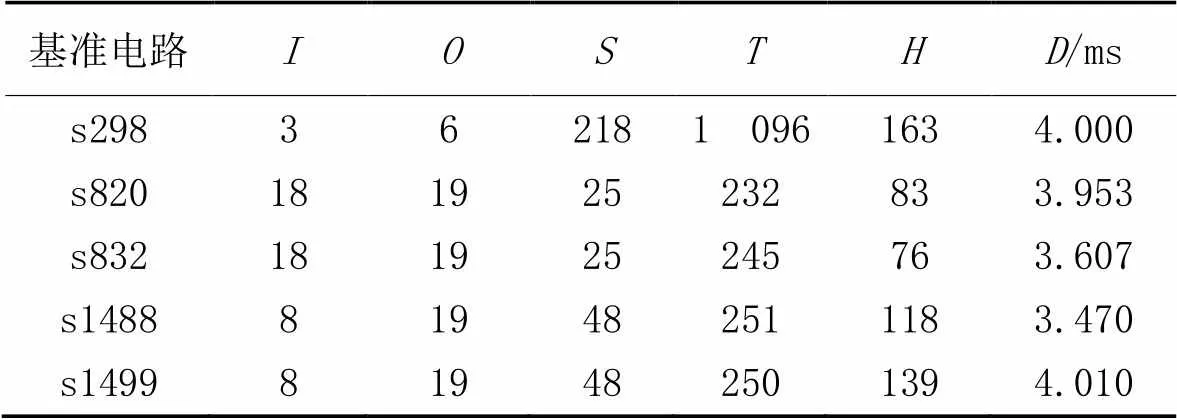

表2给出了基准电路的基本参数,其中、分别表示基准电路的开销(查找表(Look Up Table, LUT))和延时(DELAY)。

不考虑模糊提取器的情况下,文献[21]方案与RFMS-PUF方案在开销与延时效果上相差较小。文献[21]方案在延时性能上略有优势,主要原因是状态机的结构和分析工具的分析策略与本文方案不同;而IP核作为通用电路模块,在运行速率方面要求并不严格,所以两种方案在延时性能上的差别可以接受。

表2 基准电路参数

为了更直观地体现两种方案在实际应用中开销上的区别,需要在方案中增加模糊提取器的开销。一个模糊提取器会占用367个slice[19],而每个slice相当于本文实验中占用LUT数为4。为了进一步论证模糊提取器的真实开销,本文实验在Vivado上实现了模糊提取器模块并进行了开销计算。实验结果表明,模糊提取器可以将PUF响应的可靠性从91.65%提高至99.97%。根据综合报告显示,模糊提取器占用的LUT数为336,因此一个性能优越的模糊提取器占用的逻辑资源巨大,在方案中不能忽略。文献[21]方案将PUF嵌入IP中,这意味着每个IP和都需要配置一个模糊提取器;然而,它提供的资源开销最大是LUT数为262,这充分说明了文献[21]方案是将PUF作为理想模型考虑的,对方案的可实现性造成巨大冲击。

通过对比表3中两种方案的资源开销和延时数据可知,RFSM-PUF方案在保证IP核安全性和实现按次付费功能的同时,大幅降低了安全电路的资源开销。

对比RFSM-PUF方案与文献[21]方案增加模糊提取器后的开销。从表3可以明显看出,RFSM-PUF授权方案增加模糊提取器后,占用平均LUT数为195;而文献[21]方案增加了模糊提取器后,占用的平均LUT数为1 572,比RFSM-PUF方案的平均LUT数增加了1 377,总的资源开销相较于RFSM-PUF方案增加了700%以上。如果应用到更大的设计中,两种授权方案新增开销的占比将变得更小,然而文献[21]方案依然需要在IP内部加入模糊提取器,本文方案与之相比仍具有更低的开销。

综上所述,首先,在实用性方面,文献[21]方案未考虑PUF电路可靠性问题和模糊提取器开销。该方案将PUF作为理想模型,在实际应用中缺乏可行性。其次,通过表2~3可以看出,RFSM-PUF方案引入的硬件开销远低于文献[21]方案,并且在延时与安全性指标中均表现良好,可以应用于IP保护。

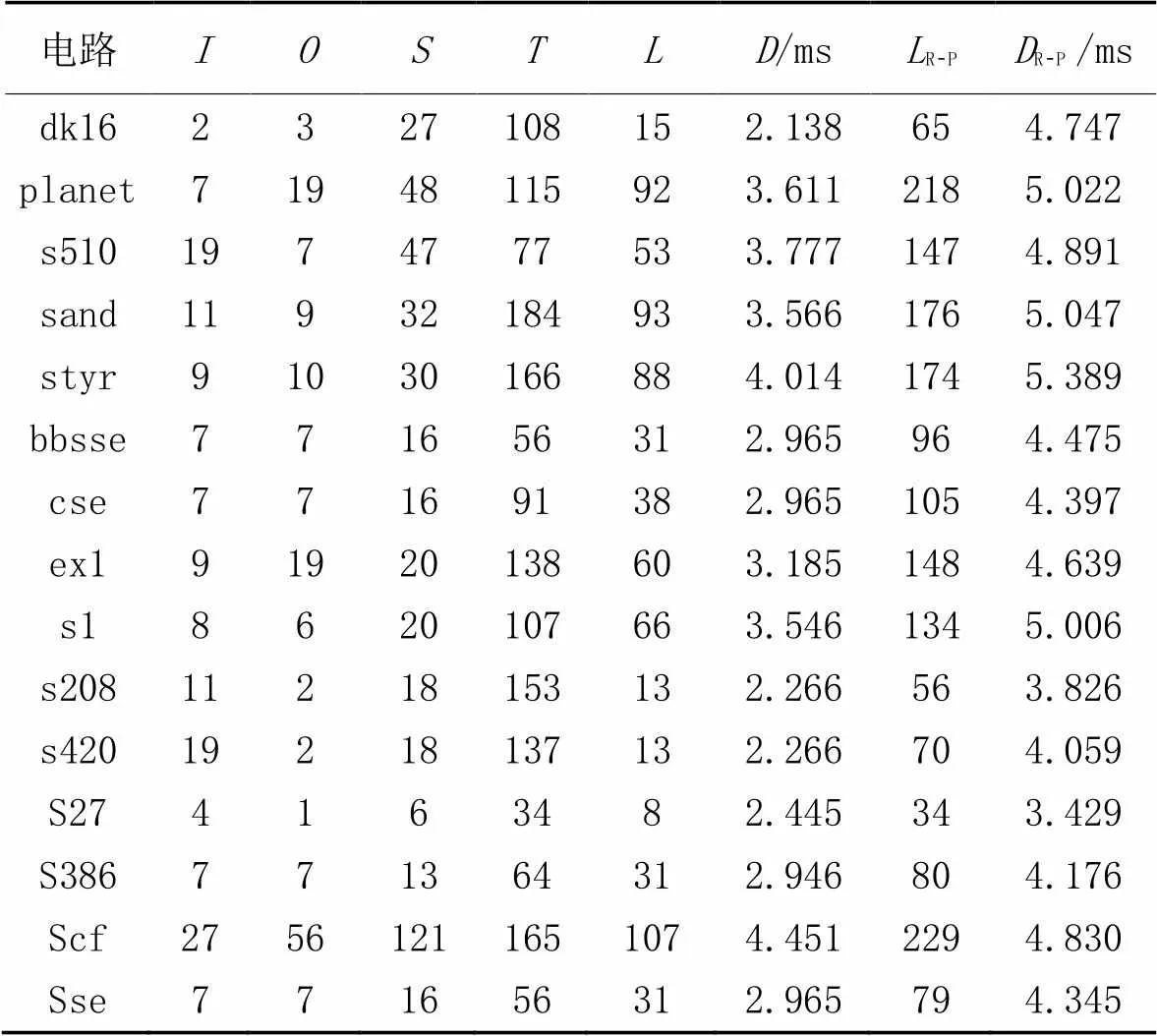

为了进一步验证RFSM-PUF安全电路在IP保护中的通用性,表4给出了15个基准电路上的拓展实验结果。从表4可以看出,RFSM-PUF方案在不同的基准电路上均具有很高的适用性,对基准电路带来的附加开销和延时在可以接受的范围之内。以sand基准电路为例,加入RFSM-PUF安全电路后的开销LUT数与延时分别增加了83和1.481 ms,表明了RFSM-PUF授权方案的优越性。

表3 不同基准电路上不同方案的实验结果对比

表4 本文方案在不同基准电路上的实验结果

5 结语

本文提出一种基于RFSM-PUF的低成本按次付费方案,可以解决当前按次付费方案存在的开销与实现性之间的权衡问题。在IP保护中,RFSM作为按次付费的安全模块,引入的PUF用于生成唯一响应。为了在IP中混淆RFSM和原始FSM,本文从RFSM中随机选择若干状态,并将它们连接到原始IP中FSM的不同状态。RFSM的正确路径是保密的,以保证license的安全,只有IP设计者可以根据RFSM和PUF响应计算出license。利用RFSM的重构特性实现IP核的按次付费功能,此外,本文设计了一个三方交互协议与所提电路契合,协议中的三方在原有交互的基础上对RFSM-PUF方案更加适用。最后在LGSyth91 基准电路上通过实验验证RFSM-PUF授权方案,实验结果表明,RFSM-PUF授权方案相较于其他按次付费方案占用更少的逻辑资源,削弱了模糊提取器的影响,更具可实现性。

[1] GUNEYSU T, MOLLER B, PAAR C. Dynamic intellectual property protection for reconfigurable devices[C]// Proceedings of the 2007 International Conference on Field-programmable Technology. Piscataway: IEEE, 2007:169-176.

[2] BOSSUET L, GOGNIAT G, BURLESON W. Dynamically configurable security for SRAM FPGA bitstreams[J]. International Journal of Embedded Systems, 2006, 2(1/2): 73-85.

[3] SISEJKOVIC D, MERCHANT F, REIMANN L M, et al. Deceptive logic locking for hardware integrity protection against machine learning attacks[J]. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2022, 41(6): 1716-1729.

[4] 张伟,冯建华. IP保护方法研究进展[J]. 微纳电子与智能制造, 2020, 2(1):95-101.(ZHANG W, FENG J H. Research progress on IP protection techniques[J]. Micro/nano Electronics and Intelligent Manufacturing, 2020, 2(1): 95-101.)

[5] TORUNOGLU I, CHARBON E. Watermarking-based copyright protection of sequential functions[J]. IEEE Journal Solid-State Circuits, 2000, 35(3): 434-440.

[6] KEAN T. Cryptographic rights management of FPGA intellectual property cores[C]// Proceedings of the ACM/SIGDA 10th International Symposium on Field-Programmable Gate Arrays. New York: ACM, 2002:113-118.

[7] ALKABANI Y, KOUSHANFAR F. Active control and digital rights management of integrated circuit IP cores[C]// Proceedings of the 2008 International Conference on Compilers, Architecture, and Synthesis for Embedded Systems. New York: ACM, 2008: 227-234.

[8] SUBRAMANYAN P, RAY S, MALIK S. Evaluating the security of logic encryption algorithms[C]// Proceedings of the 2015 IEEE International Symposium on Hardware Oriented Security and Trust. Piscataway: IEEE, 2015: 137-143.

[9] YU M D, DEVADAS S. Secure and robust error correction for physical unclonable functions[J]. IEEE Design and Test of Computers, 2010, 27(1): 48-65.

[10] DARJI A D, LAD T C, MERCHANT S N, et al. Watermarking hardware based on wavelet coefficients quantization method[J]. Circuits, Systems, Signal Processing, 2013, 32(6): 2559-2579.

[11] FYRBIAK M, WALLAT S, DÉCHELOTTE J, et al. On the difficulty of FSM-based hardware obfuscation[J]. IACR Transactions on Cryptographic Hardware and Embedded Systems, 2018, 2018(3): 293-330.

[12] KOUSHANFAR F, QU G. Hardware metering[C]// Proceedings of the 38th Design Automation Conference. Piscataway: IEEE, 2001:490-493.

[13] CUI A, CHANG C H, TAHAR S, et al. A robust FSM watermarking scheme for IP protection of sequential circuit design[J]. IEEE Transitions on Computer-Aided Design of Integrated Circuits and System, 2011, 30(5): 678-690.

[14] TORRANCE R, JAMES D. The state-of-the-art in IC reverse engineering[C]// Proceedings of the 2009 International Workshop on Cryptographic Hardware and Embedded Systems, LNCS 5747. Berlin: Springer, 2009: 363-381.

[15] MAES R, SCHELLEKENS D, VERBAUWHEDE I. A pay-per-use licensing scheme for hardware IP cores in recent SRAM-based FPGAs[J]. IEEE Transitions on Information Forensics and Security, 2012, 7(1): 98-108.

[16] ZHANG J, LIN Y, LYU Y, et al. FPGA IP protection by binding finite state machine to physical unclonable function[C]// Proceedings of the 23rd International Conference on Field Programmable Logic and Applications. Piscataway: IEEE, 2013: 1-4.

[17] KUMAR S S, GUAJARDO J, MAES R, et al. Extended abstract: the butterfly PUF: protecting IP on every FPGA[C]// Proceedings of the 2008 IEEE International Workshop on Hardware-Oriented Security and Trust. Piscataway: IEEE, 2008: 67-70.

[18] 潘畲稣,张继军,张钊锋. 一种无熵泄露的模糊提取器改进结构[J]. 电子技术应用, 2019, 45(10):96-99.(PAN S S, ZHANG J J, ZHANG Z F. An improved structure of fuzzy extractor without entropy leakage[J]. Application of Electronic Technique, 2019, 45(10): 96-99.)

[19] BÖSCH C, GUAJARDO J, SADEGHI A R, et al. Efficient helper data key extractor on FPGAs[C]// Proceedings of the 2008 International Workshop on Cryptographic Hardware and Embedded Systems, LNCS 5154. Berlin: Springer, 2008: 181-197.

[20] ZHANG J L, LIN Y, LYU Y, et al. A PUF-FSM binding scheme for FPGA IP protection and pay-per-device licensing[J]. IEEE Transitions on Information Forensics and Security, 2015, 10(6): 1137-1150.

[21] SUN P, CUI A. A new pay-per-use scheme for the protection of FPGA IP[C]// Proceedings of the 2019 IEEE International Symposium on Circuits and Systems. Piscataway: IEEE, 2019: 1-5.

[22] 刘胜利,温云华. 模糊提取器及其应用[J]. 信息安全与通信保密, 2019(2):54-63.(LIU S L, WEN Y H. Fuzzy extractor and its application[J]. Information Security and Communications Privacy, 2019(2): 54-63.)

[23] KOSTER M, TEICH J. (Self-) reconfigurable finite state machines: theory and implementation[C]// Proceedings of the 2002 Automation and Test in Europe Conference and Exhibition. Piscataway: IEEE, 2002: 559-566.

[24] LI L, NI S, ORAILOGLU A. JANUS: boosting logic obfuscation scope through reconfigurable FSM synthesis[C]// Proceedings of the 2021 IEEE International Symposium on Hardware Oriented Security and Trust. Piscataway: IEEE, 2021: 292-303.

[25] SAEED S M, ZULEHNER A, WILLE R, et al. Reversible circuits: IC/IP piracy attacks and countermeasures[J]. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2019, 27(11): 2523-2535.

[26] GUAJARDO J, KUMAR S S, SCHRIJEN G J, et al. FPGA intrinsic PUFs and their use for IP protection[C]// Proceedings of the 2007 International Workshop on Cryptographic Hardware and Embedded Systems, LNCS 4727. Berlin: Springer, 2007: 63-80.

[27] CHAKRABORTY R S , BHUNIA S. RTL hardware IP protection using key-based control and data flow obfuscation[C]// Proceedings of the 23rd International Conference on VLSI Design. Piscataway: IEEE, 2010: 405-410.

[28] MUTTAKI M R, MOHAMMADIVOJDAN R, TEHRANIPOOR M, et al. HLock: locking IPs at the high-level language[C]// Proceedings of the 58th ACM/IEEE Design Automation Conference. Piscataway: IEEE, 2021: 79-84.

[29] BHANDARI J, THALAKKATTU MOOSA A K, TAN B, et al. Exploring eFPGA-based redaction for IP protection[C]// Proceedings of the 2021 IEEE/ACM International Conference on Computer-Aided Design. Piscataway: IEEE, 2021: 1-9.

[30] DHABU S S, ZHENG Y, LIU W, et al. Active IC metering of digital signal processing subsystem with two-tier activation for secure split test[C]// Proceedings of the 2018 IEEE International Symposium on Circuits and Systems. Piscataway: IEEE, 2018: 1-5.

[31] PRUTEANU C, HABA C G., a finite state machine generation tool[C/OL]// Proceedings of the 9th International Conference on Development and Application Systems [2022-08-10].http://www.dasconference.ro/papers/2008/D8.pdf.

Low-cost pay-per-use licensing scheme for FPGA intellectual property protection

SONG Binwei, WANG Yao*

(,,450001,)

The pay-per-use licensing of the Intellectual Property (IP) core enables the system designer to purchase IP at low price according to the actual situation, and has become a major method of IP licensing. To meet the pay-per-use demand of IP core, based on Reconfigurable Finite State Machine (RFSM) and Physical Unclonable Function (PUF), a new IP licensing scheme RFSM-PUF was proposed for Field Programmable Gate Array (FPGA) IP. Aiming at the problem that the protocols of the IP protection schemes of different manufacturers cannot be used universally, an IP protection authentication protocol for the proposed scheme was proposed to ensure the confidentiality and flexibility of IP authentication. Firstly, RFSM was embedded in the Original Finite State Machine (OFSM) in the IP, and in this way, the IP was only unlocked by the IP core designer. Then, the challenges were input into the PUF circuit to produce responses. Finally, the cipher consisting of the license and PUF responses was input into the RFSM to unlock the IP. The security analysis results show that the proposed scheme meets various security indicators. RFSM-PUF scheme was tested on the LGSyth91 benchmark circuits. Experimental results show that on the premise of meeting various safety indicators, the proposed scheme reduces 1 377 Look-Up Tables (LUT) averagely at every IP core compared to the PUF based pay-per-use licensing scheme, so that the hardware overhead is significantly reduced.

Field Programmable Gate Array (FPGA); Intellectual Property (IP); Reconfigurable Finite State Machine (RFSM); Physical Unclonable Function (PUF); LGSyth91 benchmark

This work is partially supported by National Key Research and Development Program of China (SQ2020YFF0404465).

SONG Binwei, born in 1997, M. S. candidate. His research interests include on-chip and Field Programmable Gate Array (FPGA) hardware security.

WANG Yao, born in 1983, Ph. D., associate professor. His research interests include digital-analog hybrid integrated circuit design, on‑chip and FPGA hardware security, radio frequency identification technology.

1001-9081(2023)10-3142-07

10.11772/j.issn.1001-9081.2022101506

2022⁃10⁃12;

2022⁃12⁃26;

国家重点研发计划项目(SQ2020YFF0404465)。

宋斌威(1997—),男,河南周口人,硕士研究生,主要研究方向:片上与现场可编程门阵列(FPGA)硬件安全; 王耀(1983—),男,河南南阳人,副教授,博士生导师,博士,主要研究方向:数模混合集成电路设计、片上与FPGA硬件安全、射频识别技术。

TP391;TN919

A

2022⁃12⁃27。