毫米波雷达数据采集系统设计

2023-10-19孙黄悦

孙黄悦, 于 映

(南京邮电大学 集成电路科学与工程学院, 江苏 南京 210023)

0 引 言

毫米波通信具有波束窄、尺寸小、探测能力强等优点[1],已成为当前移动通信研究的热点。早期毫米波雷达主要应用于军事领域,近年来随着雷达技术的发展,毫米波雷达传感器开始应用于汽车电子、无人机、智能交通等民用领域[2-3]。毫米波雷达具有精度高、抗干扰能力强、全天候全天时、高分辨率、多目标等优点。2017 年5 月16 日,美国德州仪器(TI)全球发布了AWR和IWR 两个系列的毫米波雷达传感器,面向汽车领域和工业领域。 本文使用TI 公司的毫米波雷达AWR1243boost 开发板作为系统的射频前端传感器。AWR1243 器件是一款能够在76~81 GHz 频带内运行的集成式单芯片FMCW 收发器,主要集成了小数分频PLL、发射器、接收器、基带和ADC,具有4 GHz 的可用带宽、3 个发射通道和4 个接收通道。AWR1243 评估板上还集成了77 GHz 毫米波MIMO 天线、频率为40 MHz的时钟晶振、与外部处理器进行控制连接的SPI 接口以及与外部处理器进行数据连接的MIPI D-PHY 和CSI2 V1.1 接 口[4]。AWR1243 芯片的架构如图1 所 示。

针对毫米波雷达射频前端的高速数据,毫米波雷达采集数据系统应具有高数据采集速率、大数据容量以及较高的可移植性等特点。现场可编程门阵列(Field Programmable Gate Array, FPGA)具有并行运算能力强、实时性好等优点,可以满足毫米波雷达射频前端高速数据的需求。本文提出一种以FPGA、USB 为数据传输媒介的适用于毫米波雷达的数据采集系统[2],介绍了FPGA 内部各功能模块的划分和基本的数据通路。

1 整体系统设计

基于FPGA 的毫米波雷达数据采集系统主要由射频前端模块、FPGA 数据采集卡模块以及上位机模块[1,4-5]三部分组成,系统架构如图2 所示。AWR1243boost评估板的接收天线接收毫米波回波信号,并经过混频器、滤波器、ADC 模块转换为高频数字信号。AWR1243boost 提供了CSI2 和LVDS 两种接口输出ADC 原始数据[4]。在该系统中,FPGA 数据采集卡通过配置模块,选择使用LVDS 格式的ADC 原始数据。FPGA 数据采集卡采集射频前端的原始数据,并对其进行降速、位宽转换以及缓存处理。缓存后的数据通过USB 模块转换成符合USB协议的数据格式,再发送给上位机,上位机解析数据并进行处理。在该系统中,FPGA 选用Xilinx 公司的Artix-7 系列XC7A35T 芯片,该芯片内部有33 280 个逻辑单元、5 200个查找表以及41 600 个触发器。DDR3 芯片选用Micron(美光)公司2 Gbit 芯片,型号为MT41J28M6HA-125。DDR 的总线宽度为16 bit,最高运行时钟频率为400 MHz(数据速率为800 Mb/s)。 USB 模 块 选 用FTDIChip 公 司 的FT232H单通道高速USB芯片,其最高通信速率可达到480 Mb/s,并且支持不同的数据通信模式(FIFO、I2C、SPI),在本文系统中,采用FIFO模式进行通信。

图2 数据采集系统架构

2 系统子模块设计

2.1 射频前端配置模块

AWR1243 是一种集成调频连续波(FMCW)收发器,外部处理器可通过SPI 接口控制雷达内各个参数,如FMCW 调频斜率、采样率、Chirp 参数配置、接口通道、数据格式等[4,6]。射频前端配置模块主要分为4 个子模块,分别为40 MHz 时钟分频模块、片选使能模块、FMCW 毫米波配置模块以及配置发送控制模块,如图3 所示。

图3 射频前端配置模块

图3 中:clk_40M 模块是分频模块,主要产生40 MHz 频率时钟;cs_generate 模块是产生片选使能模块;fmcw_config 模块主要负责配置射频前端各个参数的具体数值;awr_config_send_fsm 主要负责参数发送模块的状态机控制。参数发送状态转移图如图4 所示。

图4 参数发送状态转移图

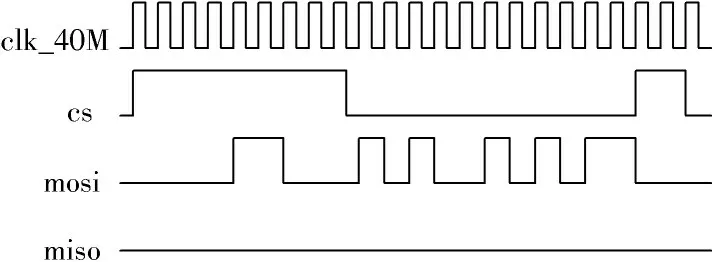

图5 所示为SPI 时序图,其各个参数均按照此时序依次发送给AWR1243boost 的寄存器,当检测到cs 有效下降沿时,间隔两个时钟周期数据有效,并且每2 B,cs使能有效一次。

图5 SPI 时序图

2.2 AWR1243boost interface 模块

AWR1243boost interface 模块主要负责接收毫米波雷达射频前端数据,毫米波雷达产生4 路串行低电压差分(LVDS)数据[7],该模块架构如图6 所示。针对差分数据格式,此模块中采用双异步FIFO 接收数据[8]。

图6 AWR1243boost interface 架构

将高电平有效的4 组接口串行数据连接高电平有效异步FIFO,将低电平有效的串行数据连接低电平有效异步FIFO,即输入数据设置为rdata_p[3∶0]和rdata_n[3∶0],并且将差分时钟分别连接2 个异步FIFO 的输入时钟,此差分时钟频率为150 MHz。异步FIFO 的读时钟则由系统架构中的时钟模块产生,时钟 频率为100 MHz。

2.3 DDR3 控制模块

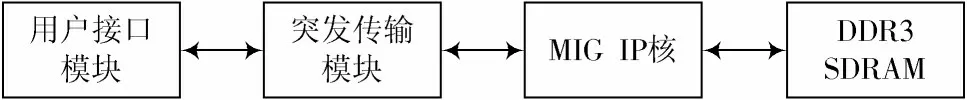

DDR3 控制模块为系统的数据缓存模块[9-10]。射频前端数据单通道输入速率为150 Mb/s;USB 模块的接口速率最大可达480 Mb/s,该数据线具有一定的空闲期,需要将数据进行缓存,然后再发送给上位机,就可以最大限度地解决传输速度不匹配的问题。DDR3 控制模块的各参数可根据Xilinx 提供的MIG IP 核进行配置。图7 所示为DDR3 interface control 模块架构框图。

图7 DDR3 interface control 模块架构

用户接口模块接收通道合并后的数据,并设置写突发长度(wr_burst_len)、写突发数据(wr_burst_data)、写突发地址(wr_burst_addr)以及写突发请求信号(wr_burst_req)等。突发传输模块解析以上信号,并生成 app_rdy、app_en、app_addr、app_wdf_data 以 及app_cmd 信号作为IP 核的输入,用于和DDR3 SDRAM存储模块交互。

在写传输时,突发传输模块准备信号app_rdy 和使能信号app_en 都应保持高使能,并确保写操作命令app_cmd 和地址信号app_addr 有效。当app_wdf_rdy 信号和app_wdf_wren 信号都为高时,此时写入数据app_wdf_data 有效。读传输时,需要app_rdy、app_en、app_addr 及app_cmd 信号同时有效时数据才有效,且数据输出会有延迟。

2.4 USB interface control 模块

USB interface control 模块主要作为FT232H 驱动芯片的接口模块[8,11-13]。使用FT_Prog 软件可将FT232H 配置为同步FIFO 模式[11]。因此本文进行该模块设计时,同样需要设计一个同步FIFO 模块,用于和FT232H 中的同步FIFO 模块进行数据交互[14]。USB interface control模块框图如图8 所示。

图8 USB interface control 模块框图

3 系统测试

系统平台搭建完成后,进行系统测试和分析。测试过程主要包括 FPGA程序烧录、功能仿真、收发数据对比。

3.1 仿真结果分析

本文系统在Xilinx 公司提供的Vivado 软件开发环境下进行FPGA 程序的编写、功能仿真、综合优化、综合后仿真、布局布线以及板级仿真和验证。在板级仿真和验 证 时,加 入ILA(Intergrated Logic Analyzer)核,即Vivado 的集成逻辑分析仪。在系统架构内加入ILA 模块,ILA 模块通过多个探针(Probe)采集需要观察的信号。首先,将FPGA 程序进行编译综合,生成bit 流文件;再使用FPGA 下载器连接计算机和FPGA,将bit 流文件烧录到FPGA 中;下载完成后ILA 模块自动打开,采集需要观察的信号,判断信号是否正确并进行调试。

在系统架构的顶层模块中加入ILA 核,主要检测射频前端四路差分数据与AWR1243boost interface 模块中异步FIFO 的写入数据。 图9 所示为ILA 抓取AWR1243boost interface 模块异步FIFO 的写入数据。

图9 异步FIFO 写入数据

图10 所示为射频前端配置模块的片选信号波形,其中每2 Byte,信号使能有效一次。

图10 AWR1243boost 四路串行数据

3.2 数据对比

数据从两方面进行接收:一方面,使用TI 公司的毫米波雷达配置软件(UniFlash)对AWR1243boost 雷达板卡烧录驱动程序[15],在PC 端使用串口助手捕捉原始的雷达回传数据(bin 文件);另一方面,射频前端数据经过系统,由PC 端的Matlab 接收并收集。导出收集的数据并与原始的雷达回传数据对比,发现导出的数据与原始的雷达回传数据一致,没有出现数据丢失的情况。图11 所示为原始的雷达回传数据的部分展示,使用Binary Viewer软件打开,左侧为数据地址,右侧为数据。

图11 原始数据(部分)

图12 所示为Matlab 收集的数据,Matlab 将接收到的原始数据收集到文本文件中。通过对比可以发现,其原始数据和经过系统缓存后的数据一致。

图12 Matlab 收集的数据

4 结 论

本文提出一种基于FPGA 的毫米波雷达数据采集系统,该系统通过FPGA 向射频前端发送参数数据,并通过FPGA 接收回传的雷达原始数据,可为后续的算法实现提供一套稳定的数据采集系统。

注:本文通讯作者为于映。